#### Description

NSI6602B-DSWR is a family of high reliability isolated dual channel gate driver ICs which can be designed to drive power transistor up to 2MHz switching frequency. Each output could source 4A and sink 6A peak current with fast 25ns propagation delay and 5ns maximum delay matching.

The NSI6602B-DSWR provides 5000Vrms isolation in SOW-16 package. System robustness is supported by 150kV/us typical common-mode transient immunity(CMTI).

The driver operates with a maximum supply voltage of 30V, while the input-side accepts from 2.7V to 5V supplyvoltage. Under voltage lock-out (UVLO) protection issupported by all the power supply voltage pins.

#### Safety Regulatory Approvals

- UL recognition(Planned):

5000Vrms for 1 minute per UL1577

- DIN EN IEC 60747-17(VDE 0884-17):2021-10

- CSA component notice 5A

#### **Applications**

- MOSFET,IGBT,SiC and GaN gate driver

- Isolated DC-DC and AC-to-DC power supplies in server,telecom,and industry

- · Motor drives and EV charging

- UPS and battery chargers

- DC-to-AC solar inverters

#### **Features**

- Isolated dual channel driver

- Input side supply voltage: 2.7V to 5.5V

- Driver side supply voltage: up to 30V with UVLO

- 4A peak source and 6A peak sink output

- High CMTI: ±200kV/us typical

- 25ns typical propagation delay

- 5ns maximum delay matching

- 6ns maximum pulse width distortion

- Programmable deadtime

- Accepts minimum input pulse width 20ns

- Operation temperature:-40°C~105°C

- RoHS & REACH Qualified

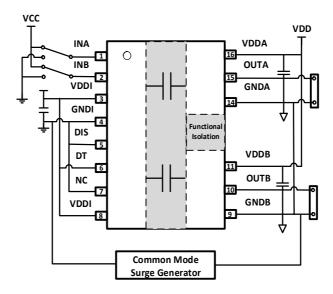

#### **Functional Block Diagram**

## **Product Family**

| Part Number   | Peak Current | UVLO      | DT | DIS | Package |

|---------------|--------------|-----------|----|-----|---------|

| NSI6602B-DSWR | +4.0A/-6.0A  | 8.5V/8.0V | Υ  | Y   | SOW-16  |

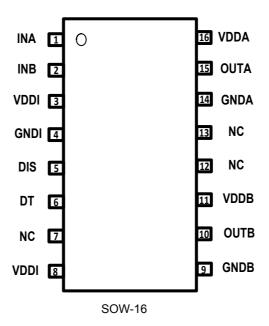

## **Pin Configuration**

## **Pin Description**

| No.     | Symbol  | Description                                                                                          |

|---------|---------|------------------------------------------------------------------------------------------------------|

| 1       | INA     | TTL/CMOS compatible input signal for channel A with internal pull down to GND.                       |

| 2       | INB     | TTL/CMOS compatible input signal for channel B with internal pull down to GND.                       |

| 3,8     | VDDI    | Input side supply voltage.                                                                           |

| 4       | GND     | Input side ground reference.                                                                         |

| 5       | DISABLE | Disable the isolator inputs and driver outputs if asserted high, enable if asserted low or left open |

| 6       | DT      | Programmable deadtime control.                                                                       |

| 9       | GNDB    | Ground for output channel B                                                                          |

| 10      | OUTB    | Output gate driver for channel B                                                                     |

| 11      | VDDB    | Supply voltage for channel B                                                                         |

| 14      | GNDA    | Ground for output channel A                                                                          |

| 15      | OUTA    | Output gate driver for channel A                                                                     |

| 16      | VDDA    | Supply voltage for channel A                                                                         |

| 7,12,13 | NC      | Not connected                                                                                        |

## **Specifications**

#### **Absolute Maximum Ratings**

| Parameter                                | Symbol                     | Min.  | Max. | Unit |

|------------------------------------------|----------------------------|-------|------|------|

| Input Side Supply Voltage                | VDDI to GNDI               | -0.3  | 6    |      |

| Input Signal Voltage                     | VIA, VIB, VDIS             | -0.3  | 6    |      |

| Output Side Supply<br>Voltage            | VDDA to GNDA, VDDB to GNDB | -0.3  | 30   |      |

| Channel A to Channel B Isolation Voltage | VISOAB                     | -     | 1500 | V    |

| Electrostatic discharge                  | HBM                        | -4000 | 4000 |      |

|                                          | CDM                        | -1500 | 1500 |      |

| Storage Temperature                      | Ts                         | -65   | +150 | °C   |

| Junction Temperature                     | Tj                         | -40   | +150 | °C   |

Note: VDDI, VIA, VIB, VDIS are reference to GNDI; VDDA, VOUTA is referenced to GNDA; VDDB, VOUTB is referenced to GNDB.

## **Recommended Operating Conditions**

| Parameter                 | Symbol                     | Min. | Max.       | Unit |

|---------------------------|----------------------------|------|------------|------|

| Input Side Supply Voltage | VDDI to GNDI               | 3.0  | 5.5        |      |

| Input Signal Voltage      | VIA, VIB, VDIS             | 3.0  | 5.5        |      |

| Output Supply Voltage     | VDDA to GNDA, VDDB to GNDB | 7    | 20         | V    |

| Input Signal Voltage      | Ina,Inb,Dis,DT             | 0    | $V_{VDDI}$ |      |

| Junction Temperature      | Tj                         | -40  | 150        |      |

| Operating Temperature     | TA                         | -40  | 125        | °C   |

Note:Operation beyond recommended operating conditions may cause long term reliability issue or even damage to the IC.

## **Electrical Characteristics (DC)**

VDDI=3.3V or 5V, VDDA=VDDB=12V for H8233A/B, VDDA=VDDB=15V for H8233C,

Ta=-40~125°C. Unless otherwise noted, typical values are tested at Ta=25°C.

| Parameter                                   | Symbol                                                                                     | Min  | Тур  | Max  | Unit | Test Condition                                                       |

|---------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|----------------------------------------------------------------------|

| Current leakage characteristic              | S                                                                                          | •    |      | •    | •    |                                                                      |

| VDDI Quiescent Current                      | $I_{VDDIQ}$                                                                                | -    | 0.4  | 2    | mA   | INA=0, INB=0                                                         |

| VDDI Operating Current                      | $I_{VDDI}$                                                                                 | -    | 11   |      | mA   | Input frequency 500kHz                                               |

| VDDA/B Quiescent Current, per Channel       | I <sub>VDDAQ,</sub><br>I <sub>VDDBQ</sub>                                                  | -    | 1.5  | 2.5  | mA   | INA=0,INB=0, VDDx=12V<br>for 6V, 8V UVLO;<br>VDDx=15V for 13V UVLO   |

| VDDA/B Operation Current, per Channel       | I <sub>VDDA</sub> , I <sub>VDDB</sub>                                                      | -    | 2.6  | -    | mA   | 100pF, 500KHz, VDDx=12V<br>for 6V, 8V UVLO; VDDx=15V<br>for 13V UVLO |

| UVLO                                        |                                                                                            | ı    |      | I    |      | 101 104 0450                                                         |

| VDDI UVLO Rising<br>Threshold               | $V_{VDDI\_ON}$                                                                             | 2.35 | 2.55 | 2.75 |      |                                                                      |

| VDDI UVLO Falling<br>Threshold              | V <sub>VDDI_OFF</sub>                                                                      | 2.15 | 2.35 | 2.55 |      |                                                                      |

| VDDI UVLO Hysteresis                        | V <sub>VDDI_HYS</sub>                                                                      | -    | 0.2  | -    | V    |                                                                      |

| VDDA/B UVLO Rising Threshold                | V <sub>VDDO_ON</sub>                                                                       | 7.5  | 8.0  | 8.5  | ľ    |                                                                      |

| VDDA/B UVLO Falling<br>Threshold            | V <sub>VDDO_</sub> OFF                                                                     | 7.0  | 7.5  | 8.0  |      |                                                                      |

| VDDA/B UVLO Hysteresis                      | V <sub>VDDO HYS</sub>                                                                      | -    | 0.5  | -    |      |                                                                      |

| Input Side Characteristic                   |                                                                                            |      |      |      |      |                                                                      |

| Input Pin Pull Down<br>Resistance, INA, INB | R <sub>INA_PD,</sub><br>R <sub>INB_PD,</sub>                                               | -    | 100  | -    | kΩ   |                                                                      |

| Input Pin Pull Down<br>Resistance, DIS(EN)  | R <sub>DIS_PD</sub>                                                                        | -    | 100  | -    | kΩ   |                                                                      |

| Logic High Input Threshold                  | V <sub>INA_H</sub> ,<br>V <sub>INB_H</sub> ,<br>V <sub>DIS H</sub>                         | -    | 1.45 | 2    |      |                                                                      |

| Logic Low Input Threshold                   | V <sub>INA_L</sub> ,<br>V <sub>INB_L</sub> ,<br>V <sub>DIS_L</sub>                         | 0.8  | 1.3  | -    | V    |                                                                      |

| Input Hysteresis                            | V <sub>INA_HYS</sub> , V <sub>INB_HYS</sub> , V <sub>DIS HYS</sub>                         | -    | 0.15 | -    |      |                                                                      |

| Output Side Characteristic                  |                                                                                            |      |      |      |      |                                                                      |

| Logic High Output Voltage                   | V <sub>VDDA</sub> -<br>V <sub>OUTA</sub> H,<br>V <sub>VDDB</sub> -<br>V <sub>OUTB</sub> H, | -    | 0.34 | -    | V    | I <sub>out</sub> =100mA                                              |

| Logic Low Output Voltage                    | VOUTA_L, VOUTB_L                                                                           | -    | 55   | -    | mV   | I <sub>out</sub> =100mA                                              |

| Output Source Resistance                    | Routa_h,<br>Routb_h                                                                        | -    | 3.4  | -    | Ω    | I <sub>out</sub> =100mA                                              |

| Output Sink Resistance                      | ROUTA_L,<br>ROUTB L                                                                        | -    | 0.55 | -    | Ω    | I <sub>out</sub> =100mA                                              |

| Peak Output Source Current                  | Iouta+,                                                                                    | -    | +4.0 | -    | Α    | VDDx=15V                                                             |

| Peak Output Sink Current                    | IOUTA-,                                                                                    | -    | -6.0 | -    | Α    | VDDx=15V                                                             |

High Reliability Isolated Dual-Channel Gate Driver

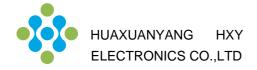

## **Switching Characteristics (AC)**

VDDI=3.3V or 5V, VDDA=VDDB=12V for H8233A/B, VDDA=VDDB=15V for H8233C, Ta=25°C.

| Parameter                                                               | Symbol                                | Min. | Тур. | Max. | Unit  | Test Condition                                    |

|-------------------------------------------------------------------------|---------------------------------------|------|------|------|-------|---------------------------------------------------|

| Turn On Propagation Delay Time                                          | t <sub>PDLH</sub>                     | 10   | 25   | 35   |       | C <sub>OUTA/B</sub> =1 nF                         |

| Turn Off Propagation Delay Time                                         | t <sub>PDHL</sub>                     | 10   | 25   | 35   |       | C <sub>OUTA/B</sub> =1 nF                         |

| Output Rise Time (20% to 80%)                                           | $t_R$                                 | -    | 7    | 16   |       | C <sub>OUTA/B</sub> =1.8nF,                       |

|                                                                         |                                       |      | _    |      |       | verified by design                                |

| Output Fall Time (90% to 10%)                                           | t <sub>F</sub>                        | -    | 6    | 12   |       | C <sub>OUTA/B</sub> =1.8nF,<br>verified by design |

| Minimum Pulse Width                                                     | $t_{\sf PWmin}$                       | -    | 10   | 15   | ns    | C <sub>OUTA/B</sub> =0 pF                         |

| Pulse Width Distortion  tpdhl-tpdh                                      | t <sub>PWD</sub>                      | -    | -    | 6    |       |                                                   |

| Channel to Channel Delay Matching                                       | t <sub>DMLH</sub> , t <sub>DMHL</sub> | -    |      | 5    |       |                                                   |

| Programmed Deadtime                                                     | t <sub>DT</sub>                       | 160  | 200  | 240  |       | $t_{DT}$ (ns)=10*R(KΩ);<br>Test for R=20KΩ        |

| Shutdown Time from Disable True                                         | t <sub>DIS</sub>                      | -    | -    | 40   |       |                                                   |

| Recovery Time from Disable False                                        | T <sub>EN</sub>                       | -    | -    | 40   |       |                                                   |

| VDDI Power-up Time Delay<br>(Time from VDDI=VDDI_ON to<br>OUTA/B=INA/B) | t <sub>start_</sub> VDDI              | -    | 8.5  | 15   | us    | INA or INB tied<br>to VDDI                        |

| VDDA/B Power-up Time Delay                                              | t <sub>start_VDDA,</sub>              | -    | 18   | 30   | us    | INA or INB tied to                                |

| (Time from VDDA/B=2V to OUTA/B=INA/B)                                   | <b>t</b> start_VDDB                   |      |      |      |       | VDDI C <sub>OUTA</sub> /<br>B=1.8nF               |

| High Level Common Mode Transient Immunity                               | CMTI <sub>H</sub>                     | 100  | 150  | -    | kV/us | B- 1.0111                                         |

| Low Level Common Mode Transient Immunity                                | CMTI∟                                 | 100  | 150  | -    | kV/us |                                                   |

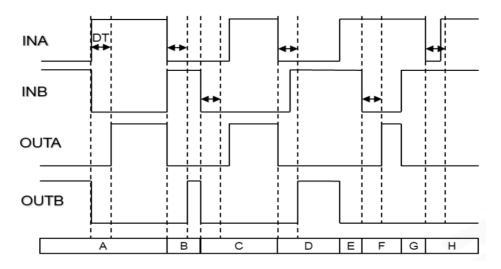

Propagation Delay and Delay Match Time

Input and Output Logic with Programmed Deadtime

**CMTI Test Circuit**

High Reliability Isolated Dual-Channel Gate Driver

#### **Feature Description**

NSI6602B-DSWR is a flexible dual channel isolated gate driver that can drive IGBTs and MOSFETs. It has 4.0A peak output current capability with maxim output driver supply voltage of 30V. It has many features that allow it to integrate well with control circuitry and protect the gates it drives such as: resistor programmable dead time control, an DIS pin, and under voltage lock out (UVLO) for both input and output voltages.

#### **Under Voltage Lockout**

The has under voltage lock out (UVLO) protection feature on each driver power supply voltage between the VDDA (VDDB) and GNDA (GNDB) pins. When the VDDx voltage is lower than VUVLO\_VDDX\_R, during device start up or lower than VUVLO\_VDDX\_F, after start up, the VDDA (VDDB) UVLO feature holds the driver output low,regardless of the status of the input pins. A hysteresis on the UVLO feature prevents glitch when there is noise from the power supply. The also monitors the input power supply and there is an internal under voltage lock out protection feature on the VDDI. The driver outputs (OUTA and OUTB) are hold low when the voltage on the VDDI is lower than VUVLO\_VDDI\_R during start up or lower than VUVLO\_VDDI\_F after start up. There is a hysteresis on the VDDI UVLO feature to prevent glitch due the noise on the VDDI power supply.

#### **Disable Input Function**

When the DIS is pulled high, the OUTA and OUTB are pulled low regardless of the states of INA and INB. Whenthe DIS pin is pulled low, the VOA and VOB are allowed for normal operation and controlled by the INA and INB. The DIS input has no effect if VDDI is below its UVLO threshold and OUTA, OUTB remain low. There is an internal pull down resistor on the DIS pin.

#### **Control Input and Output Logic**

The INA and INB input controls the corresponding output channel, OUTA and OUTB. A logic high signal on INA (INB) causes the output of OUTA(OUTB) to go high. And a logic low on INA (INB) causes the output of OUTA(OUTB) togo low.

| INA | INB | DIS | VDDI | VDDA | VDDB | OUTA | OUTB | Notes               |

|-----|-----|-----|------|------|------|------|------|---------------------|

|     |     |     | UVLO | UVLO | UVLO |      |      |                     |

| Н   | L   | L   | NO   | NO   | X    | Н    | L    |                     |

| L   | Н   | L   | NO   | Χ    | NO   | L    | Н    |                     |

| L   | L   | L   | NO   | Χ    | X    | L    | L    |                     |

| Н   | Н   | L   | NO   | NO   | NO   | Н    | Н    | Dual driver         |

| Н   | Н   | L   | NO   | NO   | NO   | L    | L    | Half bridge         |

| Χ   | Χ   | Ι   | NO   | NO   | NO   | L    | L    | Device disabled     |

| Χ   | Χ   | Χ   | YES  | NO   | NO   | L    | L    | VDDI UVLO activated |

| Χ   | Н   | L   | NO   | YES  | Х    | Ĺ    | Χ    | VDDA UVLO activated |

| Н   | Χ   | L   | NO   | NO   | YES  | Χ    | L    | VDDB UVLO activated |

Truth table

#### **Dead-time Program**

For the high side/low side configuration driver, there is a dead-time between OUTA and OUTB. The dead-time delay (tDT) is programmed by a resistor (RDT) connected from the DT input to ground and it can be calculated with below equation.

$$tDT$$

[ns]  $\approx 10 \times RDT$  [k ]

Here, tDT is the dead-time delay, RDT is the resistance value between DT and ground. The DT pin can be connected to VDDI or left floating to provide a nominal dead time at approximately 10 ns. A bypassing capacitor is recommended to be put between DT and GNDI to achieve better noise immunity.

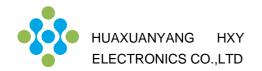

## **Application Information**

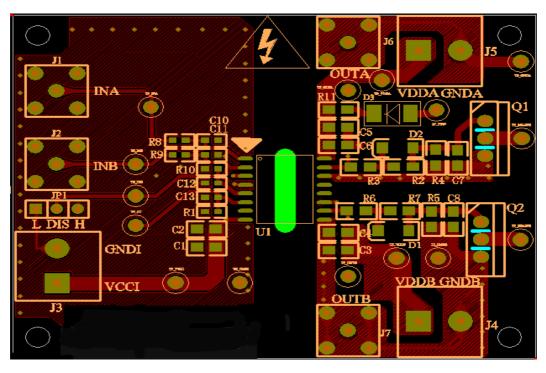

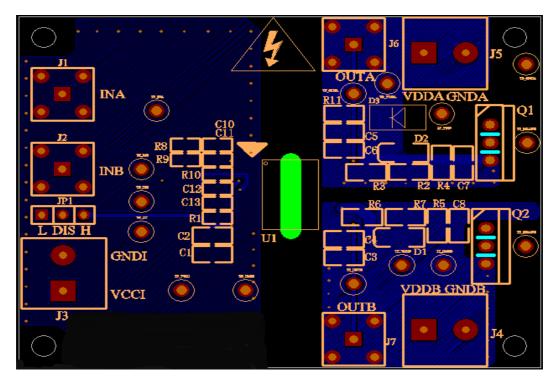

Typical Application Schematic

| Parameter               | Value  | Units |

|-------------------------|--------|-------|

| VDDI                    | 5      | V     |

| VDDA/VDDB               | 12     | V     |

| Input signal amplitude  | 5      | V     |

| Switching frequency(fs) | 10~100 | KHz   |

| Dead time               | 200    | nS    |

| RDT                     | 20     | kΩ    |

| CDT                     | 2.2    | nF    |

| RIN                     | 51     | Ω     |

| CIN                     | 33     | pF    |

| RON                     | 10     | Ω     |

| ROFF                    | -      | Ω     |

| RBOOT                   | 22     | Ω     |

| RGS                     | 10     | kΩ    |

| CVDDI                   | 10     | uF    |

| CVDD                    | 10     | uF    |

| СВООТ                   | 10     | uF    |

Recommended Design

PCB Top View

**PCB Bottom View**

#### **Insulation Characteristics**

|                              | Value          | Note                                      |

|------------------------------|----------------|-------------------------------------------|

| Installation class:          |                |                                           |

| mains≤ 150Vrms               | I-IV           |                                           |

| mains≤ 300Vrms               | I-IV           |                                           |

| mains≤ 600Vrms               | I-IV           |                                           |

| mains≤ 1000Vrms              | 1-111          |                                           |

| climatic class               | 40/125/21      |                                           |

| pollution degree             | 2              |                                           |

| Clearance (mm)               | 8              |                                           |

| Creepage (mm)                | 8              |                                           |

| Dтı(um)                      | >20            |                                           |

| Сті                          | 600            |                                           |

| DIN EN IEC 60747-17 (VDE 08  | 84-17):2021-10 |                                           |

| V <sub>IORM</sub> (Vpeak)    | 1420           |                                           |

| V <sub>PR</sub> (Vpeak)      | 2272           | Method A, VPR = 1.6xViORM, 1s ,qpd< 5pC   |

| V <sub>PR</sub> (Vpeak)      | 2663           | Method B, VPR = 1.875xVIORM, 1s ,qpd< 5pC |

| V <sub>IOTM</sub> (Vpeak)    | 5000           |                                           |

| Viosm (Vpeak)                | 5000           |                                           |

| Rio (ohms)                   | >10e9          |                                           |

| UL1577                       |                |                                           |

| V <sub>ISO</sub> 1min (Vrms) | 5700           |                                           |

| V <sub>ISO</sub> 1s (Vrms)   | 6840           |                                           |

**SOW-16 Insulation Characteristics**

High Reliability Isolated Dual-Channel Gate Driver

#### **Certification Information**

| Certification Level        |          | Industrial <sup>1</sup><br>(per JEDEC JESD 47E)  |

|----------------------------|----------|--------------------------------------------------|

|                            |          | The Series ICs have passed JEDEC's certification |

| Moisture Sensitivity Level |          | MSL1 <sup>2</sup><br>(per IPC/JEDEC J-STD-020C)  |

| ESD                        | MM Model | Class B<br>(Per JEDEC standard EIA/JESD22-A115)  |

| HBM Model                  |          | Class 2<br>(Per EIA/JEDEC standard JESD22-A114)  |

| IC Latch-up Test           |          | Class Level 1 A<br>(Per JESD78A)                 |

| RoHS Compliant             |          | YES                                              |

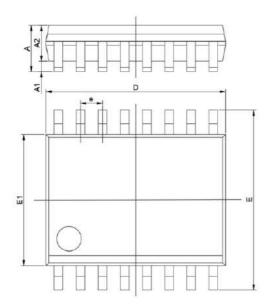

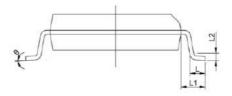

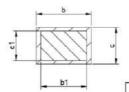

# **Package Outline Dimensions**

**SOW-16**

| Dimension | MIN       | MAX   |  |

|-----------|-----------|-------|--|

| A         |           | 2.65  |  |

| A1        | 0.1       | 0.3   |  |

| A2        | 2.05      |       |  |

| b         | 0.31      | 0.51  |  |

| b1        | 0.27      | 0.48  |  |

| С         | 0.1       | 0.33  |  |

| c1        | 0.1       | 0.3   |  |

| E         | 10.3      | BASIC |  |

| E1        | 7.58      | ASIC  |  |

| e         | 1.271     | BASIC |  |

| L         | 0.4       | 1.27  |  |

| L1        | 1.4REF    |       |  |

| 12        | 0.25BASIC |       |  |

| 0         | D         | В     |  |

| D         | 10.3      |       |  |

#### **Attention**

- Any and all HUA XUAN YANG ELECTRONICS products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your HUA XUAN YANG ELECTRONICS representative nearest you before using any HUA XUAN YANG ELECTRONICS products described or contained herein in such applications.

- HUA XUAN YANG ELECTRONICS assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein.

- Specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- HUA XUAN YANG ELECTRONICS CO.,LTD. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all HUA XUAN YANG ELECTRONICS products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of HUA XUAN YANG ELECTRONICS CO.,LTD.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

HUA XUAN YANG ELECTRONICS believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the HUA XUAN YANG ELECTRONICS product that you intend to use.