# Programmable Dual Output LCD Bias for Smartphone and Tablets

## General Description

The OCP2131 is designed to support positive / negative driven TFT-LCD panels up to10" at least (from SFF to MFF like tablets). The two output rails are usually connected to the Source Driver IC. The device uses a single inductor scheme in order to provide the user the smallest solution size possible as well as high efficiency.

It features a highly integrated step-up DC-DC converter with wide input voltage range from 2.7V to 5.5V. It is optimized for products powered by single-cell batteries (Li-Ion, Ni-Li, and Li-Polymer) and symmetrical output currents up to 120mA. An LDO and charge pump generate dual outputs at +5V (default) and -5V (default), whose voltages can be programmed via an I2Ccompatible interface. Optimized step-up, LDO and charge pump converters maximize conversion efficiency, exceeding 85%.

OCP2131 integrates all compensation and soft-start circuitry, which results in a simpler and smaller solution with much fewer external components. High switching frequency (1.2MHz) allows the use of a smaller inductor and capacitor to further reduce the solution size.

The I2C compatible interface allows to control the positive and negative outputs from+4V to +6V and -4V to -6V, respectively, as well as programming additional registers on the device.

The device is a RoHS compliant 15-Ball2.067mm X 1.237mm X 0.64mm WLCSP package.

#### Features

- Wide 2.7Vto5.5V Operating Input Range

- Dual Output Regulator with Single Inductor

- Programmable Output Voltage Voltages

- Positive Output Voltage Range: +4V to +6V (100mV/Step)

- Negative Output Voltage Range: -4V to -6V (100mV/Step)

- ±1.5% Output Voltage Accuracy

- Excellent Line Regulation

- Advanced Power-Save Mode for Light Load

- Support I2C Compatible Interface

- Integrated Compensation and Feedback Circuits

- 1uA Shut-Down Supply Current

- Boost Current Mode Operation

- Over Current Protection

- Internal Soft-Start Prevents Inrush Current

- Under Voltage Lock Out

- Thermal Shutdown

- Available in an 15-Ball WLCSP

- -40°Cto +85°COperatingTemperature Range

## Applications

- TFT LCD Smart-phones

- TFT LCD Tablets

- General Dual Power Supply Application

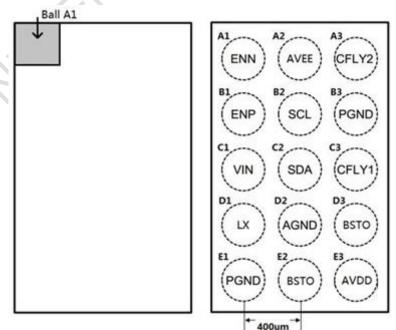

## ■ Pin Configuration

WLCSP-15 (Top View)

Figure 1, Pin Assignments of OCP2131

| Pin<br>Name | Pin No. | 1/0 | Pin Function                                                                                                                                                    |

|-------------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENN         | A1      | I   | Enable Input for negative output (AVEE). A logic high enable the negative Output, a logic low forces the output into shutdown mode reducing the supply current. |

| AVEE        | A2      | 0   | Charge pump output pin of the negative power.                                                                                                                   |

| CFLY2       | A3      | I/O | Negative charge pump flying capacitor pin.                                                                                                                      |

| ENP         | B1      | I   | Enable Input for positive output (AVDD). A logic high enable the negative Output, a logic low forces the output into shutdown mode reducing the supply current. |

| SCL         | B2      | I/O | SCL clock input pin of I2C interface.                                                                                                                           |

| PGND        | B3,E1   | Р   | Power Ground.                                                                                                                                                   |

| VIN         | C1      | Р   | Input voltage supply pin. Connect a larger than 4.7uF capacitor to ground.                                                                                      |

| SDA         | C2      | I/O | SDA bi-direction data pin of the I2C interface                                                                                                                  |

| CFLY1       | C3      | I/O | Negative charge pump flying capacitor pin.                                                                                                                      |

| LX          | D1      | I/O | Switch pin of boost converter.                                                                                                                                  |

| AGND        | D2      | Р   | Analog ground.                                                                                                                                                  |

| BSTO        | D3,E2   | I/O | Boost converter output pin.                                                                                                                                     |

| AVDD        | E3      | 0   | Output pin of the LDO positive voltage.                                                                                                                         |

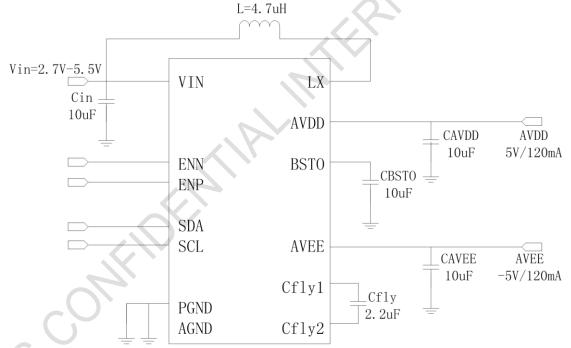

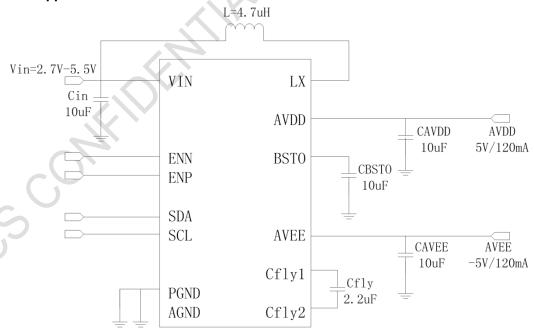

## ■ Typical Application Circuit

Figure 2, Typical Application Circuit of OCP2131

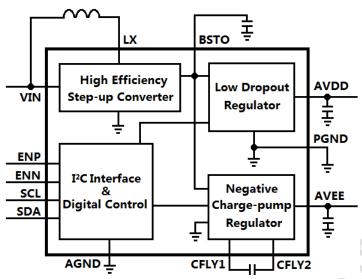

## Block Diagram

Figure 3, Block Diagram of OCP2131

■ Absolute Maximum Ratings¹ (T<sub>A</sub>=25°C unless otherwise noted)

| Parameter                                             | Symbol          | Rating      | Unit |

|-------------------------------------------------------|-----------------|-------------|------|

| VIN, CFLY1, BSTO, LX, ENN, ENP, AVDD, SCL, SDA to GND | V*              | -0.3 to 7.0 | V    |

| AGND and PGND                                         | GND             | -0.3 to 0.3 | V    |

| CFLY2, AVEE                                           | V*              | -6.5 to 0.3 | V    |

| Package Thermal Resistance, 15-Ball WLCSP             | Θја             | 77          | °C/W |

| Power Dissipation <sup>2</sup>                        | P <sub>D</sub>  | 1.3         | W    |

| Lead Temperature (Soldering, 10 Sec.)                 | T <sub>LT</sub> | 260         | °C   |

| Storage Temperature Range                             | Ts              | -55 to +150 | °C   |

| Maximum Operating Junction Temperature Range          | TJ              | -40 to 125  | °C   |

■ Recommended Operating Conditions<sup>3</sup>(T<sub>A</sub>=25°C unless otherwise noted)

| - recommended operating t            | Jonathon          | <b>3</b> (TA-25 C unless | outerwise rioled) |      |

|--------------------------------------|-------------------|--------------------------|-------------------|------|

| Parameter                            | Symbol            | Conditions               | Rating            | Unit |

| Supply Voltage                       | $V_{IN}$          | Operating                | 2.7 ~ 5.5         | V    |

| Positive Output Voltage              | V <sub>AVDD</sub> | Operating                | +4.0 ~ +6.0       | V    |

| Negative Output Voltage              | V <sub>AVEE</sub> | Operating                | -4.0 ~ -6.0       | V    |

| Positive Output Current              | I <sub>AVDD</sub> | Operating                | 0 ~ 120           | mA   |

| Negative Output Current              | I <sub>AVEE</sub> | Operating                | 0 ~ 120           | mA   |

| Inductor                             | L                 | Operating                | 2.2 ~ 4.7         | uН   |

| Flying Capacitor                     | CFLY              | Operating                | 2.2 ~4.7          | uF   |

| Input Capacitor                      | Cin               | Operating                | 4.7~10            | uF   |

| AVDD, AVEE, BSTO Output<br>Capacitor | C*                | Operating                | 4.7 ~10           | uF   |

| Operating Ambient Temperature        | T <sub>A</sub>    | Operating                | -40 ~ +85         | °C   |

Notes: 1) Exceeding these ratings may damage the device.

<sup>2)</sup> The maximum allowable power dissipation is a function of the maximum junction temperature  $T_{J(MAX)}$ , the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{D(MAX)} = (T_{J(MAX)} - T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

<sup>3)</sup> The device is not guaranteed to function outside of its operating conditions.

## ■ Electrical Characteristics<sup>4</sup>

(Unless otherwise noted, typical values are at T<sub>A</sub>=25°C, V<sub>IN</sub>=3.7V, ENN=ENP=V<sub>IN</sub>, V<sub>AVDD</sub>=5.0V, V<sub>AVEE</sub>=-5.0V)

| Symbo              | l Parameter                         | Conditions                      | Min. | Тур.     | Max. | Unit |

|--------------------|-------------------------------------|---------------------------------|------|----------|------|------|

|                    | l Supply                            |                                 | •    | <u> </u> |      | •    |

| Vin                | Power supply                        |                                 | 2.7  | -        | 5.5  | V    |

| ΙQ                 | Quiescent Current                   | I <sub>OUT</sub> =0mA           | -    | 0.7      | 1.5  | mA   |

| I <sub>SD</sub>    | Shutdown down current               | ENP=ENN=0V                      | -    | 0.1      | -    | uA   |

| Tss                | Soft-Start Period                   |                                 | -    | 0.5      | -    | mS   |

| $V_{\text{UVLO}}$  | Input UVLO Threshold                | V <sub>IN</sub> Rising          | 2.0  | 2.3      | 2.5  | V    |

| $V_{UVH}$          | Input UVLO Threshold Hysteresis     |                                 |      | 0.20     | -    | V    |

| Logic C            | ontrol: ENN, ENP, SCL, SDA          |                                 |      |          |      |      |

| ViH                | High Level Threshold Voltage        | V <sub>EN</sub> Rising          | 1.4  | -        |      | V    |

| $V_{IL}$           | Low Level Threshold Voltage         |                                 | -    | -        | 0.4  | V    |

| Ren                | ENP and ENN Pull-Down Resistance    |                                 | -    | 1        | -    | МΩ   |

|                    | Converter                           |                                 |      |          |      |      |

| Ішміт              | Boost converter current limit       |                                 | 0.9  | 1.2      | 1.5  | Α    |

| f∟x                | Boost converter switching frequency |                                 | 1.0  | 1.2      | 1.4  | MHz  |

| LDO Po             | sitive Voltage VAVDD                |                                 |      |          | •    |      |

| Vavdd              | Positive output voltage range       |                                 | 4.0  | -        | 6.0  | V    |

| V <sub>AVDDA</sub> | Positive output voltage accuracy    |                                 | -1.5 | -        | 1.5  | %    |

| I <sub>AVDD</sub>  | Positive output current capability  |                                 | -    | 120      | -    | mA   |

| $V_{DO}$           | Dropout Voltage                     | VBSTO=VAVDD=5.0V,<br>IOUT=120mA | -    | 150      | -    | mV   |

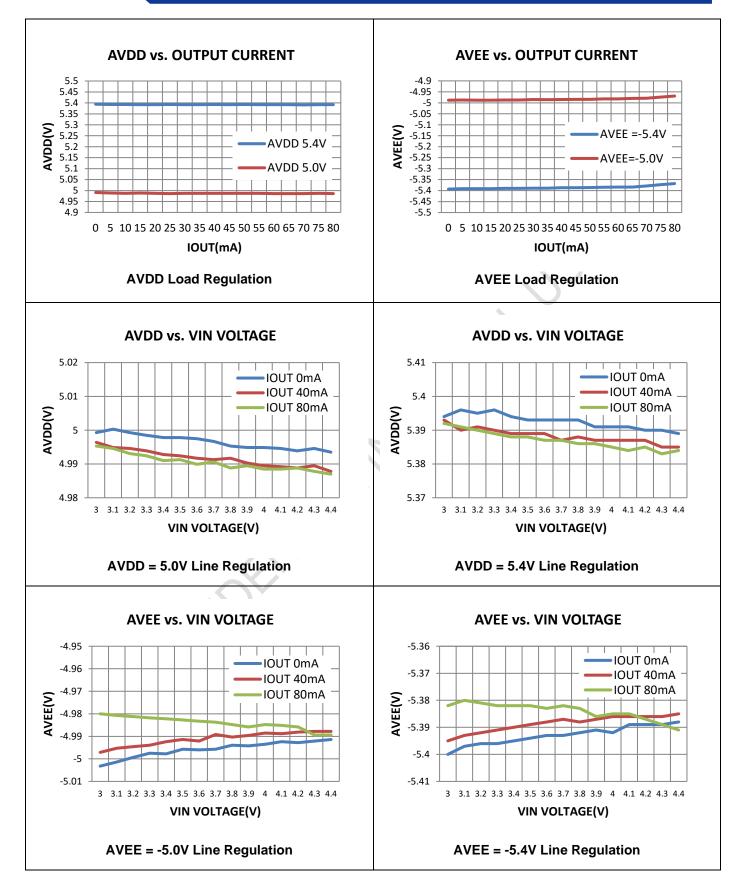

| $V_{LIP}$          | Line regulation                     | VIN=2.7~5.5V,<br>IOUT=40mA      | -    | 0.1      | -    | %/V  |

| VLOP               | Load regulation                     | ∆Iо∪т=120mA                     | -    | 1        | -    | %    |

| Charge             | Pump Negative Output Voltage VAVEE  |                                 |      |          | •    |      |

| V <sub>AVEE</sub>  | Negative output voltage range       |                                 | -4.0 | -        | -6.0 | V    |

| V <sub>AVEEA</sub> | Negative output voltage accuracy    |                                 | -1.5 | -        | 1.5  | %    |

| I <sub>AVEE</sub>  | Negative output current capability  |                                 | -    | 120      | -    | mA   |

| FLX CP             | Charge pump switching frequency     | <b>/</b>                        | 400  | 600      | 800  | KHz  |

| $V_{LIP}$          | Line regulation                     | VIN=2.7~5.5V,<br>IOUT=40mA      | -    | 0.1      | -    | %/V  |

| VLOP               | Load regulation                     | ∆ <b>І</b> о∪т=120mA            | -    | 1        | -    | %    |

| Therma             | Shut-down Section <sup>1</sup>      |                                 | •    |          | •    |      |

| TSD                | Thermal Shut-down Threshold         |                                 | -    | 140      | -    | °C   |

|                    | Thermal Shut-down Hysteresis        |                                 |      | 20       |      | °C   |

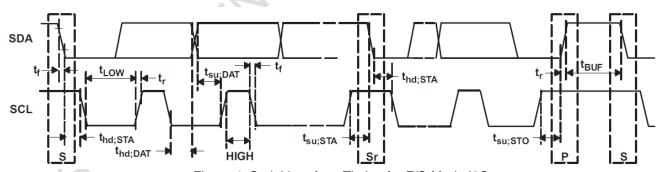

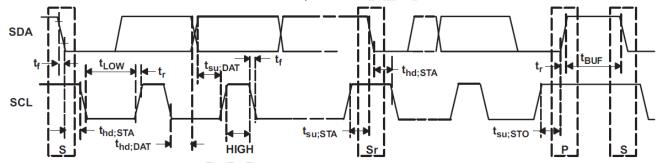

| I2C Cor          | npatible Timing Specifications (SCL,                  | SDA), see Figure 4 |                      |   |      |     |

|------------------|-------------------------------------------------------|--------------------|----------------------|---|------|-----|

| fscL             | SCL clock frequency                                   | Standard Mode      | -                    | - | 100  | KHz |

| ISCL             | SCL Clock frequency                                   | Fast Mode          | -                    | - | 400  | KHz |

| t                | Low period of the SCL clock                           | Standard Mode      | 4.7                  | - | -    | us  |

| t <sub>LOW</sub> | Low period of the SCL clock                           | Fast Mode          | 1.3                  | - | -    | us  |

| thigh            | High period of the SCL clock                          | Standard Mode      | 4.0                  | - | -    | us  |

| เกเษก            | Trigit period of the OCL clock                        | Fast Mode          | 0.6                  | - | -    | us  |

| <b>t</b> BUF     | Bus free time between a STOP and                      | Standard Mode      | 4.7                  | - | -    | us  |

| IBUF             | START condition                                       | Fast Mode          | 1.3                  | - | -    | us  |

| <b>t</b> HD,STA  | Hold time for a repeated START                        | Standard Mode      | 4.0                  | - | - 1  | us  |

| tnD,STA          | condition                                             | Fast Mode          | 0.6                  | - |      | us  |

| tsu,sta          | Setup time for a repeated START                       | Standard Mode      | 4.7                  | - | -    | us  |

| 150,51A          | condition                                             | Fast Mode          | 0.6                  | - | (-)  | us  |

| tsu,dat          | Data setup time                                       | Standard Mode      | 0.25                 | - |      | us  |

| LSU,DAT          | Data setup time                                       | Fast Mode          | 0.1                  |   | / -  | us  |

| <b>t</b> hd,dat  | Data hold time                                        | Standard Mode      | 0.05                 |   | 3.45 | us  |

| thD,DA1          | Data Hold time                                        | Fast Mode          | 0.05                 | ~ | 0.9  | us  |

|                  | Rise time of SCL signal after a                       | Standard Mode      | 20+0.1C <sub>B</sub> | - | 1000 | ns  |

| <b>t</b> RCL1    | repeated START condition and after an acknowledge bit | Fast Mode          | 20+0.1Св             | _ | 1000 | ns  |

| to or            | Pigg time of SCI piggal                               | Standard Mode      | 20+0.1Св             | - | 1000 | ns  |

| <b>t</b> RCL     | Rise time of SCL signal                               | Fast Mode          | 20+0.1Св             | - | 300  | ns  |

| <b>t</b> FCL     | Fall time of SCL signal                               | Standard Mode      | 20+0.1C <sub>B</sub> | - | 300  | ns  |

| <b>L</b> FCL     | Fail time of SCL signal                               | Fast Mode          | 20+0.1C <sub>B</sub> | - | 300  | ns  |

| <b>t</b> RDA     | Rise time of SDA signal                               | Standard Mode      | 20+0.1C <sub>B</sub> | - | 1000 | ns  |

| <b>I</b> KDA     | Trise time of SDA signal                              | Fast Mode          | 20+0.1Св             | - | 300  | ns  |

| <b>t</b> FDA     | Fall time of SDA signal                               | Standard Mode      | 20+0.1Св             | - | 300  | ns  |

| LFDA             | Tall time of SDA signal                               | Fast Mode          | 20+0.1Св             | - | 300  | ns  |

| tsu.sto          | Setup time for STOP condition                         | Standard Mode      | 4.0                  | - | -    | us  |

|                  | ·                                                     | Fast Mode          | 0.6                  | - | -    | us  |

| Св               | Capacitive load for SCL and SDA                       |                    | -                    | - | 0.4  | nF  |

Note. 4, OCP2131 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range by design, characterization and correlation with statistical process controls.

Figure 4, Serial Interface Timing for F/S-Mode I2C

## ■ Typical Characteristics—OCP2131

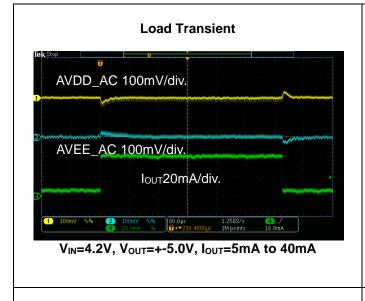

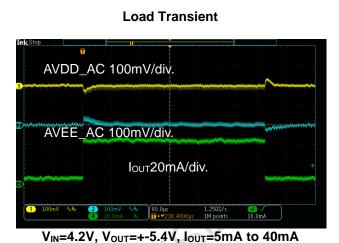

(Unless otherwise noted, typical values are at Ta=25°C, Vin=3.7V, L=4.7uH, Cin=Cavdd=Cbsto=Cavee=4.7uF, Cfly==2.2uFVavdd=5.0V, Vavee=-5.0V, Iavdd=Iavee=40mA)

$V_{IN}=4.2V$ ,  $V_{OUT}=+-5.0V$ ,  $I_{OUT}=0$ mA

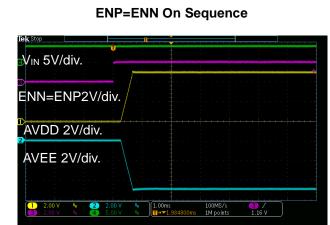

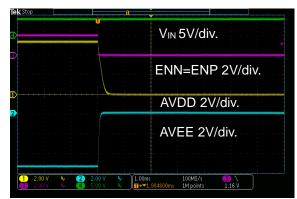

## **ENP=ENN On Sequence**

$V_{IN}=4.2V$ ,  $V_{OUT}=+-5.4V$ ,  $I_{OUT}=0mA$

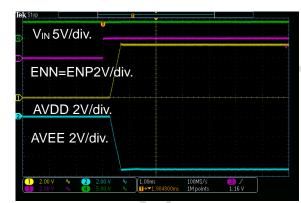

## **ENP=ENN On Sequence**

$V_{IN}$ =4.2V,  $V_{OUT}$ =+-5.0V,  $I_{OUT}$ =40mA

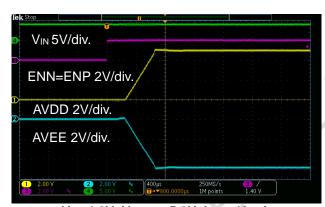

## **ENP=ENN On Sequence**

V<sub>IN</sub>=4.2V, V<sub>OUT</sub>=+-5.4V, I<sub>OUT</sub>=40mA

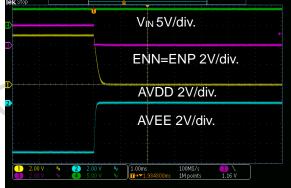

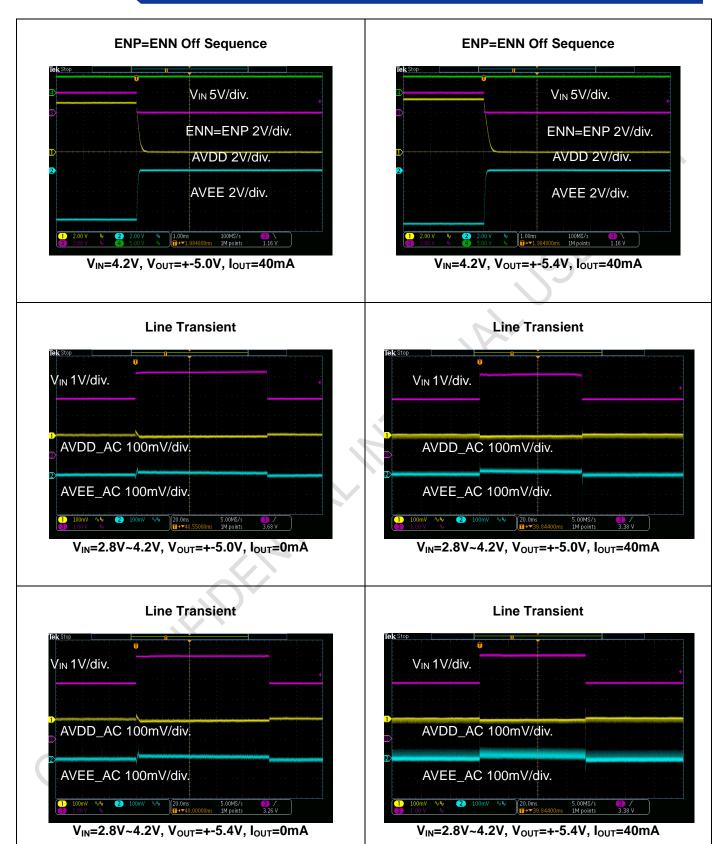

## **ENP=ENN Off Sequence**

$V_{IN}=4.2V$ ,  $V_{OUT}=+-5.0V$ ,  $I_{OUT}=0mA$

## **ENP=ENN Off Sequence**

$V_{IN}=4.2V$ ,  $V_{OUT}=+-5.4V$ ,  $I_{OUT}=0mA$

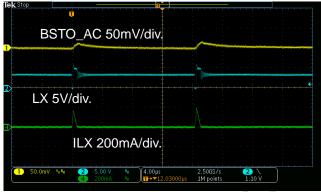

**Boost Converter Light Load (1mA)**

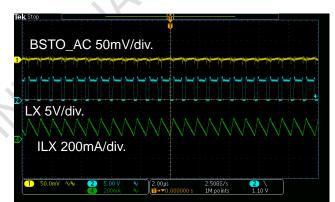

## **BOOST CONVERTER HEAVY LOAD**

**Boost Converter Heavy Load (80mA)**

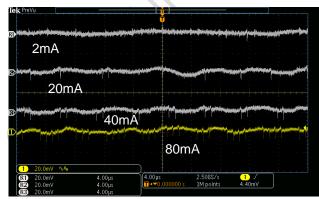

## **AVDD RIPPLE**

I<sub>OUT</sub>=2 20 40 80mA

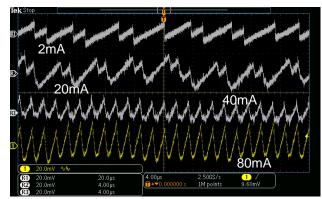

## **AVEE RIPPLE**

I<sub>OUT</sub>=2 20 40 80mA

## Functional Description

The OCP2131 is designed to support positive / negative driven TFT-LCD panels up to 10" at least (from SFF to MFF like tablets). The two output rails are usually connected to the Source Driver IC. The device uses a single inductor scheme in order to provide the user the smallest solution size possible as well as high efficiency. It features a highly integrated step-up DC-DC converter with wide input voltage range from 2.7V to 5.5V. It is optimized for products powered by single-cell batteries (Li-Ion, Ni-Li, Li-Polymer) and symmetrical output currents up to 80mA. An LDO and charge pump generate dual outputs at +5V (default) and -5V (default), whose voltages can be programmed via an I2C compatible interface. Optimized step-up, LDO and charge pump converters maximize conversion efficiency, exceeding 85%.

TheOCP2131 integrates all compensation and soft-start circuitry, which results in a simpler and smaller solution with much fewer external components. High switching frequency (1.2MHz) allows the use of a smaller inductor and capacitor to further reduce the solution size.

The I2C compatible interface allows to control the positive and negative outputs from +4.0V to +6.0V and -4.0V to -6.0V, respectively, as well as programming additional registers on the device.

#### **Under Voltage Lock Out:**

The OCP2131 integrates an Under-voltage Lockout block (or UVLO) that enables the device once the voltage on VIN pin exceeds the UVLO\_rising threshold of 2.5 V maximum. No output voltage will however be generated as long as the enable signals are not pulled HIGH. The device, as well as all converters (boost converter, LDO, CPN), will be disabled as soon as the VIN voltage falls below the UVLO\_falling threshold. The UVLO\_falling threshold is designed in a way that the OCP2131 will continue operating as long as VIN stays above 2.3 V. This guarantees a proper operation even in the event of extensive line transients when the battery gets suddenly heavily loaded.

## **Boost Converter**

#### **Boost Converter Operation:**

The synchronous boost converter uses a current mode topology and operates at a quasi-fixed frequency of typically 1.2 MHz, allowing chip inductors such as 2.2µH or 4.7µH to be used. The converter is internally compensated and provides a regulated output voltage automatically adjusted depending on the programmed VAVDD and VAVEE voltages. The boost operates either in continuous conduction mode (CCM) or Pulse Frequency Modulation mode (PFM), depending on the load current in order to provide the highest efficiency possible.

## Power Up and Soft Start (Boost Converter):

The step-up converter operates when the enable signal, ENN or ENP, is pulled high and VIN voltage is greater than UVLO. If the enable signal is already high when VIN reaches the UVLO threshold, the step-up converter will start switching immediately. An integrated soft-start circuit controls excessive inrush current from the battery during startup.

#### **Power Down:**

The boost converter stops switching when VIN reaches the UVLO\_falling threshold or when both output rails are disabled, if VIN is still above the UVLO.

## **Isolation (Boost Converter):**

The boost converter output (BSTO) is fully isolated from the input signal VIN.

## **Output Voltage (Boost Converter):**

The output voltage of the boost converter is automatically adjusted depending on the programmed VAVDD and VAVEE voltages.

## Advanced Power Save Mode for Light Load Efficiency and PFM:

The OCP2131 device integrates a power save mode to improve efficiency at light load. In power save mode the converter stops switching when the inductor current reaches 0A. The device resumes its switching activity with one or several pulses once the VBSTO voltage falls below its regulation level, and goes again into power save mode once the inductor current reaches 0A. Each pulse maintains the same duty ratio, but the frequency of these pulses varies according to the output load. This operating mode is also known as Pulse Frequency Modulation or PFM.

## LDO Regulator LDO Operation:

The Low Dropout regulator (or LDO) generates the positive voltage rail VAVDD by regulating down the output voltage of the boost converter (VBSTO). Its inherent PSRR helps filtering the output ripple of the boost converter in order to provide on AVDD pin a clean voltage, e.g. to supply the source driver IC of the display.

#### Power Up and Soft Start (LDO):

The LDO starts operating as soon as the ENP signal is pulled HIGH, VIN voltage is above the UVLO (under voltage lockout) threshold and the boost converter has reached its Power Good threshold. In the case where the enable signal is already HIGH when VIN reaches the UVLO\_rising threshold, the boost converter will start first and the LDO will start when the boost converter has reached its target voltage. The LDO integrates a soft-start that slowly ramps up its output voltage VAVDD within 500µs typically.

## Power Down and Discharge (LDO):

The LDO stops operating when VIN reaches the UVLO\_falling threshold or when the ENP is pulled LOW. The positive rail can be actively discharged to GND during power-down.

## Isolation (LDO):

The LDO is isolating the VAVDD rail from VBSTO (boost converter output) as long as the rail is not enabled in order to ensure flexible startup like VAVEE before VAVDD.

## **Setting the Output Voltage (LDO):**

The output voltage of the LDO is programmable via a two-wire interface with 5 bits, from 4.0V to 6.0V with 100mV steps.

#### **Output Capacitor Selection (LDO):**

The LDO is designed to operate with a 4.7µF minimum ceramic output capacitor.

## **Charge Pump Negative Converter**

#### **CPN Operation:**

The negative charge pump (or CPN) generates the negative voltage rail VAVEE by inverting and regulating the output voltage of the boost converter (VBSTO). The converter uses 4 switches and an external flying capacitor to generate the negative rail. Two of the switches are turned on in the first phase to charge the flying capacitor up to VBSTO, and in the second phase they are turned-off and the two others turn on to pump the energy negatively out of the AVEE capacitor.

## Power Up and Soft Start (CPN):

The CPN starts operating as soon as the ENN signal is pulled HIGH, that VIN voltage is above the UVLO (under voltage lockout) threshold and that the boost converter has reached its Power Good threshold. In the case where the enable signal is already HIGH when VIN reaches the UVLO\_rising threshold, the boost converter will start first and the CPN will start when the boost converter has reached its target voltage. The CPN integrates a soft-start that slowly ramps up its output voltage VAVEE within 500µs typically.

## Power Down and Discharge (CPN):

The CPN stops operating when VIN reaches the UVLO\_falling threshold or when the ENN is pulled LOW the negative rail can be actively discharged to GND during power-down.

## Isolation (CPN):

The CPN is isolating the VAVEE rail from VBSTO (boost converter output) as long as the rail is not enabled in order to ensure flexible startup like VAVDD before VAVEE.

#### **Setting the Output Voltage (CPN):**

The output voltage of the CPN is programmable via a two-wire interface with 5 bits, from -4.0V to -6.0V with100mV steps.

#### **Output Capacitor Selection (CPN):**

The CPN is designed to operate with a 10µF minimum ceramic output capacitor.

## Flying Capacitor Selection (CPN):

The CPN needs an external flying capacitor. The minimum value for Smartphone application is  $2.2\mu F$  and  $4.7\mu F$  for Tablet application. Special care must be taken while choosing the flying capacitor as it will directly impact the output voltage accuracy and load regulation performance. Therefore, a minimum capacitance of  $1\mu F$  and  $2.2\mu F$ respectively for Smartphone and Tablet applications must be achieved by the capacitor at a DC bias voltage of |VAVEE| + 300 mV. For proper operation, the flying capacitor value must be lower than the output capacitor of the boost converter on BSTO pin.

#### **Thermal Shutdown:**

The OCP2131 contains an internal thermal sensor that limits the total power dissipation in the device and protects it in the event of an extended thermal fault condition. When the die temperature exceeds +140°C (typ), the thermal sensor shuts down the device, turning off the DC-DC converter to allow the die to cool. After the die temperature falls by 20°C (typ), the device restarts, using the soft-start sequence.

## Appendix I2C Interface

## **I2C Serial Interface Description:**

The OCP2131 supports the I2C compatible interface and the data transmission protocol in two modes: standard mode and the fast mode. A device that sends data onto the bus is defined as a transmitter, and a device receiving data as a receiver. The device that controls the message is called a master; the devices that are controlled by the master are slaves. The bus must be controlled by a master device which generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The OCP2131operatesas a slave on the I2C bus. Connections to the bus are made via the open-drain I/O lines SDA and SDL.

Figure 5, Serial Interface Timing for F/S-Mode I2C

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as control signals. Accordingly, the following bus conditions have been defined:

## **Bus Not Busy:**

Both data and clock lines remain HIGH.

#### **Start Data Transfer:**

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH defines a START condition.

## **Stop Data Transfer:**

A change in the state of the data line, from LOW to HIGH, while the clock is HIGH defines a STOP condition.

#### Data Valid:

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise, and each receiver acknowledges with a ninth-bit. Within the I2C bus specifications, a standard mode (100 kHz clock rate) and a fast mode (400 kHz clock rate) are defined. The OCP2131 works in the two modes.

## Acknowledge:

Each receiving device, when accessed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse, which is associated with this acknowledge bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

Depending upon the state of the R/W bit, two types of data transfer are possible:

#### 1. Data transfer from a master transmitter to a slave receiver.

The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first.

#### 2. Data transfer from a slave transmitter to a master receiver.

The master transmits the first byte (the slave address). The slave then returns an acknowledge bit, followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data is transferred with the most significant bit (MSB) first.

The OCP2131 can operate in the following two modes:

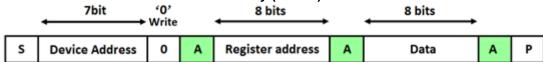

## 1. Slave Receiver Mode (Write Mode):

Serial data and clock are received through SDA and SCL. After each byte is received an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and endof a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit (see Figure 4 for Interface). The slave address byte is the first byte received after the master generates the START condition. The slave address byte contains the 7- OCP2131 address followed by the direction bit (R/W), which, for a write, is 0. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. After the OCP2131 acknowledges the slave address + write bit, the master transmits a register address to theOCP2131. This sets the register pointer on the OCP2131. The master may then transmit zero or more bytes of data, with the OCP2131Acknowledgingeach byte received. The address pointer will increment after each data byte is transferred. The master generates a STOP condition to terminate the data write.

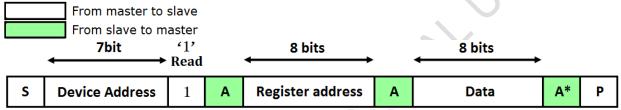

## 2. Slave Transmitter Mode (Read Mode):

The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the OCP2131 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer. The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit OCP2131 address followed by the direction bit (R/W), which, for a read, is 1. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. The OCP2131 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The OCP2131 must receive a "not acknowledge" to end a read.

The 7-bit slave device address is 0111110 binary (or 3Eh).

Figure 6, I2C Serial Interface Write - Slave Receiver Mode

Where

S = START condition

P = STOP condition

Device Address = 0111110(7bits, MSB first)

Register Address = Reg0 - Reg1address (8bits)

Data = data to read or write (8bits)

1 = read Command bit

0 = write Command bit

A = acknowledge (SDA low)

A\* = not acknowledge (SDA high)

Figure 7, I2C Serial Interface Read - Slave Transmitter Mode

## **Address Byte:**

The address byte is the first byte received following the START condition from the master device. The first seven bits (MSBs) of the slave address are factory preset to 0111110(3Eh).

| Serial Data-Words | Address Byte |     |     |     |     |     |     |     |

|-------------------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Serial Data Bits  | SD7          | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0 |

| Input Register    | AD7          | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 |

| Function          | 0            | 1   | 1   | 1   | 1   | 1   | 0   | R/W |

#### Table 1, Address Byte Code

The last bit of the address byte (R/W) defines the operation to be performed. When set to a "1", a read operation is selected; when set to a "0", a write operation is selected. Following the START condition, the OCP2131monitors the SDA bus and checks the device type identifier being transmitted. Upon receiving the 0111110 code, and the R/W bit, the slave device outputs an acknowledge signal on the SDA line.

| Command Address | Description                  | Default | D7 | 7 D6 D5   |  | D4 | D3        | D2   | D1 | D0 |

|-----------------|------------------------------|---------|----|-----------|--|----|-----------|------|----|----|

| 00h             | Positive Output AVDD Voltage | 0AH     |    | RSVD      |  |    | AVDD[4:0] |      |    |    |

| 01h             | Negative Output AVEE Voltage | 0AH     |    | RSVD      |  |    | AVEE[4:0] |      |    |    |

| 03h             | Controller                   | 33H     |    | RSVD      |  |    |           | RSVE | )  |    |

| 04h             | Device ID                    | 0DH     |    | Read Only |  |    |           |      |    |    |

|                 |                              |         |    |           |  |    | -         |      |    |    |

| Address    | D7           | D6                                      | D5                                      | D4                                      | D3           | D2           | D1                                            | D0                                           |

|------------|--------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|--------------|--------------|-----------------------------------------------|----------------------------------------------|

| 03h        | 0            | 0                                       | 1                                       | 1                                       | 0            | 0            | 1                                             | 1                                            |

| Controller | Read<br>only | Read<br>&write<br>Default:0<br>Reserved | Read<br>&write<br>Default:1<br>Reserved | Read<br>&write<br>Default:1<br>Reserved | Read<br>only | Read<br>only | 1:Discharge<br>Default 1<br>0:no<br>discharge | 1:Discharge<br>Default1<br>0:no<br>discharge |

## I2C Serial Bus Register Map:

The device has two registers, Reg0 to Reg1. Each register includes one data byte (8 bits) that can be written or read via the I2C interface.

| AVDD-00h | AVDD(V) | AVEE-01h | AVEE(V) |

|----------|---------|----------|---------|

| 00h      | 4.0     | 00h      | -4.0    |

| 01h      | 4.1     | 01h      | -4.1    |

| 02h      | 4.2     | 02h      | -4.2    |

| 03h      | 4.3     | 03h      | -4.3    |

| 04h      | 4.4     | 04h      | -4.4    |

| 05h      | 4.5     | 05h      | -4.5    |

| 06h      | 4.6     | 06h      | -4.6    |

| 07h      | 4.7     | 07h      | -4.7    |

| 08h      | 4.8     | 08h      | -4.8    |

| 09h      | 4.9     | 09h      | -4.9    |

| 0Ah      | 5.0     | 0Ah      | -5.0    |

| 0Bh      | 5.1     | 0Bh      | -5.1    |

| 0Ch      | 5.2     | 0Ch      | -5.2    |

| 0Dh      | 5.3     | 0Dh      | -5.3    |

| 0Eh      | 5.4     | 0Eh      | -5.4    |

| 0Fh      | 5.5     | 0Fh      | -5.5    |

| 10h      | 5.6     | 10h      | -5.6    |

| 11h      | 5.7     | 11h      | -5.7    |

| 12h      | 5.8     | 12h      | -5.8    |

| 13h      | 5.9     | 13h      | -5.9    |

| 14h      | 6.0     | 14h      | -6.0    |

## Application Information

## **Recommended Application Circuit:**

Figure 8, Typical Smartphone Application Circuit of OCP2131

#### Capacitor Selection:

Small size X5R or X7R ceramic capacitors are recommended for the OCP2131 application.  $4.7\mu F$  capacitors are suggested for the input VIN and AVDD. 10uF capacitors are for the outputs BSTO and AVEE. The input capacitor should be placed as close as possible to the input pin and the PGND pin of the OCP2131. For better input voltage filtering, this value can be increased. For the output capacitors, higher capacitor values can be used to improve the load transient response. For higher output current up to 80mA, the AVDD and AVEE output capacitors can be increased to  $10\mu F$ .

The capacitor datasheet determines what value of capacitor is required to guarantee a minimum capacitance value for a given bias voltage and over operating temperature.

| Capacitor(uF) | Supplier | Component Code    | EIA Size | Voltage Rating(V) | Comments     |

|---------------|----------|-------------------|----------|-------------------|--------------|

| 2.2           | Murata   | GRM188R61C225KAAD | 0603     | 16                | $C_{FLY}$    |

| 4.7           | Murata   | GRM188R61C475KAAJ | 0603     | 16                | CIN, CAVDD,  |

| 10            | Murata   | GRM219R61C106KA73 | 0603     | 16                | CBSTO, CAVEE |

**Table 2, Input And Output Capacitor Selection**

#### **Inductor Selection:**

Saturation current: the inductor must handle the maximum peak current { $I_{L\_SAT} > I_{LXPEAK}$ , or  $I_{L\_SAT} > [I_{LIM\_min} + \Delta I_{L}]$  as conservative approach}

DC Resistance: the lower the DCR, the lower the losses

Inductor value: in order to keep the ratio  $I_{OUT}$  /  $\Delta I_{L}$  low enough for proper sensing operation purpose, it is recommended to use a 4.7µH inductor for Smartphone applications (a 2.2µH might however be used, but the efficiency might be lower than with 4.7µH at light output loads) and for Tablet applications, 2.2µH are recommended.

| L(uH) | Supplier | Component Code      | EIA Size | DCR TYP(mΩ) | I <sub>SAT</sub> (A) |

|-------|----------|---------------------|----------|-------------|----------------------|

| 4.7   | TDK      | VLS252012HBX-4R7M-1 | 2520     | 200         | 1.4                  |

**Table 3, Inductor Selection**

Ordering Information

| Part Number   | Driver<br>Capability | Package Type     | Package<br>Qty | Temperature | Eco<br>Plan | Lead/Ball<br>Finish |

|---------------|----------------------|------------------|----------------|-------------|-------------|---------------------|

| OCP2131WPAD-G | +/-120mA             | 15-Ball<br>WLCSP | 3000pcs        | -40∼85℃     | Green       | Su/Ag/Cu            |

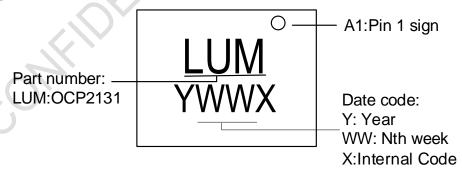

## Marking Information

15-Ball WLCSP

# OCS Confidential DO NOT COPY

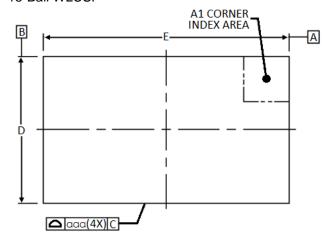

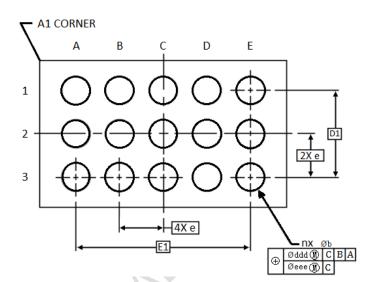

## ■ Package Information

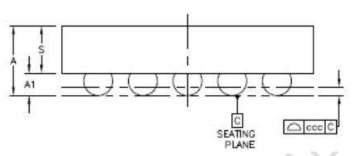

15-Ball WLCSP

|                            |   | SYMBOL       | COMMON DIMENSIONS |     |  |

|----------------------------|---|--------------|-------------------|-----|--|

| TOTAL THICKNESS            |   | Α            | 0.640± 0.043      |     |  |

| WAFER THICKNESS            |   | S            | 0.447± 0.029      |     |  |

| STAND OFF                  |   | A1           | 0.193±0.029       |     |  |

| BODY SIZE                  | X | Ш            | 2.067             |     |  |

| BODT SIZE                  | Υ | D            | 1.237             |     |  |

| EDGE BALL CENTER TO CENTER | Х | E1           | 1.6               | BSC |  |

|                            | Υ | D1           | 0.8               | BSC |  |

| PITCH                      |   | е            | 0.4               | BSC |  |

| BALL DIAMETER              |   |              | 0.231 ±0.023      |     |  |

| BALL/BUMP WIDTH            | b | 0.231 ±0.023 |                   |     |  |

| BALL/BUMP COUNT            | n | 15           |                   |     |  |

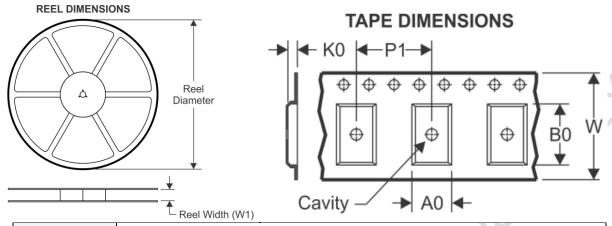

## Packing Information

## 15-Ball WLCSP

| A0 | Dimension designed to accommodate the component width     |  |  |  |

|----|-----------------------------------------------------------|--|--|--|

| В0 | Dimension designed to accommodate the component length    |  |  |  |

| K0 | Dimension designed to accommodate the component thickness |  |  |  |

| W  | Overall width of the carrier tape                         |  |  |  |

| P1 | Pitch between successive cavity centers                   |  |  |  |

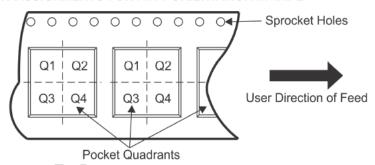

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Package tape               | Package Drawing | MSL          | SPQ        | Reel<br>Diame<br>ter<br>(mm) | Reel<br>Width<br>W1(mm) |

|----------------------------|-----------------|--------------|------------|------------------------------|-------------------------|

| 15-Ball WLCSP<br>(WLCSP15) | LUM             | Level-1-260C | 3000       | 180                          | 8.4                     |

| A0<br>(mm)                 | B0<br>(mm)      | K0<br>(mm)   | P1<br>(mm) | W<br>(mm)                    | PIN A1<br>Quadrant      |

| 1.4                        | 2.2             | 0.77         | 4.0        | 8.0                          | Q1                      |

OCS Confidential DO NOT COPY

**OCP2131**

#### IMPORTANT NOTICE

Orient-Chip Semiconductor Co., Ltd (OCS) and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. These separate provisions won't be provided.

**Page19 - 19** Rev. 1.0Aug 6, 2021