- Connects Two High-Speed Asynchronous Buses

- -Up to 5M Bytes/Second DMA on Host System Bus

- -6M Bytes/Second DMA on LAN Adapter

Bus

- Provides Dual-Port DMA and Direct I/O Transfer Between Buses

- Selectable Host System Bus Options

- -808X- or 680XX-Type Bus and Memory Organization

- -8- or 16-Bit Data Bus for 808X-Type Buses

- -Optional Parity Checking

- Provides Direct Control of Latches and Drivers on Host System Bus Interface

- Test Pin for Hi-Z, Module-In-Place Testing

- Single 5-V Supply

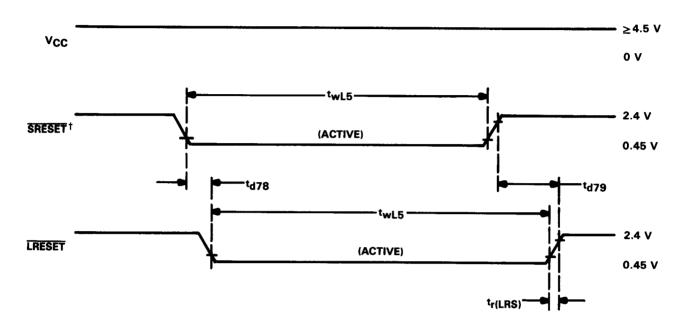

- 100-Pin Ceramic Grid Array Package

- Low-Power Scaled-NMOS Technology

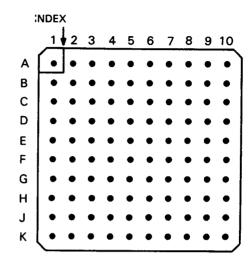

# GB PACKAGE<sup>†</sup> (TOP VIEW)

<sup>†</sup>See pin description table (Page 2) for location and description of all pins.

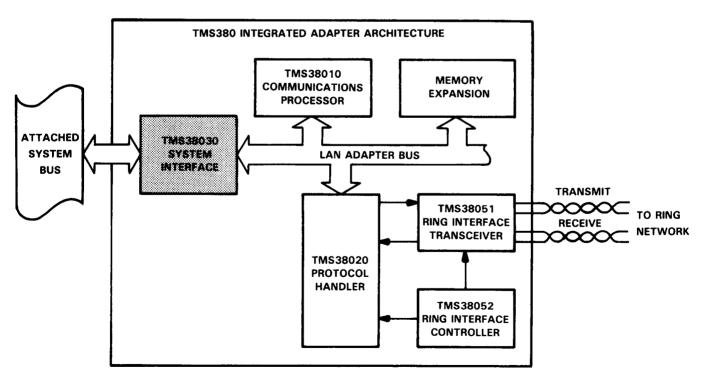

### token ring LAN application diagram

# pin descriptions

| NAME               | PIN  | 1/0 | DESCRIPTION                                                                     |

|--------------------|------|-----|---------------------------------------------------------------------------------|

|                    |      |     | SYSTEM BUS ADDRESS/DATA PINS                                                    |

| SADH0              | . H7 | 1/0 | System address/Data bus - High Byte. SADH0 is the most-significant bit          |

| SADH1              | K10  | 1/0 | and SADH7 is the least-significant bit.                                         |

| SADH2              | J8   | 1/0 |                                                                                 |

| SADH3              | J7   | 1/0 |                                                                                 |

| SADH4              | К6   | 1/0 |                                                                                 |

| SADH5              | J6   | 1/0 |                                                                                 |

| SADH6              | К9   | 1/0 |                                                                                 |

| SADH7              | К8   | 1/0 |                                                                                 |

| SADL0              | J5   | 1/0 | System Address/Data bus — Low Byte. SADL0 is the most-significant bit and SADL7 |

| SADL1              | Н5   | 1/0 | is the least-significant bit.                                                   |

| SADL2              | G5   | 1/0 |                                                                                 |

| SADL3              | К4   | 1/0 |                                                                                 |

| SADL4              | F5   | 1/0 |                                                                                 |

| SADL5              | J4   | 1/0 |                                                                                 |

| SADL6              | H4   | 1/0 |                                                                                 |

| SADL7              | КЗ   | 1/0 |                                                                                 |

| SPH                | K7   | 1/0 | System Parity High Byte                                                         |

| SPL                | K5   | 1/0 | System Parity Low Byte                                                          |

|                    |      |     | SYSTEM BUS CONTROL PINS                                                         |

| SI/M               | Н8   |     | 808X/680XX Mode Select                                                          |

| \$8/ <del>16</del> | Н9   |     | 8/16-Bit Data Bus Select                                                        |

| SRESET             | H10  |     | System Reset                                                                    |

| SCS                | J2   | 1   | Chip Select                                                                     |

| SRS0               | K2   |     | Register Select 0 (MSB)                                                         |

| SRS1               | нз   |     | Register Select 1                                                               |

| SRS2               | G4   | 1   | Register Select 2 (LSB)                                                         |

| SBHE/SRNW          | K1   | 1/0 | Byte High Enable (808X mode)/Read Not Write (680XX mode)                        |

| SWR/SLDS           | H1   | 1/0 | Write Strobe (808X mode)/Lower Data Strobe (680XX mode)                         |

| SRD/SUDS           | G1   | 1/0 | Read Strobe (808X mode)/Upper Data Strobe (680XX mode)                          |

| SRAS/SAS           | G3   | 1/0 | Register Address Strobe (808X mode)/Memory Address Strobe (680XX mode)          |

| SRDY/SDTACK        | J1   | 1/0 | Bus Ready (808X mode)/Data Transfer Acknowledge (680XX mode)                    |

| SALE               | D3   | 0   | Address Latch Enable                                                            |

| SXAL               | D2   | 0   | Extended Address Latch Enable                                                   |

| SBCLK              | E2   |     | System Bus Clock                                                                |

|                    |      |     | SYSTEM BUS DRIVER/RECEIVER CONTROL PINS                                         |

| SDDIR              | C2   | 0   | Data Direction                                                                  |

| SDBEN              | C1   | 0   | Data Bus Enable                                                                 |

| SOWN               | E5   | 0   | System Bus Owned                                                                |

# pin descriptions (continued)

| NAME       | PIN      | I/O | DESCRIPTION                                                                         |

|------------|----------|-----|-------------------------------------------------------------------------------------|

|            |          |     | SYSTEM BUS ARBITRATION/DMA CONTROL PINS                                             |

| SHRQ/SBRQ  | H2       | 0   | Hold Request (808X mode)/Bus Request (680XX mode)                                   |

| SHLDA/SBGR | F1       | 1   | Hold Acknowledge (808X mode)/Bus Grant (680XX mode)                                 |

| SBBSY      | G2       | 1   | Bus Busy                                                                            |

| SBRLS      | B2       | 1   | Bus Release                                                                         |

| SBERR      | F2       | - 1 | Bus Error                                                                           |

|            |          |     | SYSTEM BUS INTERRUPT CONTROL PINS                                                   |

| SINTR/SIRQ | D4       | 0   | Interrupt Request (808X mode)/Interrupt Request (680XX mode)                        |

| SIACK      | D1       | - 1 | Interrupt Acknowledge                                                               |

|            | <u> </u> |     | LAN ADAPTER BUS ADDRESS/DATA PINS                                                   |

| LAD0       | B8       | I/O | LAN Adapter Bus Address/Data Bus. LADO is the most-significant bit and LAD15 is the |

| LAD1       | A8       | 1/0 | least-significant bit.                                                              |

| LAD2       | C7       | 1/0 |                                                                                     |

| LAD3       | B7       | 1/0 |                                                                                     |

| LAD4       | A7       | 1/0 |                                                                                     |

| LAD5       | D6       | 1/0 |                                                                                     |

| LAD6       | C6       | 1/0 |                                                                                     |

| LAD7       | В6       | 1/0 |                                                                                     |

| LAD8       | А3       | 1/0 |                                                                                     |

| LAD9       | A2       | 1/0 |                                                                                     |

| LAD10      |          |     |                                                                                     |

| LAD11      | A5       | 1/0 |                                                                                     |

| LAD12      | B4       | 1/0 |                                                                                     |

| LAD13      | В3       | 1/0 |                                                                                     |

| LAD14      | A1       | 1/0 |                                                                                     |

| LAD15      | C4       | 1/0 |                                                                                     |

| LPH        | A6       | 1/0 | LAN Adapter Bus Parity High Byte                                                    |

| LPL        | A4       | I/O | LAN Adapter Bus Parity Low Byte                                                     |

|            |          |     | LAN ADAPTER BUS CONTROL PINS                                                        |

| LBCLK1     | B10      |     | LAN Adapter Bus Clock 1                                                             |

| LBCLK2     | C10      |     | LAN Adapter Bus Clock 2                                                             |

| LAL        | D9       | 1/0 | LAN Adapter Bus Address Latch Enable                                                |

| LI/D       | D8       | 1   | LAN Adapter Bus Instruction/Data Bus Status Code                                    |

| LEN        | C9       | 1/0 | LAN Adapter Bus Data Enable                                                         |

| LR/W       | E7       | 1/0 | LAN Adapter Bus Read/Not Write                                                      |

| LBRDY      | A9       | - 1 | LAN Adapter Bus Ready                                                               |

# pin descriptions (concluded)

| NAME            | PIN                                 | I/O | DESCRIPTION                                          |  |  |  |  |

|-----------------|-------------------------------------|-----|------------------------------------------------------|--|--|--|--|

|                 |                                     |     | LAN ADAPTER BUS INTERRUPT PINS                       |  |  |  |  |

| LIRQINO         | G10                                 | 1   | LAN Adapter Bus Interrupt Request 0 Input            |  |  |  |  |

| LIRQIN1         | F7                                  | 1   | LAN Adapter Bus Interrupt Request 1 Input            |  |  |  |  |

| LIRQIN2         | F8                                  | 1   | LAN Adapter Bus Interrupt Request 2 Input            |  |  |  |  |

| LIRQOUTO        | F6                                  | 0   | LAN Adapter Bus Interrupt Request Output 0           |  |  |  |  |

| LIRQOUT1        | F10                                 | 0   | LAN Adapter Bus Interrupt Request Output 1           |  |  |  |  |

| LIRQOUT2        | F9                                  | 0   | LAN Adapter Bus Interrupt Request Output 2           |  |  |  |  |

| LRESET          | G9                                  | 0   | LAN Adapter Bus Reset                                |  |  |  |  |

|                 |                                     |     | LAN ADAPTER BUS ARBITRATION PINS                     |  |  |  |  |

| LBRQS           | LBRQS A10 O LAN Adapter Bus Request |     |                                                      |  |  |  |  |

| LBGRS           | C8                                  | ı   | LAN Adapter Bus Grant                                |  |  |  |  |

|                 | <u> </u>                            |     | MISCELLANEOUS PINS                                   |  |  |  |  |

| CHPTST          |                                     |     |                                                      |  |  |  |  |

| TEST            | G8                                  | 1   | Module-in-Place Test Mode Select                     |  |  |  |  |

| V <sub>BB</sub> | D10                                 |     | This pin is reserved and should be left unconnected. |  |  |  |  |

| NC              | E6                                  |     | This pin is reserved and should be left unconnected. |  |  |  |  |

|                 |                                     |     | POWER PINS                                           |  |  |  |  |

| Vcc             | J3                                  |     | 5-V power supply (All pins must be connected.)       |  |  |  |  |

| Vcc             | J9                                  |     |                                                      |  |  |  |  |

| Vcc             | E9                                  |     |                                                      |  |  |  |  |

| Vcc             | D7                                  |     |                                                      |  |  |  |  |

| Vcc             | D5                                  |     |                                                      |  |  |  |  |

| Vcc             | E3                                  |     |                                                      |  |  |  |  |

| V <sub>SS</sub> | C3                                  |     | Ground pins (All pins must be connected.)            |  |  |  |  |

| V <sub>SS</sub> | E4                                  |     |                                                      |  |  |  |  |

| V <sub>SS</sub> | E1                                  |     |                                                      |  |  |  |  |

| V <sub>SS</sub> | F3                                  |     |                                                      |  |  |  |  |

| Vss             | F4                                  |     |                                                      |  |  |  |  |

| V <sub>SS</sub> | H6                                  |     |                                                      |  |  |  |  |

| Vss             | G6                                  |     |                                                      |  |  |  |  |

| Vss             | G7                                  |     |                                                      |  |  |  |  |

| Vss             | E8                                  |     |                                                      |  |  |  |  |

| Vss             | E10                                 |     |                                                      |  |  |  |  |

| Vss             | B9                                  |     |                                                      |  |  |  |  |

| Vss             | C5                                  |     |                                                      |  |  |  |  |

| V <sub>SS</sub> | B1                                  |     |                                                      |  |  |  |  |

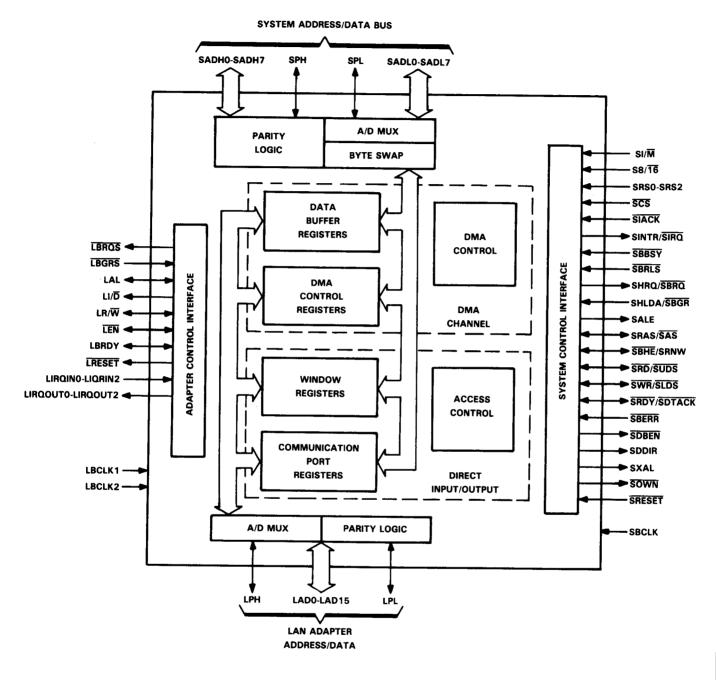

### functional block diagram<sup>†</sup>

<sup>†</sup>For signal names separated by a slash (/), the first signal name given is for the 808X mode and the second signal name is for the 680XX mode.

### description

The TMS38030 System Interface (SIF) connects two high-speed buses and provides DMA and direct I/O (DIO) transfer between these buses. The TMS38030 features a dual-port DMA channel and DIO registers that connect a host system bus transferring data up to 5 megabytes per second to the LAN Adapter bus operating at a 6 megabyte per second transfer rate. For added flexibility the host system bus can be pinstrap selected to either an 808X-type or 680XX-type bus allowing the designer to choose the bus configuration which best meets his application. When in 808X mode, the TMS38030 automatically handles byte swapping to meet the requirements of the 808X processor memory conventions. Four DIO registers on the host system bus are available for handshaking between the host system CPU and the LAN Adapter CPU. Full control of the TMS38030 is provided by nine 16-bit registers accessible from the LAN Adapter bus interface. Control lines on the host system bus interface reduce interface logic requirements by providing direct control of latches and drivers.

The TMS38030, when coupled with the TMS38010 Communications Processor, the TMS38020 Protocol Handler, and the TMS38051 and TMS38052 Ring Interface Circuits, forms a complete integrated Token Ring local area network adapter fully compatible with IEEE Std 802.5-1985 Token Ring Access and Physical Layer Specifications for Token Ring Networks.

#### architecture

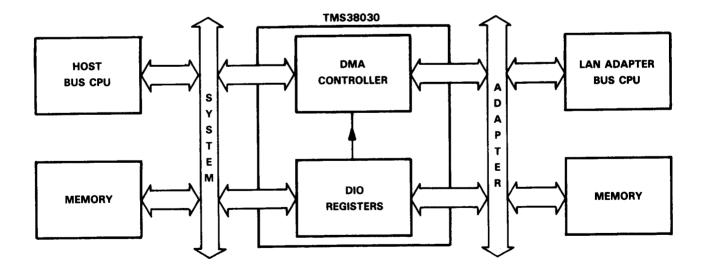

The TMS38030 may be conceptually viewed as shown in Figure 1. The DMA controller differs from conventional DMA controllers in that DMA transfers occur from the memory of one bus to the memory of another bus versus DMA transfers on the same bus. The two buses are independent of each other in that timing of one bus may be asynchronous to the timing of the other. A direct I/O (DIO) (or memory-mapped I/O) interface on the host system bus may be used as a low-level handshake between the two CPUs as well as for posting interrupts from one CPU to the other.

The TMS38030 also contains an interrupt priority encoder for prioritizing up to seven interrupt levels for presentation to the LAN Adapter bus CPU (TMS38010 Communications Processor).

FIGURE 1. TMS38030 DMA CONTROL-CONCEPTUAL REPRESENTATION

#### system bus interface

#### interface modes

The TMS38030 system-side interface may be pin strap selected, via the  $SI/\overline{M}$  pin, to provide pin personalities compatible with 808X-type and 680XX-type processor buses. When the  $SI/\overline{M}$  pin is tied high, the system interface pins assume 808X-type personalities. When the  $SI/\overline{M}$  pin is tied low, the system interface pins assume 680XX-type personalities. The system designer has the option to choose the bus type which best supports his intended hardware environment.

The S8/ $\overline{16}$  pin may be used to select either an 8-bit or 16-bit wide system data bus when the SI/ $\overline{M}$  pin is strapped high (808X mode). When 8-bit mode is selected, the SI/ $\overline{M}$  pin must not be strapped low (680XX mode). When in 8-bit mode, the data is transferred on the SADLO-SADL7 pins while the SADHO-SADH7 pins are either ignored during data read or high impedance during data write.

### direct I/O registers

Located on the system bus are four 16-bit registers. One register, called the Interrupt Register, is dedicated to bit-level status and control information handshaking between the host system processor and the LAN Adapter bus processor (the TMS38010 Communications Processor). The remaining three registers are used by the host system processor to access memory locations within the LAN Adapter bus address space. These registers are the Address Register, Data Register, and Data Register with Autoincrement (of the Address Register). These registers are selected by the SRS0-SRS2 register select pins as shown in Table 1.

TABLE 1. TMS38030 SYSTEM BUS REGISTERS

| SRS0 | SRS1 | SRS2   | REGISTER                         |

|------|------|--------|----------------------------------|

| L    | L    | Note 1 | Data Register                    |

| L    | Н    | Note 1 | Data Register with Autoincrement |

| Н    | L    | Note 1 | Address Register                 |

| Н    | Н    | Note 1 | Interrupt Register               |

NOTE 1: SRS2 is used to address the upper/lower byte of the register when in 8-bit mode (S8/16 high).

#### interrupt register

The Interrupt Register is used to pass bit-level control and status information between the host system processor and the LAN Adapter processor (TMS38010). The Interrupt Register is also used to clear the TMS38030-to-host interrupt (SINTR/SIRQ) and to post interrupts to the LAN Adapter bus CPU through the TMS38030 interrupt prioritizer. The bit functions of the Interrupt Register are shown in Table 2.

TABLE 2. INTERRUPT REGISTER BIT FUNCTIONS - SYSTEM SIDE

| BITS    | READ/WRITE | FUNCTION                                                                                  |  |  |

|---------|------------|-------------------------------------------------------------------------------------------|--|--|

| O (MSB) | Write      | 1 = set bit and interrupt LAN Adapter Bus CPU.                                            |  |  |

|         | 1          | 0 = no effect.                                                                            |  |  |

|         | Read       | Read value of bit.                                                                        |  |  |

| 1-7     | Write      | 1 = sets bit value to 1. 0 = no effect.                                                   |  |  |

|         | Read       | Read value of bit.                                                                        |  |  |

| 8       | Write      | $1 = \text{no effect. } 0 = \text{reset. SINTR}/\overline{\text{SIRQ}}$ to inactive high. |  |  |

| 9-15    | Write      | No effect. These bits cannot be set/reset by the host                                     |  |  |

|         |            | processor.                                                                                |  |  |

|         | Read       | Read value of bits.                                                                       |  |  |

### TMS38030 SYSTEM INTERFACE

#### address register

The Address Register provides a pointer into LAN Adapter bus memory address space with which the host system processor may access data through either the Data Register or the Data Register with Autoincrement. Bits 5 through 14 may be set to any value by the host processor by writing the appropriate value to this register. Bits 0-4 and bit 15 may only be set/reset by the LAN Adapter bus CPU. This allows the LAN Adapter bus CPU to control host access to the LAN Adapter bus memory space within a 2K-byte window as defined by the setting of bits 0 through 4. Bit 15 is always set to zero as all data transfers on the LAN Adapter bus are 16-bit transfers (even addresses).

#### data registers

Two data registers provide read/write capability to the LAN Adapter bus memory address location pointed to by the Address Register. The host processor does not access these locations directly however, the TMS38030 performs LAN Adapter bus DMA operations to read or write the memory location as necessary.

When read, the Data Register returns the value found in the memory location pointed to by the Address Register. The TMS38030 will perform a DMA read of this location when this occurs. Writing to the Data Register will cause the data to be written to the LAN Adapter bus memory location as pointed to by the Address Register when the IOWEN bit of the SIF Control (SIFCTL) Register is set to one. The TMS38030 will perform a DMA write to this location when this occurs.

The Data Register with Autoincrement behaves identically to the Data Register; however, the Address Register is automatically incremented by two following each access (post increment). This feature is useful for the passing of parameter tables to sequential memory locations within the LAN Adapter bus memory space.

#### direct input/output

Read and write cycles to the direct I/O registers cannot occur simultaneously with DMA operation on the system bus because they share the same physical interface pins. However, a DIO access occurring between two successive bus cycles of a DMA cycle will not disrupt any DMA conditions existing within the TMS38030.

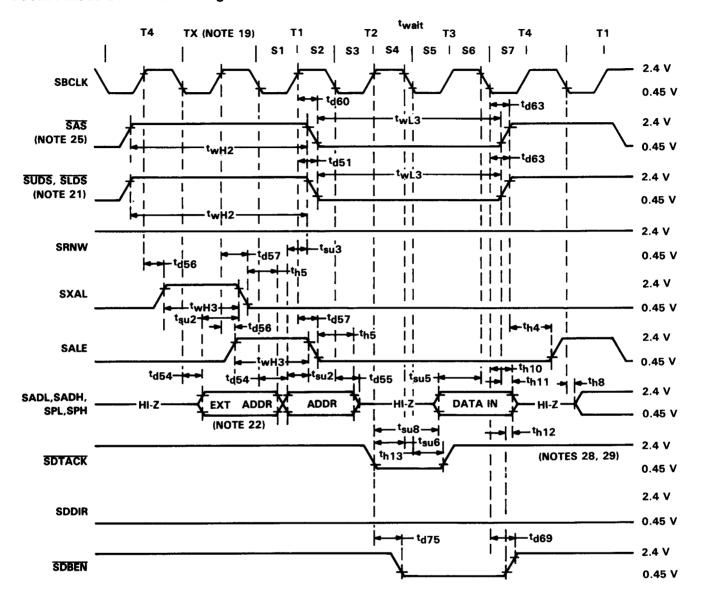

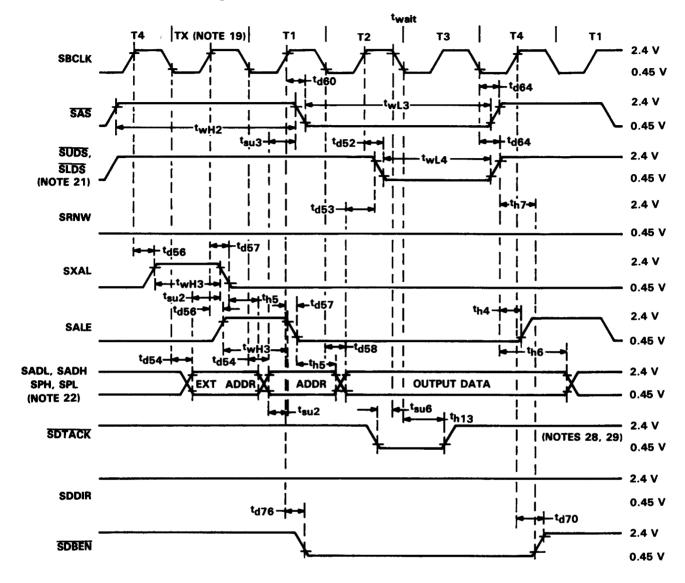

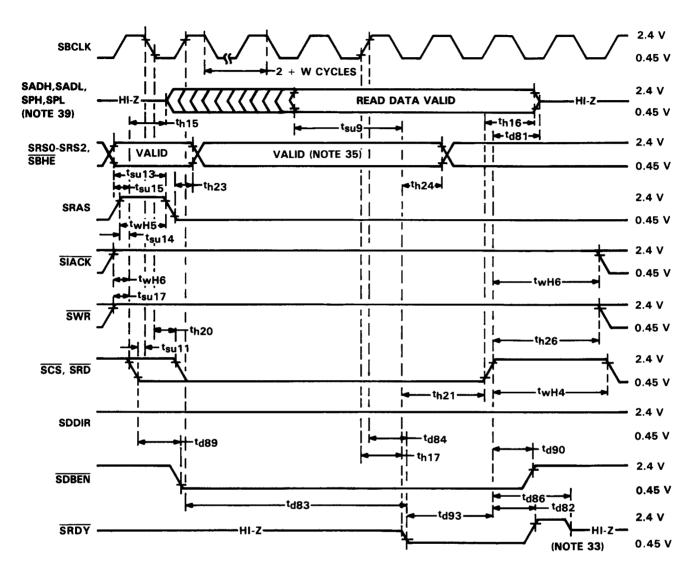

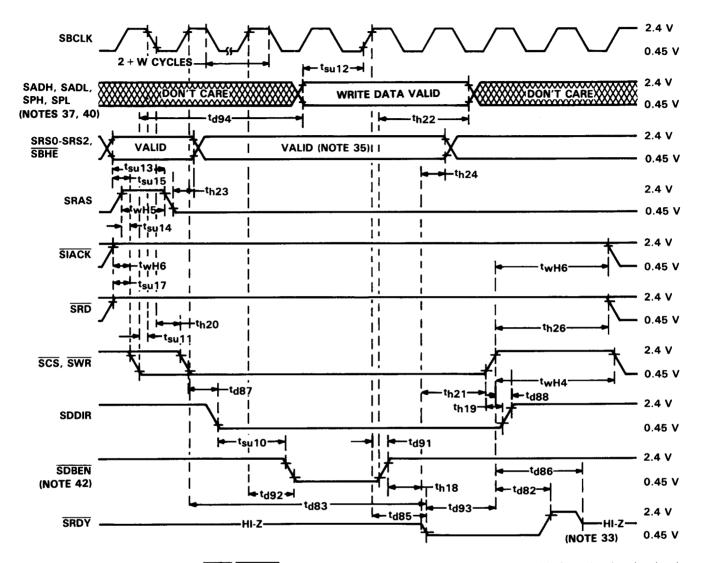

#### direct memory access

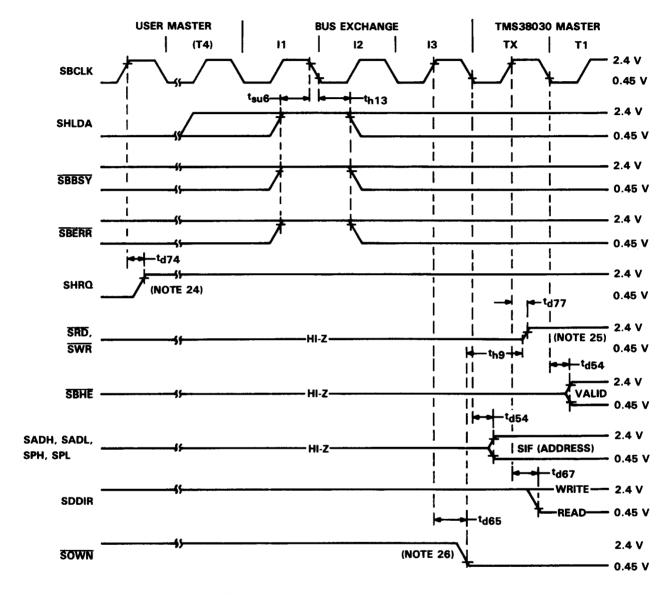

The direct memory access (DMA) channel of the system bus interface provides a full 24 bits of address with which to access up to 16 megabytes of system memory. The throughput capability of the DMA channel is matched to that of the host system through a host system supplied bus clock (SBCLK). The maximum DMA transfer rate corresponds to one word per four user system clock periods. DMA on the system bus may occur concurrently and asynchronously to DMA on the LAN Adapter bus.

When configured in 808X mode, the TMS38030 performs automatic byte swapping on data passed between the LAN Adapter bus and the host system bus. This is to compensate for the differing byte ordering conventions between the 808X-type processor and the LAN Adapter bus CPU. The LAN Adapter bus memory organization defines byte 0 of a 16-bit memory word to be the most-significant byte and byte 1 to be the least-significant. The 808X-type processor defines byte 0 of a 16-bit memory word to be the least-significant byte and byte 1 to be the most-significant. Byte swapping automatically corrects for this difference in convention. Byte swapping is not performed on DIO accesses.

The system bus DMA is controlled by the LAN Adapter bus CPU through the registers resident on the Adapter bus. The system bus DMA may be configured for system bus starting address, DMA length, burst or cycle-steal mode of operation and parity checking on DMA reads.

Since only 16 bits of address can be output at any instant on the 16 address/data pins, the 8 most-significant address bits must be multiplexed onto the address/data pins. These are called the extended address bits. Two separate latch enable signals (SALE and SXAL) are provided for the demultiplexing of the address. The extended address portion is updated only when the TMS38030 increments an address such that a carry out from the low-order 8 bits is generated. The updating of the extended address is done during an extra phase of the system bus memory transfer cycle. This extra phase is termed the TX cycle. For systems only requiring 16-bits of address, the extended address latches are not required. The TMS38030 performs a TX cycle every time it acquires the system bus. In cycle steal mode, then, the TMS38030 will always perform a TX cycle; in burst mode, the TMS38030 will perform a TX cycle on the first memory cycle and thereafter only when the most-significant 16 bits of address are changed due to a carry propagated from the lower 8 bits. Detailed timing of system DMA operations for both 808X mode and 680XX mode may be found in the Electrical Specifications.

# LAN adapter bus interface

The LAN Adapter bus interface provides the ability of the TMS38030 to transfer data between the LAN Adapter bus environment and the system bus. This high-speed bus is used by the TMS380 family to connect the TMS38010 Communications Processor and TMS38020 Protocol Handler. In expanded configurations, the LAN Adapter bus can interface to expansion memory. The timing of LAN Adapter bus memory mapped I/O and direct memory access cycles is provided in the Electrical Specifications.

# LAN Adapter bus registers

The TMS38030 contains nine registers accessible from the LAN Adapter bus side. These registers are used to control the DMA operation on the system bus side, the DMA operation on the LAN Adapter bus side, direct I/O for the system bus side, and the system interrupt vector driven onto the system bus side during an interrupt acknowledge cycle. These registers, their function and LAN Adapter bus memory location are shown in Figure 2.

| [       | BITS    |        |  |  |

|---------|---------|--------|--|--|

| ADDRESS | 0 7     | 8 15   |  |  |

| >0080   | SIF     | CTL    |  |  |

| >0082   | SIF     | ACT    |  |  |

| >0084   | SIF     | INT    |  |  |

| >0086   | SIFADR  |        |  |  |

| >0088   | SDM     | ALEN   |  |  |

| >008A   | 00      | SDMAX  |  |  |

| >008C   | SDMAH   | SDMAL  |  |  |

| >008E   | LDMAADR |        |  |  |

| >0090   | 00      | SIFVEC |  |  |

DESCRIPTION

SYSTEM INTERFACE CONTROL

SYSTEM INTERFACE ACTIVITY

INTERRUPT REGISTER

SYSTEM DIO ADAPTER BUS ADDRESS

SYSTEM DMA LENGTH

SYSTEM ADDRESS EXTENDED BYTE

SYSTEM ADDRESS HIGH/LOW BYTES

ADAPTER BUS DMA ADDRESS

SYSTEM INTERRUPT VECTOR

FIGURE 2. TMS38030 LAN ADAPTER BUS REGISTERS

### SIFCTL register

The SIFCTL register controls all TMS38030 peripheral functions. Certain values are loaded to the bits of SIFCTL when the LAN Adapter bus CPU writes to address >0080. The current value of the bits are returned by reading the word at this location. Changes made to DMADIR, DMABURST, SPIEN, and SLPIEN bits have no effect on DMA operations already in progress. Such changes affect subsequent DMA operation. All bits of SIFCTL are set to zero when SRESET is activated. The bits of SIFCTL are summarized in Table 3.

**TABLE 3. SIFCTL REGISTER BIT FUNCTIONS**

| BIT  | NAME     | DESCRIPTION                    |

|------|----------|--------------------------------|

| 0    | DMADIR   | System DMA Direction           |

| 1    | DMAENB   | System DMA Enable              |

| 2    | DMABURST | System DMA Burst Mode          |

| 3    | DMAHALT  | System DMA Halt                |

| 4    | DMAIEN   | System DMA Interrupt Enable    |

| 5    | SPIEN    | System Parity Interrupt Enable |

| 6    | SPTST    | System Parity Test             |

| 7    | SLPIEN   | System Local Parity Enable     |

| 8    | IOWEN    | DIO Write Enable               |

| 9-15 |          | Reserved                       |

### SIFACT register

The SIFACT register contains the system bus error flag, LAN Adapter bus and system bus parity error flags, and the DMA halt interrupt request bit. All bits of SIFACT are reset to zero at system reset. Table 4 summarizes the bit functions of the SIFACT register.

**TABLE 4. SIFACT REGISTER BIT FUNCTIONS**

| BIT  | NAME  | DESCRIPTION                                    |  |  |

|------|-------|------------------------------------------------|--|--|

| 0    |       | Reserved                                       |  |  |

| 1    |       | Reserved                                       |  |  |

| 2    | DIRQ  | System DMA Halt Interrupt Request              |  |  |

| 3    | SPE   | System Parity Error - DIO                      |  |  |

| 4    | SDPE  | System Parity Error - DMA                      |  |  |

| 5    | SDBE  | System DMA Bus Error                           |  |  |

| 6    | LPEXM | LAN Adapter Bus Parity Error - External Master |  |  |

| 7    | LPESM | LAN Adapter Bus Parity Error - TMS38030 Master |  |  |

| 8-15 | Ī     | Reserved                                       |  |  |

### SIFINT register

The SIFINT register is the Interrupt register which is accessible from both the host system bus side and the LAN Adapter bus side. However, the restrictions on setting/clearing these bits is different than when accessed from the LAN Adapter bus side. These are illustrated in Table 5. Table 2 illustrates the function of these bits as viewed from the host system bus side.

TABLE 5. INTERRUPT REGISTER BIT FUNCTIONS - LAN ADAPTER BUS SIDE

| BITS    | READ/WRITE | FUNCTION                                 |

|---------|------------|------------------------------------------|

| O (MSB) | Write      | 1 = no effect. 0 = clear interrupt.      |

|         | Read       | Read value of bit.                       |

| 1-7     | Write      | 1 = no effect. 0 = reset bit to zero.    |

|         | Read       | Read value of bit.                       |

| 8       | Write      | 1 = set SINT/SIRQ active. 0 = no effect. |

| 9-15    | Write      | Modify current contents.                 |

|         | Read       | Read value of bits.                      |

### SIFADR Register

The SIFADR (SIF Address) register is the Address register which is accessible from both the host system bus and the LAN Adapter bus. Bits 0-4 and bit 15 can only be set/reset from the LAN Adapter bus side of the TMS38030. The remaining bits (5-14) can only be set/reset from the host system side of the TMS38030.

#### **SDMALEN Register**

The SDMALEN (System DMA length) register contains the byte count length of a DMA transfer. A maximum length transfer can be 65,535 bytes. A zero loaded into SDMALEN will limit DMA to transferring zero bytes.

#### SDMAX, SDMAH, and SDMAL Registers

These three register fields contain the 24-bit system address where DMA is to begin. SDMAX contains the most-significant eight bits, SDMAH the middle eight bits, and SDMAL the least-significant eight bits.

#### LDMAADR Register

The LDMAADR (LAN Adapter bus DMA address) register contains the 16-bits of LAN Adapter bus address location where DMA is to begin. This address space is always in the data space of the LAN Adapter bus (the TMS38030 always drives  $LI/\overline{D}$  low). The DMA length is controlled by SDMALEN.

#### SIFVEC Register

The SIFVEC (SIF vector) register contains the 8-bit interrupt vector which is output onto the system data bus during an interrupt acknowledge cycle.

#### interrupts

The TMS38030 contains an interrupt prioritizer for other devices on the LAN Adapter bus for presentation of interrupts to the TMS38010 Communications Processor. Other devices assert an interrupt on the TMS38030's LIRQIN0 through LIRQIN2 (LAN Adapter Bus Request In) inputs. The TMS38030 prioritizes the requests and presents an interrupt priority code to the TMS38010 on output pins LIRQOUT0 through LIRQOUT2. The relation between the levels on LIRQIN0 through LIRQIN2 and priority level is given in Table 6.

#### **TABLE 6. INTERRUPT REQUEST CODES**

| LIRQINO | LIRQIN1 | LIRQIN2 | MEANING                   |

|---------|---------|---------|---------------------------|

| 0       | 0       | 0       | Level-1 Interupt Request  |

| 0       | 0       | 1       | Level-2 Interrupt Request |

| 0       | 1       | 0       | Level-3 Interrupt Request |

| 0       | 1       | 1       | Level-4 Interrupt Request |

| 1       | 0       | 0       | Level-5 Interrupt Request |

| 1       | О       | 1       | Level-6 Interrupt Request |

| 1       | 1       | 0       | Level-7 Interrupt Request |

| 1       | 1       | 1       | No request                |

#### TMS38030 Generated Interrupts

The TMS38030 will assert an interrupt on the LIRQOUT0 through LIRQOUT2 pins as follows:

- 1. LAN Adapter bus or system bus parity errors are asserted on level 2.

- 2. The system DMA complete interrupt is asserted on level 6.

- 3. The interrupt request from the system bus (MSB of the interrupt register is set to one) is asserted on level 7.

#### test mode

The TMS38030 features a module-in-place test mode for board level testing with the TMS38030 in circuit. This facilitates testing by bed-of-nails testers. This test mode is enabled by tying the TEST pin to ground. This has the effect of driving all outputs of the TMS38030 to a high-impedance state. When not used for testing purposes, this pin should be left unconnected. An internal pullup drives the TEST pin high when not externally connected.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 2)                  | 7 V |

|---------------------------------------------------|-----|

| Input voltage range                               |     |

| Output voltage range                              |     |

| Operating free-air temperature range (see Note 3) |     |

| Storage temperature range                         |     |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 2. Voltage values are with respect to VSS.

3. Devices are tested in an environment in excess of 70 °C to guarantee operation at 70 °C. Case temperatures should be maintained at or below 85 °C.

# recommended operating conditions

|                  |                                                                             |                                                                                                                                                | MIN | NOM | MAX   | UNIT       |

|------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------------|

| VCC              | Supply voltage                                                              |                                                                                                                                                | 4.5 | 5   | 5.5   | V          |

| VSS              | Supply voltage                                                              |                                                                                                                                                | 0   | 0   | 0     | ٧          |

|                  |                                                                             | TEST                                                                                                                                           | Vcc |     |       | V          |

| VIH              | High-level                                                                  | LBCLK1, LBCLK2                                                                                                                                 | 3.8 |     |       | ٧          |

|                  | input voltage                                                               | All other inputs                                                                                                                               | 2   |     |       |            |

|                  |                                                                             | TEST                                                                                                                                           |     |     | VSS   | ٧          |

| VIL              | Low-level                                                                   | · LBCLK1, LBCLK2                                                                                                                               |     |     | 0.6   | ٧          |

|                  | input voltage                                                               | All other inputs                                                                                                                               |     |     | 0.8   | ٧          |

| ЮН               | High-level<br>output current                                                | SBHE/SRNW, SWR/SLDS, SRD/SUDS, SRAS/SAS, SRDY/SDTACK, SADHO-SADH7, SADLO-SADL7, SPH, SPL SHRQ/SBRQ, SINTR/SIRQ, SDBEN, SDDIR, SALE, SXAL, SOWN |     |     | 0.4   | mA         |

| output duritorit | ·                                                                           | LBRQS, LRESET, LIRQOUTO-LIRQOUT2, LAL LEN, LI/D, LR/W, LADO-LAD15, LPH, LPL                                                                    |     |     | 0.15  | mA         |

|                  | SBHE/SRNW, SWR/SLDS, SRD/SUDS, SRAS/SAS, SRDY/SDTACK, SHRQ/SBRQ, SINTR/SIRQ | SRD/SUDS, SRAS/SAS,                                                                                                                            |     |     | - 2   | mA         |

|                  |                                                                             | SADHO-SADH7, SADLO-SADL7,<br>SPH, SPL, SDDIR                                                                                                   |     |     | - 2.5 | mA         |

| lOL              | Low-level output current                                                    | SALE, SXAL                                                                                                                                     |     |     | - 3.5 | m/         |

|                  | output current                                                              | SDBEN                                                                                                                                          |     |     | - 5   | m/         |

|                  |                                                                             | SOWN                                                                                                                                           |     |     | - 5.5 | m.A        |

|                  |                                                                             | LBRQS, LRESET, LIRQOUTO-LIRQOUT2, LAL LEN, LI/D, LR/W, LADO-LAD15, LPH, LPL                                                                    |     |     | - 1.7 | m <i>A</i> |

| CL               | Load capacitance                                                            | All outputs                                                                                                                                    |     |     | 100   | pF         |

| TA               | Operating free-air temperate                                                |                                                                                                                                                | 0   |     | 70    | °C         |

NOTE 3: Devices are tested in an environment in excess of 70 °C to guarantee operation at 70 °C. Case temperatures should be maintained at or below 85 °C.

# electrical characteristics over full range of recommended operating conditions

|                 | PARA                                                                                                                                                                                                                         | AMETER                                                                       | TEST<br>CONDITIONS                                  | MIN | TYP | MAX   | UNIT |    |     |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-------|------|----|-----|

| Vон             | High-level<br>output voltage                                                                                                                                                                                                 | All outputs                                                                  | V <sub>CC</sub> = 4.5 V,<br>I <sub>OH</sub> = max   | 2.4 |     |       | ٧    |    |     |

| V <sub>OL</sub> | Low-level output voltage                                                                                                                                                                                                     | All outputs                                                                  | $V_{CC} = 4.5 V,$ $I_{OL} = max$                    |     |     | 0.45  | ٧    |    |     |

| Юн              | BBHE/SRNW, SWR/SLDS, SRD/SUDS, SRAS/SAS, SRDY/SDTACK, SADHO-SADH7, SADLO-SADL7, SPH, SPL, SHRQ/SBRQ SINTR/SIRQ, SDBEN, SDDIR, SALE, SXAL, SOWN  LBRQS, LRESET, LIRQOUTO-LIRQOUT2, LAL, LEN, LI/D, LR/W, LADO-LAD15, LPH, LPL | V <sub>CC</sub> = 4.5 V,                                                     |                                                     |     |     | 400   | μΑ   |    |     |

|                 |                                                                                                                                                                                                                              |                                                                              | LIRQOUTO-LIRQOUT2, LAL,<br>LEN, LI/D, LR/W,         |     |     |       |      |    | 150 |

|                 |                                                                                                                                                                                                                              | SBHE/SRNW, SWR/SLDS, SRD/SUDS, SRAS/SAS, SRDY/SDTACK, SHRQ/SBRQ, SINTR/SIRQ  |                                                     |     |     |       | - 2  | mA |     |

|                 |                                                                                                                                                                                                                              | SADHO-SADH7, SADLO-SADL7,<br>SPH, SPL, SDDIR                                 | V <sub>CC</sub> = 4.5 V,                            |     |     | - 2.5 | mA   |    |     |

| IOL             | Low-level output current                                                                                                                                                                                                     | SALE, SXAL                                                                   | $V_{OL} = 4.5 \text{ V},$ $V_{OL} = 0.45 \text{ V}$ |     |     | -3.5  | mA   |    |     |

|                 | output current                                                                                                                                                                                                               | SDBEN                                                                        | ] *0[ = 0.43 * [                                    |     |     | - 5   | mA   |    |     |

|                 |                                                                                                                                                                                                                              | SOWN                                                                         |                                                     |     |     | - 5.5 | mA   |    |     |

|                 |                                                                                                                                                                                                                              | LBRQS, LRESET, LIRQOUTO-LIRQOUT2, LAL, LEN, LI/D, LR/W, LADO-LAD15, LPH, LPL |                                                     |     |     | - 1.7 | mA   |    |     |

Continued next page.

### electrical characteristics over full range of recommended operating conditions (concluded)

|                  | PAR                                                          | AMETER                                                            | TEST<br>CONDITIONS                                      | MIN   | TYP | MAX   | UNIT |

|------------------|--------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------|-------|-----|-------|------|

| <sup>I</sup> OZL | Off-state (high-imp<br>output current with<br>(outputs only) | edance state)<br>n low-level vołtage applied                      | V <sub>O</sub> = 0.45 V                                 |       |     | - 20  | μΑ   |

| lоzн             | Off-state (high-imp<br>output current with<br>(outputs only) | edance state)<br>high-level voltage applied                       | V <sub>O</sub> = 2.4 V                                  |       |     | 20    | μΑ   |

|                  |                                                              | TEST, LIRQINO-LIRQIN2                                             |                                                         |       |     | - 700 | μΑ   |

| lir              | Low-level input current                                      | SBHE/SRNW, SWR/SLDS,<br>SRD/SUDS, SRAS/SAS,<br>SRDY/SDTACK, SBSSY | V <sub>I</sub> = 0.45 V                                 |       |     | - 450 | μΑ   |

|                  |                                                              | All other inputs and I/O's                                        |                                                         |       |     | – 2C  | μΑ   |

| ļH.              | High-level input current                                     | SBHE/SRNW, SWR/SLDS,<br>SRD/SUDS, SRAS/SAS,<br>SRDY/SDTACK, SBBSY | V <sub>I</sub> = 2.4 V                                  | - 100 |     |       | μΑ   |

|                  |                                                              | All other inputs and I/O's                                        | VI = VCC                                                |       |     | 20    | μΑ   |

|                  |                                                              |                                                                   | $V_{CC} = 5 V,$ $T_A = 25 ^{\circ}C$                    |       | 190 |       | mA   |

| Icc              | Supply current                                               |                                                                   | $V_{CC} = 5.5 V,$ $T_A = 0 ^{\circ}C$                   |       |     | 240   | mA   |

|                  |                                                              |                                                                   | $V_{CC} = 5.5 \text{ V},$ $T_{C} = 85 ^{\circ}\text{C}$ |       | ·   | 200   | mA   |

|                  | L                                                            | SBCLK                                                             | f = 1 MHz,                                              |       |     | 25    | pF   |

| Cl               | Input                                                        | LBCLK1, LBCLK2 (Note 4)                                           | All other inputs                                        |       |     | 20    | pF   |

|                  | capacitance                                                  | All other inputs                                                  | at O                                                    |       |     | 15    | pF   |

NOTE 4: Input capacitance difference between LBCLK1 and LBCLK2 will not exceed 3 pF.

### LAN ADAPTER BUS CLOCK PARAMETERS

### timing requirements over recommended supply voltage range and operating free-air temperature range

|                     | PARAMETER                                                    | MIN     | MAX    | UNIT |

|---------------------|--------------------------------------------------------------|---------|--------|------|

| t <sub>C</sub> (LA) | LAN adapter bus cycle time (Note 5)                          | 333     | 333.7  |      |

| <sup>t</sup> d1     | Delay time, LBCLK2 low to LBCLK2 no longer low in next cycle | 40 – 2  | 4Q + 2 |      |

| d2                  | Delay time, LBCLK2 rise to LBCLK2 high in next cycle         |         | 4Q+9   |      |

| td3                 | Delay time, LBCLK2 no longer low to LBCLK1 no longer low     | Q-3     | Q+3    |      |

| td4                 | Delay time, LBCLK2 rise to LBCLK1 high                       |         | Q+9    |      |

| d5                  | Delay time, LBCLK2 no longer low to LBCLK2 no longer high    | 2Q – 2  | 2Q + 7 |      |

| d6                  | Delay time, LBCLK2 rise to LBCLK2 low                        |         | 2Q+12  | ns   |

| d7                  | Delay time, LBCLK2 no longer low to LBCLK1 no longer high    | 3Q - 15 | 3Q – 1 |      |

| t <sub>d8</sub>     | Delay time, LBCLK2 rise to LBCLK1 low                        |         | 30     |      |

| td9                 | Delay time, LBCLK1 low to LBCLK2 high                        | Q       |        |      |

| <sup>1</sup> d10    | Delay time, LBCLK2 high to LBCLK1 high                       | Q-4     |        |      |

| d11                 | Delay time, LBCLK1 high to LBCLK2 low                        | Q-4     |        |      |

| <sup>t</sup> d12    | Delay time, LBCLK2 low to LBCLK1 low                         | Q-16    |        |      |

NOTES: 5. The LAN Adapter bus cycle time is 333.3 ns  $\pm 0.1\%$ . This value shall be used for calculations requiring the time between successive rising edges of LBCLK2.

6.  $Q = 0.25 t_{C (LA)}$

# LAN ADAPTER BUS READ AND WRITE PARAMETERS

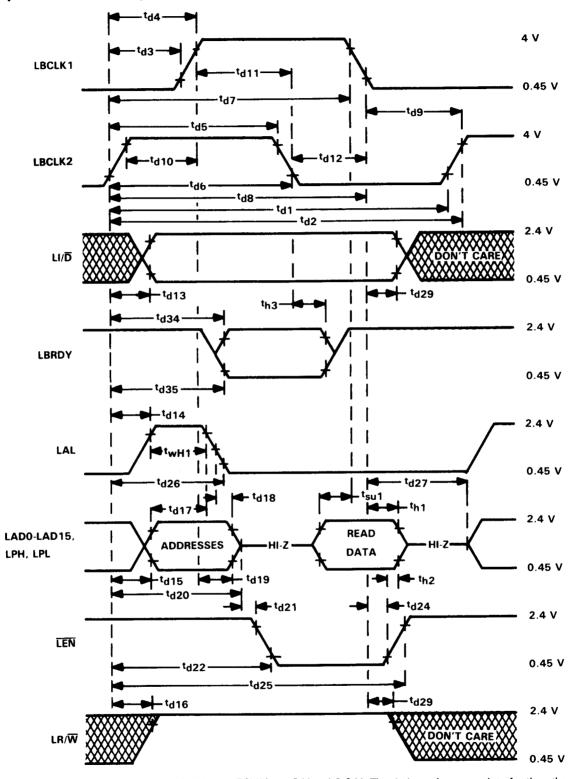

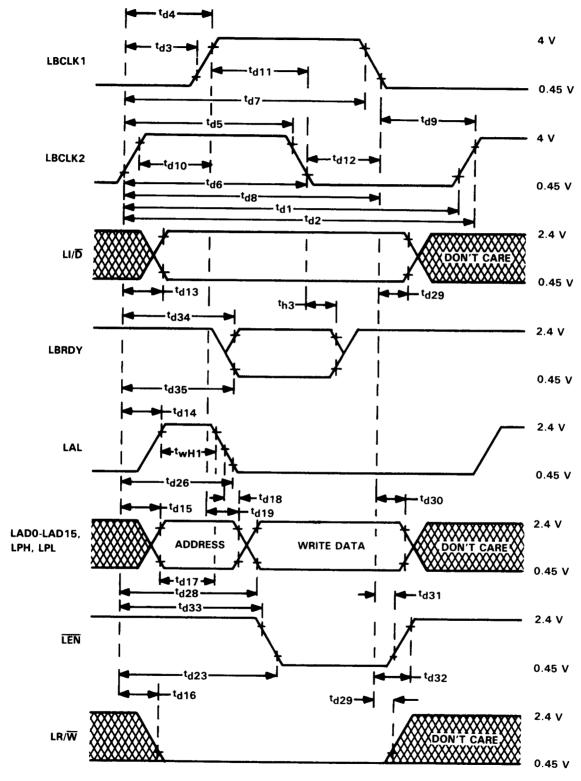

switching characteristics/timing requirements over recommended supply voltage range and operating free-air temperature range (see Figure 3)

|                   | PARAMETER                                                                      | MIN  | MAX     | UNIT |

|-------------------|--------------------------------------------------------------------------------|------|---------|------|

| <sup>t</sup> d13  | Delay time, LBCLK2 rise to LI/D valid                                          |      | 47      |      |

| td14              | Delay time, LBCLK2 rise to LAL high                                            |      | 47      |      |

| td15              | Delay time, LBCLK2 rise to address valid                                       |      | 47_     |      |

| td16              | Delay time, LBCLK2 rise to LR/W valid                                          |      | 47      |      |

| t <sub>wH1</sub>  | Pulse duration, LAL high                                                       | Q-50 |         |      |

| <sup>t</sup> d17  | Delay time, address valid to LAL no longer high                                | Q-50 |         |      |

| td18              | Delay time, LAL fall to 1.3 V to address no longer valid                       | 7_   |         |      |

| td19              | Delay time, LBCLK1 high to address no longer valid                             | 7    |         |      |

| t <sub>d20</sub>  | Delay time, LBCLK2 rise to LAD, LPH, LPL high impedance in read cycle          |      | Q + 74  |      |

| t <sub>d21</sub>  | Delay time, LAD, LPH, LPL high impedance to LEN no longer high in read cycle   | 0    |         |      |

| t <sub>d22</sub>  | Delay time, LBCLK2 rise to LEN low in read cycle                               |      | Q + 84  |      |

| t <sub>d23</sub>  | Delay time, LBCLK2 rise to LEN low in write cycle                              |      | Q + 47  |      |

| t <sub>d24</sub>  | Delay time, LBCLK1 low to LEN no longer low in read cycle                      | 0    |         |      |

| t <sub>d25</sub>  | Delay time, LBCLK2 rise to LEN high in read cycle                              |      | 3Q + 47 | ns   |

| t <sub>d26</sub>  | Delay time, LBCLK2 rise to LAL low                                             |      | 20 – 12 | ""   |

| t <sub>d27</sub>  | Delay time, LBCLK1 low to LAD, LPH, LPL no longer high impedance in next cycle | 80   |         |      |

| td28              | Delay time, LBCLK2 rise to write data valid                                    |      | 3Q - 70 |      |

| t <sub>d29</sub>  | Delay time, LBCLK1 low to LI/D, LR/W no longer valid                           | 20   |         |      |

| t <sub>d30</sub>  | Delay time, LBCLK1 low to write data no longer valid                           | 20   |         |      |

| t <sub>d31</sub>  | Delay time LBCLK1 low to LEN no longer low in write cycle                      | 20   |         |      |

| t <sub>d</sub> 32 | Delay time, LBCLK1 low to LEN high in write cycle                              |      | 80      |      |

| td33              | Delay time, LBCLK2 rise to LEN no longer high in write cycle                   | Q-4  |         |      |

| t <sub>su1</sub>  | Setup time, Read data valid to LBCLK1 no longer high                           | 20   |         |      |

| th1               | Hold time, read data valid after LBCLK1 low if th2 not met                     | 15   |         | ]    |

| th2               | Hold time, read data valid after LEN no longer low if th1 not met              | 0    |         |      |

| t <sub>d34</sub>  | Delay time, LBCLK2 rise to LBRDY high                                          |      | 2Q – 41 |      |

| t <sub>d</sub> 35 | Delay time, LBCLK2 rise to LBRDY low                                           |      | 2Q – 21 |      |

| th3               | Hold time, LBRDY valid after LBCLK2 low                                        | 80   |         |      |

<sup>†</sup>This table is entitled switching characteristics/timing requirements because several of the parameters specified can be classified as characteristics or requirements depending on the mode of operation: bus slave or bus master (DMA). The values given are valid for both modes. NOTE 6: Q = 0.25 t<sub>C(LA)</sub>.

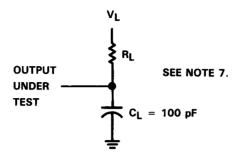

# PARAMETER MEASUREMENT INFORMATION

NOTE 7:  $R_L$  and  $V_L$  are chosen as follows:

$$R_{L} = \frac{V_{OH} - V_{OL}}{|I_{OL} - I_{OH}|}$$

$V_{L} = V_{OH} - (I_{OH})(R_{L})$

FIGURE 3. LOAD CIRCUIT

### LAN adapter bus read timing

NOTE 8: The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for the other waveforms are 2 V and 0.8 V. The intermediate reference point for LAL is 1.3 V.

### LAN adapter bus write timing

NOTE 8: The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for the other waveforms are 2 V and 0.8 V. The intermediate reference point for LAL is 1.3 V.

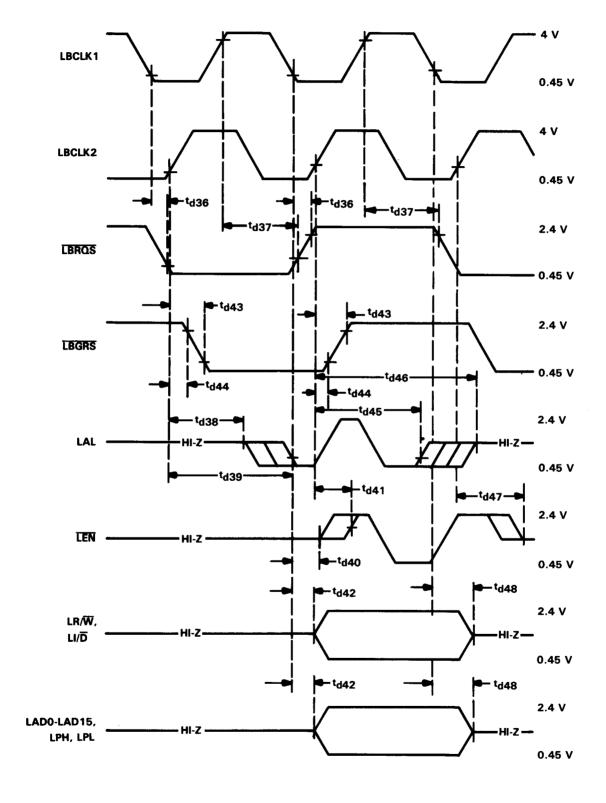

# LAN ADAPTER BUS ARBITRATION PARAMETERS

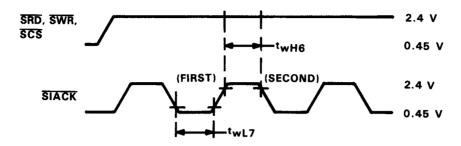

# switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 3)

|                   | PARAMETER                                                                                                                         | MIN  | MAX     | UNIT |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|---------|------|

| t <sub>d</sub> 36 | Delay of LBRQS from LBCLK1 low                                                                                                    |      | 48      |      |

| t <sub>d37</sub>  | Delay of LBRQS after LBCLK1 rise                                                                                                  | 0    |         |      |

| d38               | Delay time, LBCLK2 rise to LAL no longer high impedance by TMS38030                                                               | 20-9 |         |      |

| d39               | Delay time, LBCLK2 rise to LAL driven low by TMS38030                                                                             |      | 3Q – 15 | ns   |

| d40               | Delay time, LBCLK1 low to LEN no longer high impedance by TMS38030                                                                | 80   |         |      |

| d41               | Delay time, LBCLK2 rise to LEN driven high by TMS38030                                                                            |      | 74      |      |

| td42              | Delay time, LBCLK1 low to LR/ $\overline{W}$ , LI/ $\overline{D}$ , LADO-LAD15, LPH, and LPL no longer high impedance by TMS38030 | 80   |         |      |

NOTE 6:  $Q = 0.25 t_{C(LA)}$ .

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                   | PARAMETER                                                                     | MIN     | MAX            | UNIT |

|-------------------|-------------------------------------------------------------------------------|---------|----------------|------|

| t <sub>d</sub> 43 | Delay time, LBCLK2 rise to LBGRS valid                                        |         | 2Q <b>-</b> 73 |      |

| t <sub>d44</sub>  | Delay time, LBCLK2 rise to LBGRS no longer valid                              | -6      |                |      |

| td45              | Delay time, LBCLK2 rise to LAL no longer driven low from old bus master       | 3Q - 15 |                |      |

| td46              | Delay time, LBCLK2 rise to LAL high impedance from old bus master             |         | 40 – 2         | ns   |

| t <sub>d47</sub>  | Delay time, LBCLK2 rise to LEN high impedance from old bus master             |         | 74             |      |

|                   | Delay time, LBCLK1 low to LR/W, LI/D, LADO-LAD15, LPH, and LPL high impedance |         | 80             |      |

| <sup>t</sup> d48  | from old bus master                                                           |         | 60             |      |

NOTE 6:  $Q = 0.25 t_{C(LA)}$ .

### LAN adapter bus arbitration

NOTE 9: The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for the other waveforms are 2 V and 0.8 V.

# **MISCELLANEOUS LAN ADAPTER BUS PARAMETERS**

switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 3)

|                    | PARAMETER                                                                        | MIN | MAX | UNIT |

|--------------------|----------------------------------------------------------------------------------|-----|-----|------|

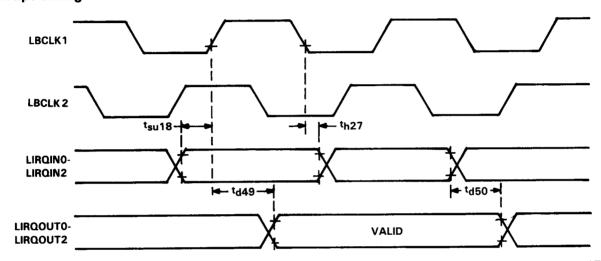

| t <sub>d</sub> 49  | Delay time, LBCLK1 rise to LIRQOUT0-LIRQOUT2 valid                               |     | 140 |      |

| t <sub>su</sub> 18 | LIRQINO-LIRQIN2 setup before LBCLK1 rise                                         | 0   |     | ns   |

| th27               | Hold time, LIRQINO-LIRQIN2 after LBCLK1 low                                      | 0   |     |      |

| t <sub>d50</sub>   | Delay time, LIRQINO-LIRQIN2 no longer valid to LIRQOUTO-LIRQOUT2 no longer valid | 0   |     |      |

### interrupt timing

NOTE 10: LIRQOUTs may not follow LIRQINs because the TMS38030 prioritizes LIRQOUT0-LIRQOUT2 outputs between internal TMS38030 interrupts and LIRQIN0-LIRQIN2.

### SYSTEM DMA TIMING PARAMETERS

switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 3)

|                   | PARAMETER                                                               | MIN                      | MAX | UNIT |

|-------------------|-------------------------------------------------------------------------|--------------------------|-----|------|

|                   | Pulse duration, SAS, SUDS, and SLDS high                                | t <sub>c(SC)</sub> +     |     |      |

| twH2              | ruise duration, SAS, SODS, and SLDS high                                | tw(SCL) - 40             |     |      |

| t <sub>d</sub> 51 | Delay from T1 high to SUDS and SLDS active (read cycle only) (Note 11)  |                          | 55  |      |

| td52              | Delay from T2 high to SUDS and SLDS active (write cycle only) (Note 11) |                          | 55  |      |

| td53              | Delay of output data valid to SUDS and SLDS no longer high              | tw(SCL) - 40             |     |      |

| td54              | Delay from SBCLK low to address valid (Note 11)                         |                          | 45  |      |

| t <sub>d55</sub>  | Delay from T1 low to SAD HI-Z                                           | ĺ                        | 45  |      |

| t <sub>wH3</sub>  | Pulse duration, SALE and SXAL high                                      | t <sub>c</sub> (SC) - 70 |     |      |

| td56              | Delay from SBCLK high to SALE or SXAL high (Note 11)                    |                          | 70  |      |

| th4               | Hold of SALE or SXAL low after SRD, SWR, SUDS, SLDS, and SAS high       | tw(SCL) - 40             |     |      |

| td57              | Delay from T1 high to SALE low or TX high to SXAL low (Note 11)         |                          | 45  |      |

| th5               | Hold of address valid after SALE, SXAL low                              | tw(SCH) - 30             |     |      |

| td58              | Delay from T1 low to output data and parity valid                       |                          | 50  |      |

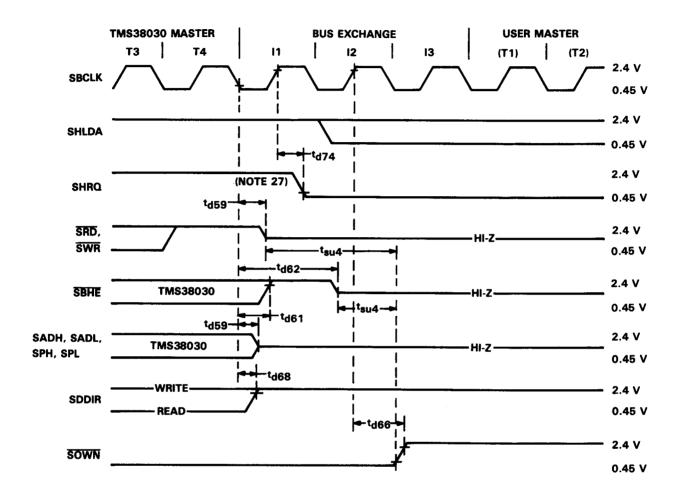

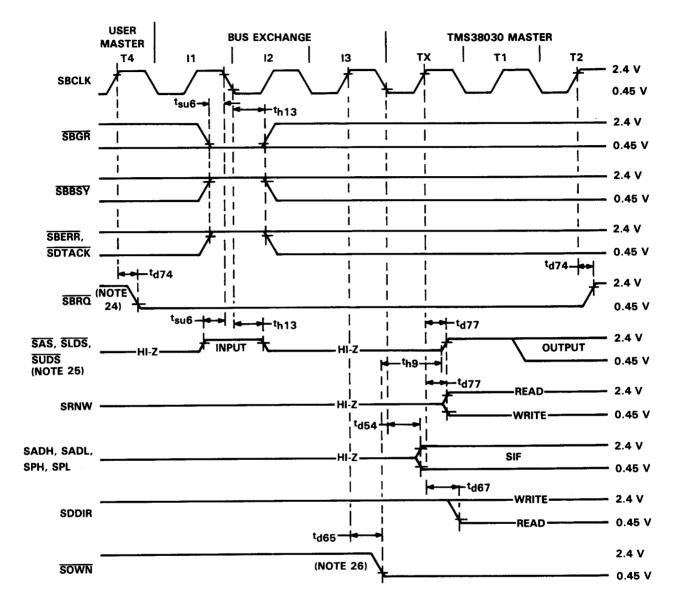

| t <sub>d</sub> 59 | Delay from T4 low to SAD, SPL, SPH, SUDS, SLDS HI-Z, bus release        |                          | 100 |      |

| th6               | Hold of output data, parity valid after write strobe high               | <sup>†</sup> c(SC) - 60  |     |      |

| <sup>t</sup> d60  | Delay from SBCLK high to SAS low                                        |                          | 55  | ns   |

| td61              | Delay from T4 low to SBHE/SRNW high, bus release                        |                          | 75  |      |

| td62              | Delay from T4 low to SBHE/SRNW HI-Z                                     |                          | 145 |      |

| td63              | Delay from T3 low to SRD, SUDS, SLDS, SAS high on read cycle (Note 12)  |                          | 60  |      |

| td64              | Delay from SBCLK low to SWR, SUDS, SLDS, SAS high on write cycle        |                          | 60  |      |

| td65              | Delay from SBCLK high in cycle before T1/TX to SOWN low (Note 13)       |                          | 75  |      |

| t <sub>d66</sub>  | Delay from SBCLK high in 2nd cycle after T4 to SOWN high (Note 11)      |                          | 75  |      |

| td67              | Delay from TX high to SDDIR low in DMA read cycle (Note 11)             |                          | 75  |      |

| td68              | Delay from T4 low in last read cycle to SDDIR high (Note 11)            | 1                        | 75  |      |

| t <sub>d</sub> 69 | Delay from T3 low to SDBEN high, read cycle (Note 11)                   | Note 12                  | 75  |      |

| <sup>t</sup> d70  | Delay from T4 high to SDBEN high, write cycle (Note 11)                 |                          | 60  |      |

| th7               | Hold of SDBEN low after write data strobe high                          | tw(SCL) -40              |     |      |

| td71              | Delay from SAD HI-Z to SRD low                                          | . 0                      |     |      |

| td72              | Delay from T1 low to SRD low                                            |                          | 70  |      |

| td73              | Delay from T1 low to SWR low                                            |                          | 55  |      |

| th8               | Hold of SAD HI-Z after T4 low                                           | 0                        |     |      |

Continued next page.

NOTES: 11. Unless otherwise specified, for all signals specified as a maximum delay from the end of an SBCLK transition to the signal valid, the signal is also specified to hold its previous value (including HI-Z) until the start of that SBCLK transition.

13. While SIF DMA controls are active (i.e., SOWN is asserted), the SCS input is disabled.

### switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 3) (concluded)

|                   | PARAMETER                                                                                  | MIN                      | MAX | UNIT |

|-------------------|--------------------------------------------------------------------------------------------|--------------------------|-----|------|

| t <sub>d74</sub>  | Delay from SBCLK high to bus request valid (Note 11)                                       |                          | 60  |      |

| twL1              | Pulse duration, SRD low                                                                    | 2t <sub>c(SC)</sub> - 40 |     |      |

| twL2              | Pulse duration, SWR low                                                                    | 2t <sub>c(SC)</sub> - 40 |     |      |

| tsu2              | Setup of address valid before SALE, SXAL no longer high                                    | tw(SCL) - 43             |     |      |

| t <sub>su3</sub>  | Setup of address valid before SAS no longer high                                           | tw(SCL) - 32             |     |      |

| td75              | Delay from T2 high to SDBEN low in read cycle (Note 11)                                    |                          | 80  |      |

| t <sub>d</sub> 76 | Delay from T1 high to SDBEN low in write cycle (Note 11)                                   |                          | 60  |      |

|                   | D.L. duration CAC on word and united pulse duration CUDS and CLDS on road                  | 2t <sub>c(SC)+</sub>     |     | ns   |

| twL3              | Pulse duration, SAS on read and write; pulse duration, SUDS and SLDS on read               | tw(SCH) - 50             |     |      |

| t <sub>su4</sub>  | Setup of control signals HI-Z before SOWN no longer low                                    | 0                        |     |      |

| t <sub>d77</sub>  | Delay from TX high to data strobes high, bus acquisition (Note 11)                         |                          | 70  |      |

| th9               | Hold of data strobe HI-Z after SOWN low, bus acquisition                                   | <sup>t</sup> c(SC) - 70  |     |      |

|                   | D.L. duration CUSC and CUSC are united                                                     | t <sub>c</sub> (SC)+     |     |      |

| twL4              | Pulse duration, SUDS and SLDS on write                                                     | <sup>t</sup> w(SCH) - 50 |     |      |

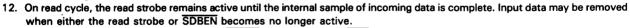

| td78              | Delay from SRESET low to TRESET low, VCC at VCC min                                        |                          | 100 |      |

| t <sub>d</sub> 79 | Delay from SRESET high to LRESET high                                                      |                          | 200 |      |

| t <sub>d80</sub>  | Delay from reaching minimum V <sub>CC</sub> during power-up to valid SBCLK, LBCLK1, LBCLK2 |                          | 90  | ms   |

NOTE 11: Unless otherwise specified, for all signals specified as a maximum delay from the end of an SBCLK transition to the signal valid, the signal is also specified to hold its previous value (including HI-Z) until the start of that SBCLK transition.

# timing requirements over recommended supply voltage range and operating free-air temperature range

|                      | PARAMETER                                                                                     |                       | MIN | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------------------------------|-----------------------|-----|-----|------|

| •                    | Cycle time of SBCLK                                                                           | TMS38030-6            | 166 | 500 |      |

| t <sub>c</sub> (SC)  | (Note 14)                                                                                     | TMS38030-8            | 125 | 500 | ns   |

|                      | (14016-14)                                                                                    | TMS38030-10           | 100 | 500 | 1    |

|                      |                                                                                               | TMS38030-6            | 65  |     |      |

| <sup>t</sup> w(SCL)  | Pulse duration, SBCLK low                                                                     | TMS38030-8            | 55  |     | ns   |

|                      |                                                                                               | TMS38030-10           | 45  |     |      |

|                      |                                                                                               | TMS38030-6            | 65  |     |      |

| <sup>t</sup> w(SCH)  | Pulse duration, SBCLK high                                                                    | TMS38030-8            | 55  |     | ns   |

|                      |                                                                                               | TMS38030-10           | 45  |     |      |

| tt(SC)               | Transition time of SBCLK                                                                      |                       |     | 10  | ns   |

| t <sub>su5</sub>     | Setup of input data valid before T3 no longer high                                            |                       | 15  |     | ns   |

| <sup>t</sup> h10     | Hold of input data valid after T3 low, if thill and thill not met                             |                       | 40  |     | ns   |

| <sup>t</sup> h11     | Hold of input data valid after data strobe no longer low                                      |                       | 0   |     | ns   |

| th12                 | Hold of input data valid after SDBEN no longer low                                            |                       | 0   |     | ns   |

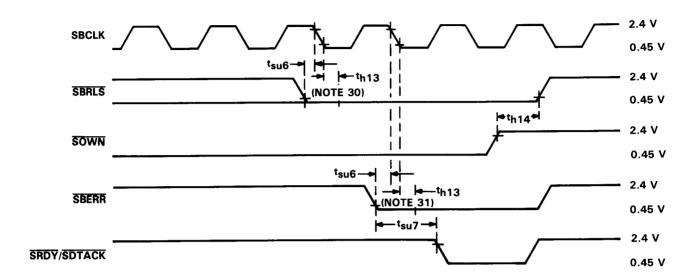

| <sup>t</sup> su6     | Setup of asynchronous input before SBCLK no longer high to guara                              | ntee recognition      | 20  |     | ns   |

| th13                 | Hold of asynchronous input after SBCLK low to guarantee recognit                              | on                    | 40  |     | ns   |

| th14                 | Hold of SBRLS low after SOWN high                                                             |                       | 0   |     | ns   |

| t <sub>su</sub> 7    | Setup of SBERR low before SRDY/SDTACK no longer high, if t <sub>su6</sub>                     | not met               | 65  |     | ns   |

| <sup>t</sup> su8     | Setup of SRDY/SDTACK low before data valid if t <sub>su6</sub> not met                        |                       |     | 45  | ns   |

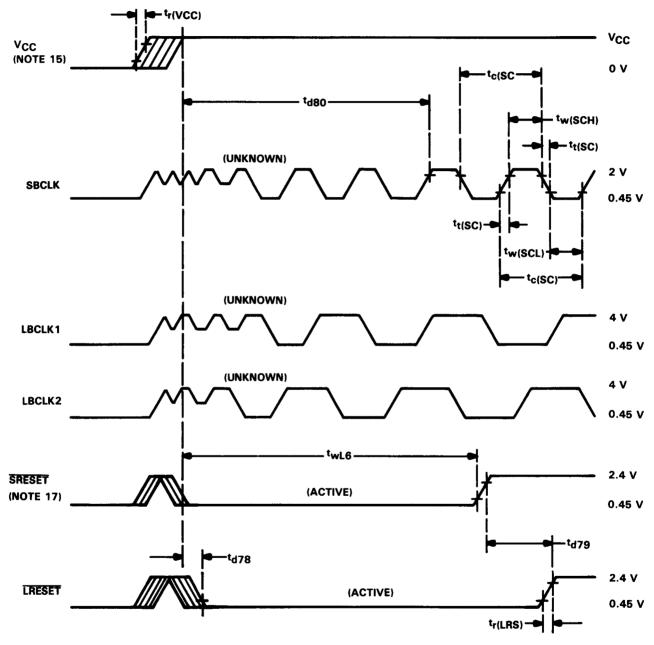

|                      | Pulse duration, SRESET and LRESET asserted with minimum V <sub>CC</sub> of                    | r greater applied and |     |     |      |

| twL5                 | valid LBCLKs                                                                                  |                       | 14  |     | μS   |

| <sup>t</sup> wL6     | Pulse duration, SRESET asserted after V <sub>CC</sub> above V <sub>CC</sub> (min) at power-up |                       | 100 |     | ms   |

| t <sub>r</sub> (LRS) | Rise time of LRESET                                                                           |                       |     | 100 | ns   |

| tr(VCC)              | Rise time from 1.2 volts to V <sub>CC</sub> minimum, at the V <sub>CC</sub> pins              |                       | 1   |     | ms   |

NOTE 14: The MXTALOUT signal output of the TMS38010 cannot be used as the SBCLK input.

### power-up, SBCLK, LBCLK, SRESET, and LRESET timing

#### power on

- NOTES: 15. A minimum one second interval between power off and power on is required for correct initialization of the TMS38030.

- 16. The timing reference points for LBCLK1 and LBCLK2 are 3 V and 0.8 V. The timing reference points for SBCLK, SRESET,

- and LRESET are 2 V and 0.8 V. The timing reference points for V<sub>CC</sub> are 4.5 V and 1.2 V.

17. During power-up, SRESET is undefined (asserted) prior to 1.2 V applied to the V<sub>CC</sub> pins of the TMS38030.

SRESET must remain asserted from V<sub>CC</sub> = 1.2 V to V<sub>CC</sub> minimum. The TMS38030 must not be accessed from either the system or LAN Adapter bus interface within 3 µs of the de-assertion of SRESET. This is primarily a test limitation since currently available processors cannot violate this condition.

# SRESET and LRESET timing

### operational

NOTE 18: The timing reference points for SRESET and LRESET are 2 V and 0.8 V.

†Following a low-to-high transition of SRESET, SRESET must remain high for a minimum of 20 milliseconds before again driven low.

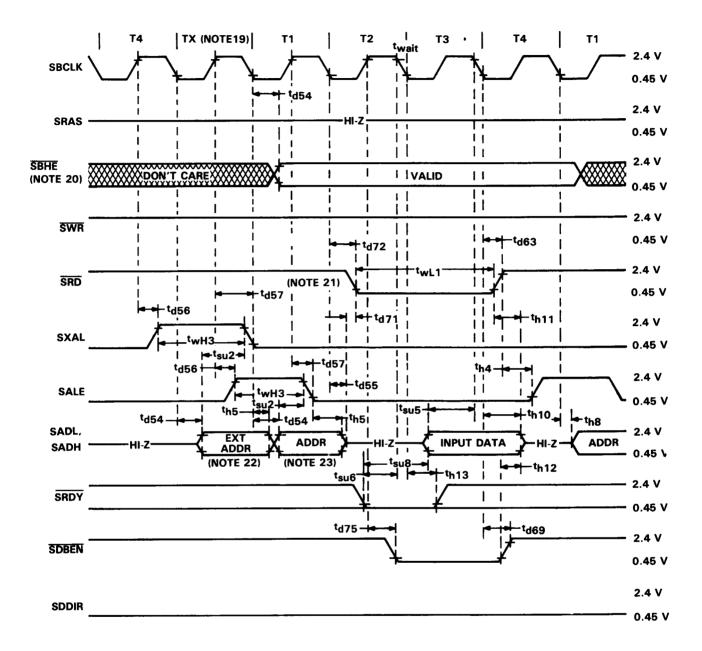

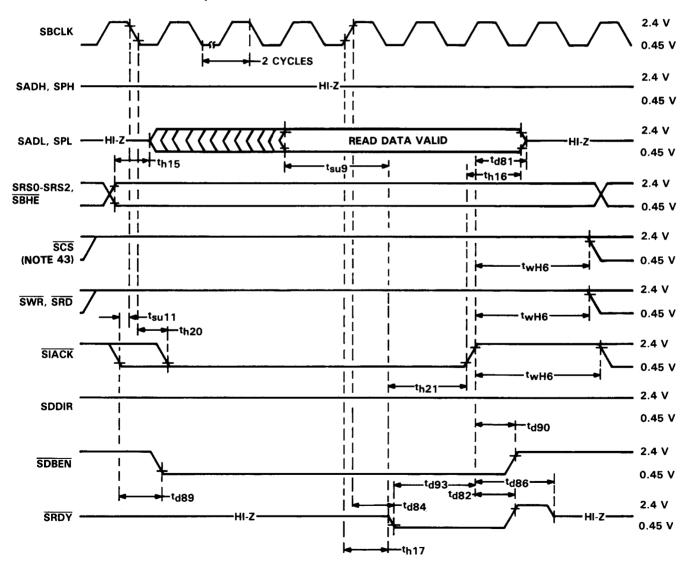

### 808X mode DMA read timing

- NOTES: 19. In cycle-steal mode, state TX is present on every system bus transfer. In burst mode, state TX is present on the first bus transfer, and whenever the increment of the address carries beyond the least-significant 8 bits.

- 20. In 8-bit 808X Mode, SBHE/SRNW is a don't care input during DIO and an inactive (high) output during DMA.

- 21. If the TX state is not present, SAS, SUDS, and SLDS are asserted in the T1 state.

- 22. In state TX, SADH continues to output the most-significant byte of the address.

- 23. In 8-bit mode, the most-significant byte of the address is maintained on SADH for T2, T3, and T4. The address is maintained according to the, i.e., held after T4 high.

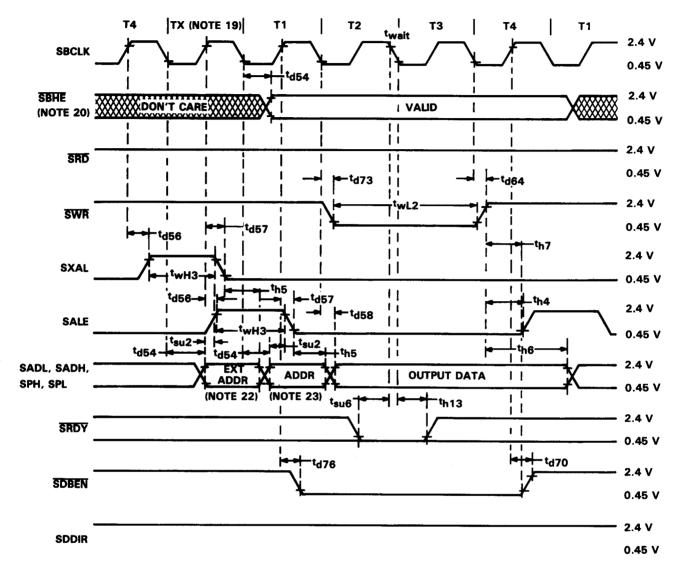

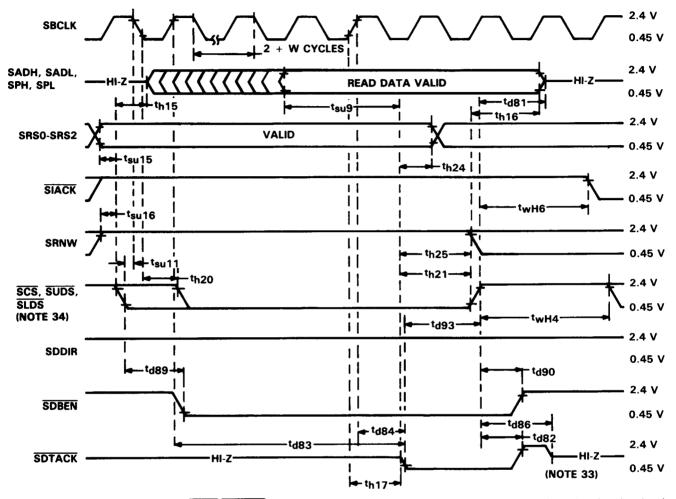

### 808X mode DMA write timing

NOTES: 19. In cycle-steal mode, state TX is present on every system bus transfer. In burst mode, state TX is present on the first bus transfer, and whenever the increment of the address carries beyond the least-significant 8 bits.

- 20. In 8-bit 808X Mode, SBHE/SRNW is a don't care input during DIO and an inactive (high) output during DMA.