# Single Row Buffer SRB

| E | E/ | ۸7 | TI. | н | 31 | 6 | e | • |

|---|----|----|-----|---|----|---|---|---|

|   |    |    |     |   |    |   |   |   |

- □ Low Cost Solution to CRT Memory Contention Problem

□ Provides Enhanced Processor Throughput for CRT

- Display Systems

- ☐ Provides 8 Bit Wide Variable Length Serial Memory

- ☐ Permits Active Video on All Scan Lines of Data Row

- ☐ Dynamically Variable Number of Characters per Data Row—...64, 80, 132,...up to a Maximum of 135

- ☐ Cascadable for Data Rows Greater than 135 Characters

- ☐ Stackable for Invisible Attributes or Character

- Widths of Greater than 8 Bits

- ☐ Three-State Outputs

- ☐ 3.3MHz Typical Read/Write Data Rate

- ☐ Static Operation

- ☐ Compatible with SMC CRT 5037, CRT 9007, and other CRT Controllers

- 24 Pin Dual In Line Package

- +5 Volt Only Power Supply

- ☐ TTL Compatible Inputs and Outputs

- ☐ Available in 135 Byte Maximum Length (CRT 9006-135)

- or 83 Byte Maximum Length (CRT 9006-83)

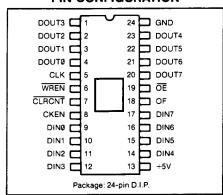

#### PIN CONFIGURATION

#### **APPLICATIONS:**

- ☐ CRT Data Row Buffer

- ☐ Block-Oriented Buffer

- ☐ Printer Buffer

- ☐ Synchronous Communications Buffer

- ☐ Floppy Disk Sector Buffer

#### **GENERAL DESCRIPTION**

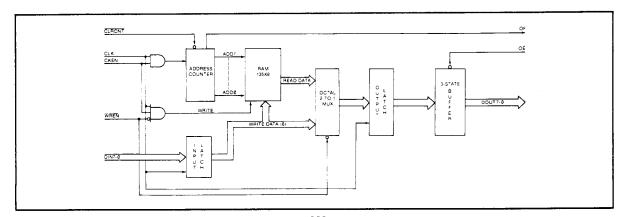

The SMC Single Row Buffer (SRB) provides a low cost solution to memory contention between the system processor and CRT controller in video display systems.

The SRB is a RAM-based buffer which is loaded with character data from system memory during the first scan line of each data row. While data is being written into the RAM it is also being output through the multiplexer onto the Data Ouput

(DOUT) Lines. During subsequent scan lines in the data row, the system will disable Write Enable (WREN) and cause data to be read out from the internal RAM for CRT screen refresh, thereby releasing the system memory for processor access for the remaining N-1 scan lines where N is the number of scan lines per data row. The SRB enhances processor throughput and permits a flicker-free display of data.

#### **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO. | NAME          | SYMBOL      | FUNCTION                                                                                                                                                                                                                             |

|---------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-4     | DATA OUTPUTS  | DOUT3-DOUTØ | Data Outputs from the internal output latch.                                                                                                                                                                                         |

| 5       | CLOCK         | CLK         | Character clock. The negative-going edge of CLK clocks the latches. When CKEN (pin 8) is high, CLK will increment the address counter.                                                                                               |

| 6       | WRITE ENABLE  | WREN        | When WREN is low, data from the input latch is transferred directly to the output latch and simultaneously written into sequential locations in the RAM.                                                                             |

| 7       | CLEAR COUNTER | CLRCNT      | A negative transition on CLRCNT clears the RAM address counter. CLRCNT is normally asserted low near the beginning of each scan line.                                                                                                |

| 8       | CLOCK ENABLE  | CKEN        | When CKEN is high, CLK will clock the address counter. The combination of CKEN high and WREN low will allow the writing of data into the RAM.                                                                                        |

| 9-12    | DATA INPUTS   | DINØ-DIN3   | Data Inputs from system memory.                                                                                                                                                                                                      |

| 13      | POWER SUPPLY  | Vcc         | +5 Volt supply.                                                                                                                                                                                                                      |

| 14-17   | DATA INPUTS   | DIN4-DIN7   | Data Inputs from system memory.                                                                                                                                                                                                      |

| 18      | OVERFLOW FLAG | OF          | This output goes high when the RAM address counter reaches its maximum count. If cascaded operation of multiple CRT 9006's is desired for more than 135 bytes, OF may be used to drive the CKEN input of the second row buffer chip. |

| 19      | OUTPUT ENABLE | ŌĒ          | When $\overline{OE}$ is low, the data outputs DOUTØ-DOUT7 are enabled. When $\overline{OE}$ is high, DOUTØ-DOUT7 present a high impedance state.                                                                                     |

| 20-23   | DATA OUTPUTS  | DOUT7-DOUT4 | Data Outputs from the internal output latch.                                                                                                                                                                                         |

| 24      | GROUND        | GND         | Ground.                                                                                                                                                                                                                              |

#### **OPERATION**

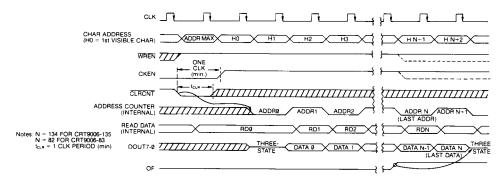

For CRT operation, the Write Enable (WREN) signal is made active for the duration of the top scan line of each data row. Clear Counter (CLRCNT) typically occurs at the beginning of each scan line (HSYNC may be used as input to CLRCNT). Data is continually clocked into the input latch by CLK. When Clock Enable (CKEN) occurs, the data in the input latch (Write Data) is written into the first location of RAM. At the negative-going edge of the next clock, the address counter is incremented, the next input data is latched into the input latch, and the new data is then written into the RAM. Loading the RAM continues until one clock after CKEN goes inactive or until the

RAM has been fully loaded (135 bytes). While data is being written into the RAM, it is also being output through the multiplexer onto the Data Output (DOUT) lines. Each byte is loaded into the output latch one clock time later than it is written into the RAM. Output of the data during the first scan line permits the Video Display Controller (such as the CRT 8002) to display video on the first scan line. During subsequent scan lines in the data row, the system will disable Write Enable (WREN) and cause data to be read out from the internal RAM, thereby freeing the system memory for processor access for the remaining N-1 scan lines where N is the number of scan lines per data row.

#### **MAXIMUM GUARANTEED RATINGS\***

| Operating Temperature Range                         | 0°C to + 70°C     |

|-----------------------------------------------------|-------------------|

| Storage Temperature Range                           | 55° C to + 150° C |

| Lead Temperature (soldering, 10 sec.)               | +325°C            |

| Positive Voltage on any Pin, with respect to ground | +8 OV             |

| Positive voltage on any Pin, with respect to ground | -0.07             |

| Negative Voltage on any Pin, with respect to ground |                   |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

### **ELECTRICAL CHARACTERISTICS** ( $T_A = 0^{\circ}$ C to 70° C, $V_{CC} = +5 \pm 5\%$ , unless otherwise noted)

| PARAMETER                                                                        | MIN          | TYP        | MAX          | UNITS          | COMMENTS                                            |

|----------------------------------------------------------------------------------|--------------|------------|--------------|----------------|-----------------------------------------------------|

| DC CHARACTERISTICS                                                               |              |            |              |                |                                                     |

| Input Voltage Levels<br>Low Level V <sub>IL</sub><br>High Level V <sub>IH</sub>  | 2.0          |            | 0.8          | V              |                                                     |

| Output Voltage Levels<br>Low Level V <sub>OL</sub><br>High Level V <sub>OH</sub> | 2.4          |            | 0.4          | V              | I <sub>OL</sub> = 2mA<br>I <sub>OH</sub> = -100µA   |

| Input Current<br>Leakage, I <sub>⊩</sub>                                         |              |            | 10           | μΑ             | 0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>               |

| Output '1' Leakage<br>Output '0' Leakage<br>(Off State)                          |              |            | 10<br>10     | μΑ<br>μΑ       |                                                     |

| Input Capacitance CLK All other inputs                                           |              | 30<br>10   | 45<br>15     | pF<br>pF       |                                                     |

| Power Supply Current $I_{\infty}$ (SRB-135) $I_{\infty}$ (SRB-83)                |              |            | 115<br>100   | mA<br>mA       |                                                     |

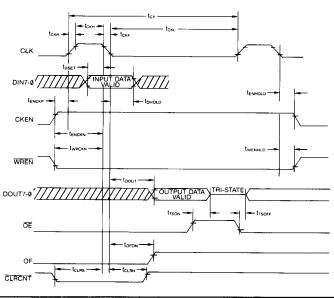

| AC CHARACTERISTICS                                                               |              |            |              |                |                                                     |

| t <sub>cy</sub> (SRB135)<br>(SRB83)                                              | 300<br>400   | 250<br>330 |              | ns<br>ns       |                                                     |

| t <sub>CKL</sub> (SRB135)<br>(SRB83)                                             | 240<br>320   | 190<br>250 | DC<br>DC     | ns<br>ns       |                                                     |

| <sup>t<sub>СКН</sub></sup> (SRB135)<br>(SRB83)                                   | 28<br>34     |            | 5000<br>5000 | ns<br>ns       |                                                     |

| t <sub>CKR</sub> (SRB135)<br>(SRB83)                                             |              |            | 10<br>10     | ns<br>ns       | t <sub>скн</sub> = 28ns<br>t <sub>скн</sub> = 34ns  |

| t <sub>CKF</sub> (SRB135) (SRB83)                                                |              |            | 10<br>10     | ns<br>ns       | t <sub>CKL</sub> =240ns<br>t <sub>CLK</sub> = 320ns |

| tdset<br>tdhold<br>tenckp                                                        | 65<br>5<br>0 |            |              | ns<br>ns<br>ns |                                                     |

| t <sub>ENCKN</sub> (SRB135) (SRB83)                                              | 100<br>125   |            |              | ns<br>ns       |                                                     |

| tenhold<br>twrckn                                                                | 0            |            |              | ns             |                                                     |

| (SRB135)<br>(SRB83)                                                              | 100<br>125   |            |              | ns<br>ns       |                                                     |

| twenhld thout                                                                    | 0            |            | 175          | ns<br>ns       | C <sub>L</sub> = 50pF                               |

| t <sub>TSON</sub>                                                                |              |            | 175          | ns             | 32 33                                               |

| trsoff<br>tofon                                                                  |              |            | 175<br>175   | ns<br>ns       | C <sub>L</sub> = 30pF                               |

| t <sub>CLRS</sub> (SRB135)                                                       | 100          |            |              | ns             | ·                                                   |

| (SRB83)                                                                          | 125          |            |              | ns             |                                                     |

| t <sub>CLRH</sub>                                                                | 0            | 004        | I            | ns             | į.                                                  |

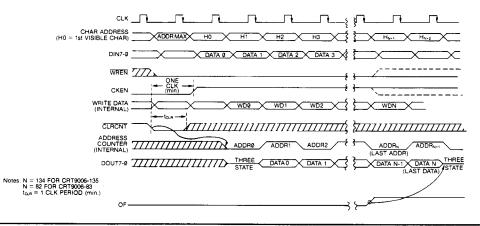

#### FIGURE 2: SINGLE ROW BUFFER READ TIMING

#### FIGURE 3: SINGLE ROW BUFFER WRITE TIMING

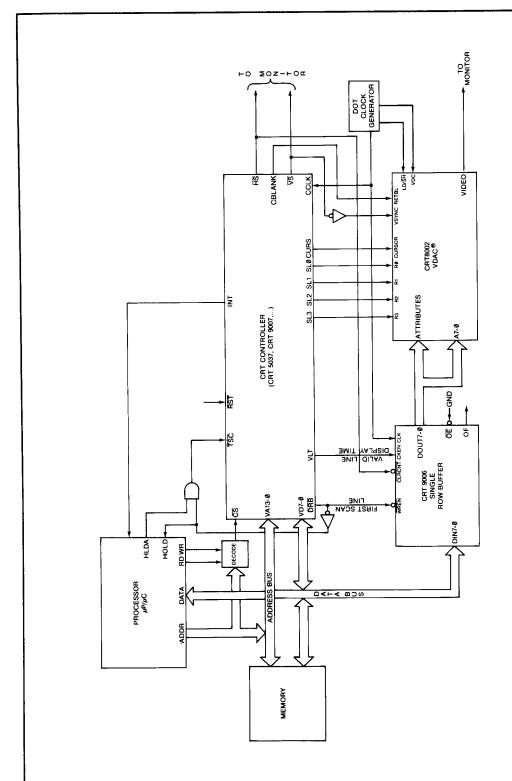

FIGURE 2: TYPICAL CRT CONTROLLER CONFIGURATION WITH SINGLE ROW BUFFER

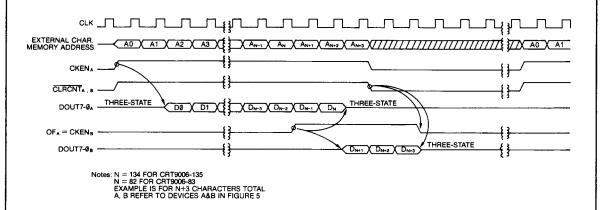

## FIGURE 4: TYPICAL READ TIMING FOR SRB CASCADED CONFIGURATION

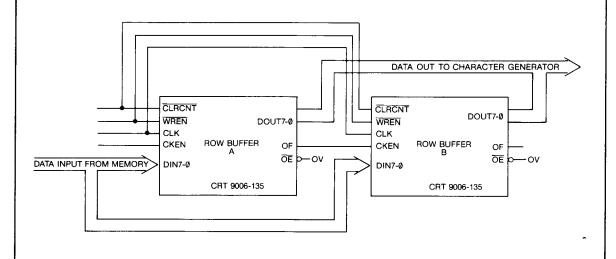

## FIGURE 5: TYPICAL CASCADE OF SINGLE ROW BUFFERS—270 BYTES TOTAL

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications; consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMC or others, SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.