### Very high accuracy (20 μV), zero-drift, rail-to-rail output, 3 MHz, 36 V op amp

MiniSO8

SO8

#### **Features**

Very low offset voltage: 20 μV max. @ 25 °C

Rail-to-rail output

Wide supply voltage: 4 to 36 VGain bandwidth product: 3 MHz

Slew rate: 2 V/µs

Low noise: 24 nV/√Hz

EMI hardened

High ESD tolerance: 4 kV HBM

Extended temperature range: -40 °C to 125 °C

AEC-Q100 qualified

### **Applications**

| • | Ind | lus | trıa |

|---|-----|-----|------|

· Power supplies

Automotive

### Description

The TSB182 is a very high precision dual operational amplifier ensuring a maximum input offset voltage of 20  $\mu$ V. It can operate over an extended supply voltage range and features rail-to-rail output. It offers an excellent speed/current consumption ratio with 3 MHz gain bandwidth product while consuming 650  $\mu$ A typically per operational amplifier on a large supply voltage range.

The TSB182 operates over a wide temperature range from -40 °C to 125 °C making this device ideal for industrial and automotive applications with the associated qualification.

Thanks to its small package size, the TSB182 can be used in applications where space on the board is limited. It can thus reduce the overall cost of the PCB.

#### Maturity status link

TSB182

| Related products |                                                      |  |  |

|------------------|------------------------------------------------------|--|--|

| TSB612           | For lower current consumption                        |  |  |

| TSB622           | For lower speed                                      |  |  |

| TSB572           | For rail-to-rail inputs                              |  |  |

| TSB712           | For higher speed, precision, and rail-to-rail inputs |  |  |

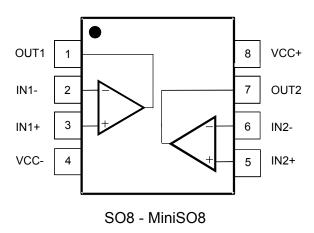

# 1 Pin description

Figure 1. Pin connections (top view)

**Table 1. Pin description**

| Pin | Pin name | Description             |  |  |

|-----|----------|-------------------------|--|--|

| 1   | OUT1     | Output                  |  |  |

| 2   | IN1 -    | Negative input voltage  |  |  |

| 3   | IN1 +    | Positive input voltage  |  |  |

| 4   | VCC -    | Negative supply voltage |  |  |

| 5   | IN2 +    | Positive input voltage  |  |  |

| 6   | IN2 -    | Negative input voltage  |  |  |

| 7   | OUT2     | Output                  |  |  |

| 8   | VCC +    | Positive supply voltage |  |  |

DS14357 - Rev 4 page 2/36

# Absolute maximum ratings and operating conditions

Table 2. Absolute maximum ratings

| Symbol | Parameter                                      | Value                      | Unit |

|--------|------------------------------------------------|----------------------------|------|

| Vcc    | Supply voltage (1)                             | 40                         | V    |

| Vid    | Differential input voltage (2)                 | ± 0.7                      | V    |

| Vin    | Input voltage                                  | (Vcc-) -0.3 to (Vcc+) +0.3 | V    |

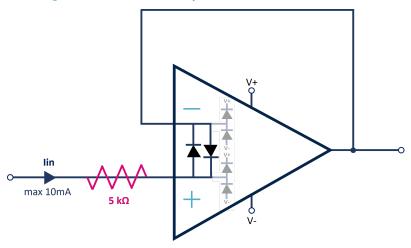

| lin    | Input current (3)                              | 10                         | mA   |

| Tstg   | Storage temperature                            | -65 to 150                 | °C   |

| Tj     | Junction temperature                           | 150                        | °C   |

|        | Thermal resistance junction-to-ambient (4) (5) |                            |      |

| Rth-ja | S08                                            | 125                        | °C/W |

|        | MiniSO8                                        | 190                        |      |

|        | Human Body Model (HBM) (6)                     | 4000                       |      |

| ESD    | Machine Model (MM) (7)                         | 200                        | V    |

|        | Charged Device Model (CDM) (8)                 | 1500                       |      |

- 1. All voltage values, except differential voltage, are with respect to network ground terminal.

- 2. The differential voltage is the difference between inverting and non-inverting terminal voltage.

- 3. Input current must be limited by a resistor in series with the inputs.

- 4. Rth are typical values.

- 5. Short-circuits can cause excessive heating and destructive dissipation.

- 6. According to JEDEC standard JESD22-A114F.

- 7. According to JEDEC standard JESD22-A115A.

- 8. According to ANSI/ESD STM 5.3.1.

**Table 3. Operating conditions**

| Symbol | Parameter                            | Value               | Unit |

|--------|--------------------------------------|---------------------|------|

| Vcc    | Supply voltage                       | 4 to 36             | V    |

| Vicm   | Common mode voltage on input pins    | (Vcc-) to (Vcc+) -2 | V    |

| Т      | Operating free-air temperature range | -40 to 125          | °C   |

DS14357 - Rev 4 page 3/36

### 3 Electrical characteristics

Table 4. Electrical characteristics  $V_{CC}$  = 5 V,  $V_{icm}$  =  $V_{CC}/2$ ,  $R_L$  = 10 k $\Omega$  connected to  $V_{CC}/2$  (unless otherwise specified)

| Symbol                       | Parameter                       | Conditions                                              | Min.     | Тур. | Max. | Unit                                           |

|------------------------------|---------------------------------|---------------------------------------------------------|----------|------|------|------------------------------------------------|

|                              |                                 | DC performance                                          |          |      |      |                                                |

|                              |                                 | V <sub>icm</sub> = V <sub>CC</sub> /2                   |          |      |      |                                                |

|                              |                                 | T = 25 °C                                               | -20      |      | +20  |                                                |

| \/ Input offers              | Innut offert veltere            | Tmin < T < Tmax                                         | -30      |      | +30  |                                                |

| $V_{IO}$                     | Input offset voltage            | V <sub>icm</sub> = 0 V                                  |          |      | '    | μV                                             |

|                              |                                 | T = 25 °C                                               | -20      |      | +20  |                                                |

|                              |                                 | Tmin < T < Tmax                                         | -30      |      | +30  |                                                |

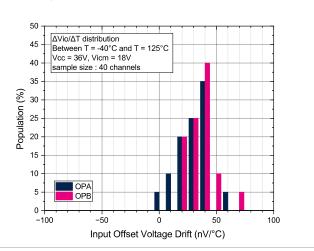

| $\Delta V_{IO}/\Delta T_{I}$ | Input offset voltage drift (1)  | Tmin < T < Tmax                                         |          | 30   | 100  | nV/°C                                          |

| 1                            | Input higg gurrant              | T = 25 °C                                               |          |      | 400  |                                                |

| I <sub>IB</sub>              | Input bias current              | Tmin < T < Tmax                                         |          |      | 400  |                                                |

| l                            | Input offset current            | T = 25 °C                                               |          |      | 600  | pA                                             |

| I <sub>IO</sub>              | input onset current             | Tmin < T < Tmax                                         |          |      | 600  |                                                |

| CMR                          | Common made rejection ratio     | $V_{icm}$ = 0 to $V_{CC}$ -2 V, $V_{out}$ = $V_{CC}$ /2 | 105      | 130  |      | dB                                             |

| CIVIR                        | Common mode rejection ratio     | Tmin < T < Tmax                                         | 97       |      |      |                                                |

| A l                          | 1                               | V <sub>OUT</sub> = 0.5 to (V <sub>CC</sub> -0.5 V)      | 105      | 130  |      |                                                |

| Avd                          | Large signal voltage gain       | Tmin < T < Tmax                                         | 96       |      |      | dB                                             |

|                              | Outside the second second       | T = 25 °C                                               |          | 30   | 50   |                                                |

| $V_{OL}$                     | Output swing from negative rail | Tmin < T < Tmax                                         |          |      | 80   | m) /                                           |

| V <sub>OH</sub>              | Output awing from positive roll | T = 25 °C                                               |          | 20   | 40   | mV                                             |

| VOH                          | Output swing from positive rail | Tmin < T < Tmax                                         |          |      | 60   |                                                |

|                              |                                 | V <sub>OUT</sub> connected to VCC+                      |          |      |      |                                                |

|                              | Isink                           | T = 25 °C                                               | 20       | 27   |      |                                                |

| I                            |                                 | Tmin < T < Tmax                                         | 10       |      |      | - m A                                          |

| l <sub>OUT</sub>             |                                 | V <sub>OUT</sub> connected to VCC-                      | <u>'</u> |      |      | mA                                             |

|                              | Isource                         | T = 25 °C                                               | 20       | 29   |      |                                                |

|                              |                                 | Tmin < T < Tmax                                         | 10       |      |      |                                                |

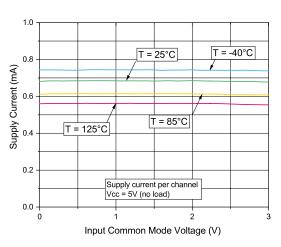

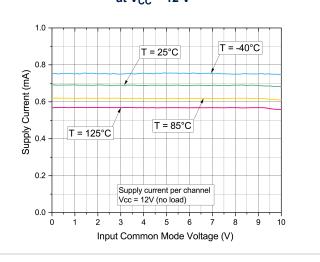

| I                            | Cumply cumpert (per sharped)    | No load, V <sub>OUT</sub> = V <sub>CC</sub> /2          |          | 650  | 850  |                                                |

| I <sub>CC</sub>              | Supply current (per channel)    | Tmin < T < Tmax                                         |          |      | 900  | μA                                             |

|                              |                                 | AC performance                                          |          |      |      | •                                              |

| GBP                          | Cain handwidth are dust         | $R_L = 10 \text{ k}\Omega, C_L = 100 \text{ pF}$        | 1.8      | 3    |      | MHz                                            |

| GBP                          | Gain bandwidth product          | Tmin < T < Tmax                                         | 1.6      |      |      | IVIHZ                                          |

| CD.                          | Claw rata                       | T = 25 °C                                               | 0.85     | 2    |      | \// <sub>1</sub> / <sub>1</sub> / <sub>2</sub> |

| SR                           | Slew rate                       | Tmin < T < Tmax                                         | 0.75     |      |      | V/µs                                           |

| Фт                           | Phase margin                    | $R_L = 10 \text{ k}\Omega, C_L = 100 \text{ pF}$        |          | 58   |      | o                                              |

| Gm                           | Gain margin                     |                                                         |          | 15   |      | dB                                             |

| En                           | Equivalent input soice valters  | f = 1 kHz                                               |          | 27   |      | nV/√H                                          |

| En                           | Equivalent input noise voltage  | 0.1 to 10 Hz                                            |          | 700  |      | nVpp                                           |

DS14357 - Rev 4 page 4/36

| Symbol | Parameter                         | Conditions                                 | Min. | Тур.  | Max. | Unit |

|--------|-----------------------------------|--------------------------------------------|------|-------|------|------|

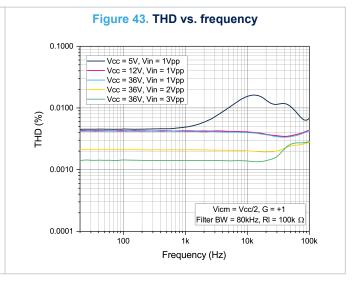

| THD+N  | Total harmonic distortion + noise | f = 1 kHz, G = 1, V <sub>OUT</sub> = 1 Vpp |      | 0.005 |      | %    |

| Cs     | Channel separation                | f = 1 kHz                                  |      | 130   |      | dB   |

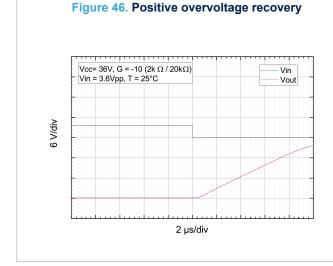

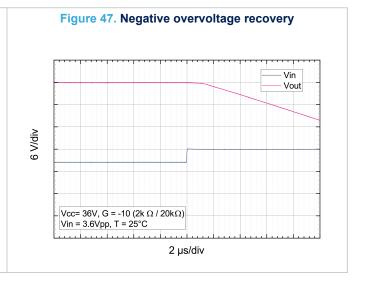

| trec   | Overload recovery time            | G = -10                                    |      | 2     |      | μs   |

| Ts     | Settling time                     | 0.1% to final value, G = 1, 1 V step       |      | 18    |      | μs   |

| Cload  | Capacitive load drive             | No sustained oscillation                   |      | 1     |      | nF   |

<sup>1.</sup> See section Section 5.4.

DS14357 - Rev 4 page 5/36

Table 5. Electrical characteristics  $V_{CC}$  = 12 V,  $V_{icm}$  =  $V_{CC}/2$ ,  $R_L$  = 10 k $\Omega$  connected to  $V_{CC}/2$  (unless otherwise specified)

| Symbol                 | Parameter                         | Conditions                                              | Min. | Тур.  | Max. | Unit  |

|------------------------|-----------------------------------|---------------------------------------------------------|------|-------|------|-------|

|                        |                                   | DC performance                                          |      |       |      |       |

|                        |                                   | V <sub>icm</sub> = V <sub>CC</sub> /2                   |      |       |      |       |

|                        |                                   | T = 25 °C                                               | -20  |       | +20  |       |

|                        |                                   | Tmin < T < Tmax                                         | -30  |       | +30  |       |

| $V_{IO}$               | Input offset voltage              | V <sub>icm</sub> = 0 V                                  |      | I     | I    | μV    |

|                        |                                   | T = 25 °C                                               | -20  |       | +20  |       |

|                        |                                   | Tmin < T < Tmax                                         | -30  |       | +30  |       |

| Δ V <sub>IO</sub> /ΔΤΙ | Input offset voltage drift (1)    | Tmin < T < Tmax                                         |      | 25    | 100  | nV/°C |

|                        |                                   | T = 25 °C                                               |      |       | 400  |       |

| I <sub>IB</sub>        | Input bias current                | Tmin < T < Tmax                                         |      |       | 400  |       |

|                        |                                   | T = 25 °C                                               |      |       | 600  | pA    |

| I <sub>IO</sub>        | Input offset current              | Tmin < T < Tmax                                         |      |       | 600  |       |

|                        |                                   | $V_{icm}$ = 0 to $V_{CC}$ - 2 V, $V_{OUT}$ = $V_{CC}/2$ | 116  | 140   |      |       |

| CMR                    | Common mode rejection ratio       | Tmin < T < Tmax                                         | 107  |       |      | dB    |

|                        |                                   | V <sub>OUT</sub> = 0.5 to (V <sub>CC</sub> - 0.5 V)     | 113  | 135   |      | dB    |

| Avd                    | Large signal voltage gain         | Tmin < T < Tmax                                         | 106  |       |      |       |

|                        |                                   | T = 25 °C                                               |      | 60    | 90   |       |

| $V_{OL}$               | Output swing from negative rail   | Tmin < T < Tmax                                         |      |       | 120  |       |

| .,                     |                                   | T = 25 °C                                               |      | 40    | 70   | mV    |

| V <sub>OH</sub>        | Output swing from positive rail   | Tmin < T < Tmax                                         |      |       | 90   |       |

|                        |                                   | V <sub>OUT</sub> connected to VCC+                      |      |       |      |       |

|                        | Isink                             | T = 25 °C                                               | 20   | 26    |      |       |

|                        |                                   | Tmin < T < Tmax                                         | 10   |       |      |       |

| I <sub>OUT</sub>       |                                   | V <sub>OUT</sub> connected to VCC-                      |      | I     | I    | - mA  |

|                        | Isource                           | T = 25 °C                                               | 20   | 29    |      |       |

|                        |                                   | Tmin < T < Tmax                                         | 10   |       |      |       |

|                        |                                   | No load, V <sub>OUT</sub> = V <sub>CC</sub> /2          |      | 650   | 850  |       |

| I <sub>CC</sub>        | Supply current (per channel)      | Tmin < T < Tmax                                         |      |       | 900  | μA    |

|                        |                                   | AC performance                                          |      | 1     | 1    |       |

| 0==                    |                                   | R <sub>L</sub> = 10 kΩ, C <sub>L</sub> = 100 pF         | 1.8  | 3     |      |       |

| GBP                    | Gain bandwidth product            | Tmin < T < Tmax                                         | 1.6  |       |      | MHz   |

| 65                     |                                   | T = 25 °C                                               | 0.8  | 1.8   |      |       |

| SR                     | Slew rate                         | Tmin < T < Tmax                                         | 0.75 |       |      | V/µs  |

| Фт                     | Phase margin                      | R <sub>L</sub> = 10 kΩ, C <sub>L</sub> = 100 pF         |      | 55    |      | 0     |

| Gm                     | Gain margin                       |                                                         |      | 12    |      | dB    |

|                        |                                   | f = 1 kHz                                               |      | 25    |      | nV/√H |

| En                     | Equivalent input noise voltage    | 0.1 to 10 Hz                                            |      | 650   |      | nVpp  |

| THD+N                  | Total harmonic distortion + noise | f = 1 kHz, Gain = 1, V <sub>OUT</sub> = 1 Vpp           |      | 0.004 |      | %     |

| Cs                     | Channel separation                | f = 1 kHz                                               |      | 130   |      | dB    |

DS14357 - Rev 4 page 6/36

| Symbol            | Parameter              | Conditions                            | Min. | Тур. | Max. | Unit |

|-------------------|------------------------|---------------------------------------|------|------|------|------|

| t <sub>rec</sub>  | Overload recovery time | G = -10                               |      | 1    |      | μs   |

| Ts                | Settling time          | 0.1% to final value, G = 1, 10 V step |      | 7    |      | μs   |

| C <sub>load</sub> | Capacitive load drive  | No sustained oscillation              |      | 1    |      | nF   |

<sup>1.</sup> See section Section 5.4.

DS14357 - Rev 4 page 7/36

Table 6. Electrical characteristics  $V_{CC}$  = 36 V,  $V_{icm}$  =  $V_{CC}/2$ ,  $R_L$  = 10 k $\Omega$  connected to  $V_{CC}/2$  (unless otherwise specified)

| Symbol                               | Parameter                      | Conditions                                              | Min. | Тур. | Max. | Unit   |

|--------------------------------------|--------------------------------|---------------------------------------------------------|------|------|------|--------|

|                                      |                                | DC performance                                          |      |      |      |        |

|                                      |                                | V <sub>icm</sub> = V <sub>CC</sub> /2                   |      |      |      |        |

|                                      |                                | T = 25 °C                                               | -20  |      | +20  |        |

| V <sub>IO</sub> Input offset voltage | Innut offert wellens           | Tmin < T < Tmax                                         | -30  |      | +30  |        |

|                                      | Vicm = 0 V                     |                                                         |      |      | μV   |        |

|                                      |                                | T = 25 °C                                               | -20  |      | +20  |        |

|                                      |                                | Tmin < T < Tmax                                         | -30  |      | +30  |        |

| $\Delta V_{IO}/\Delta T_{I}$         | Input offset voltage drift (1) | Tmin < T < Tmax                                         |      | 20   | 100  | nV/°C  |

|                                      | Land his a summer              | T = 25 °C                                               |      |      | 500  |        |

| I <sub>IB</sub>                      | Input bias current             | Tmin < T < Tmax                                         |      |      | 500  | - ^    |

|                                      | Inner to offer a to a company  | T = 25 °C                                               |      |      | 800  | pA     |

| I <sub>IO</sub>                      | Input offset current           | Tmin < T < Tmax                                         |      |      | 800  |        |

| OMB                                  | Common mode rejection          | $V_{icm}$ = 0 to $V_{CC}$ -2 V, $V_{OUT}$ = $V_{CC}$ /2 | 127  | 150  |      | -15    |

| CMR                                  | ratio                          | Tmin < T < Tmax                                         | 120  |      |      | dB     |

| 0)//5                                | Supply voltage rejection       | V <sub>CC</sub> = 4 to 36 V                             | 127  | 138  |      |        |

| SVR                                  | ratio                          | Tmin < T < Tmax                                         | 120  |      |      | dB     |

|                                      |                                | V <sub>OUT</sub> = 0.5 to (V <sub>CC</sub> -0.5 V)      | 124  | 145  |      | dB     |

| Avd                                  | Large signal voltage gain      | Tmin < T < Tmax                                         | 115  |      |      |        |

| .,                                   | Output swing from              | T = 25 °C                                               |      | 140  | 200  |        |

| $V_{OL}$                             | negative rail                  | Tmin < T < Tmax                                         |      |      | 270  | mV     |

| W                                    | Output swing from positive     | T = 25 °C                                               |      | 130  | 200  |        |

| V <sub>OH</sub>                      | rail                           | Tmin < T < Tmax                                         |      |      | 300  |        |

|                                      |                                | V <sub>OUT</sub> connected to VCC+                      |      |      |      |        |

|                                      | Isink                          | T = 25 °C                                               | 20   | 24   |      |        |

|                                      |                                | Tmin < T < Tmax                                         | 12   |      |      | A      |

| lout                                 |                                | V <sub>OUT</sub> connected to VCC-                      |      |      |      | mA.    |

|                                      | Isource                        | T = 25 °C                                               | 20   | 27   |      |        |

|                                      |                                | Tmin < T < Tmax                                         | 12   |      |      |        |

| 1                                    | Supply current (per            | No load, V <sub>OUT</sub> = V <sub>CC</sub> /2          |      | 670  | 850  |        |

| I <sub>CC</sub>                      | channel)                       | Tmin < T < Tmax                                         |      |      | 900  | μΑ     |

|                                      |                                | AC performance                                          | '    |      |      | '      |

| CDD                                  | Coin handwidth and dust        | $R_L = 10 \text{ k}\Omega, C_L = 100 \text{ pF}$        | 1.8  | 3    |      | B 41.1 |

| GBP                                  | Gain bandwidth product         | Tmin < T < Tmax                                         | 1.8  |      |      | MHz    |

| 0.0                                  | Oleverate                      | T = 25 °C                                               | 0.8  | 1.7  |      |        |

| SR                                   | Slew rate                      | Tmin < T < Tmax                                         | 0.6  |      |      | V/µs   |

| Фт                                   | Phase margin                   | $R_L = 10 \text{ k}\Omega, C_L = 100 \text{ pF}$        |      | 54   |      | 0      |

| Gm                                   | Gain margin                    |                                                         |      | 11   |      | dB     |

|                                      | Equivalent input noise         | f = 1 kHz                                               |      | 24   |      | nV/√H  |

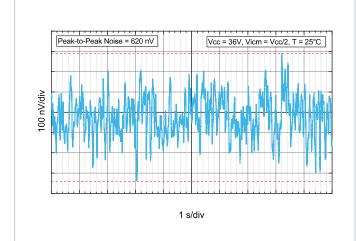

| En                                   | voltage                        | 0.1 to 10 Hz                                            |      | 620  |      | nVpp   |

DS14357 - Rev 4 page 8/36

| Symbol            | Parameter                         | Conditions                                 | Min. | Тур.  | Max. | Unit |

|-------------------|-----------------------------------|--------------------------------------------|------|-------|------|------|

| THD+N             | Total harmonic distortion + noise | f = 1 kHz, G = 1, V <sub>OUT</sub> = 2 Vpp |      | 0.002 |      | %    |

| Cs                | Channel separation                | f = 1 kHz                                  |      | 130   |      | dB   |

| t <sub>rec</sub>  | Overload recovery time            | G = -10                                    |      | 1     |      | μs   |

| T <sub>s</sub>    | Settling time                     | 0.1% to final value, G = 1, 10 V step      |      | 7     |      | μs   |

| C <sub>load</sub> | Capacitive load drive             | No sustained oscillation                   |      | 1     |      | nF   |

<sup>1.</sup> See section Section 5.4.

DS14357 - Rev 4 page 9/36

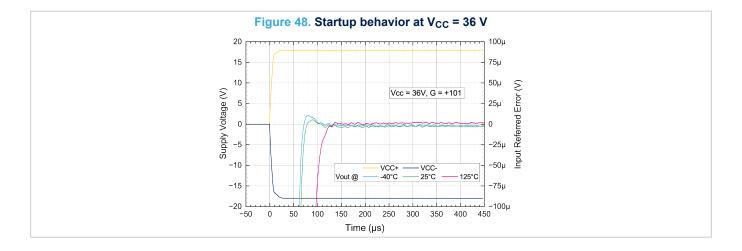

## 4 Typical performance characteristics

DS14357 - Rev 4 page 10/36

Figure 6. Input offset voltage vs. input common mode voltage at  $V_{CC} = 5 \text{ V}$ Vcc = 5V 5 Typical Units Shown

Input Offset Voltage (µV) 0 -5 -10 -15 -20 -Input Common Mode Voltage (V)

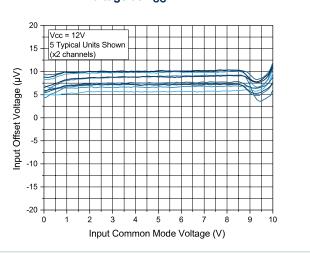

Figure 7. Input offset voltage vs. input common mode voltage at V<sub>CC</sub> = 12 V

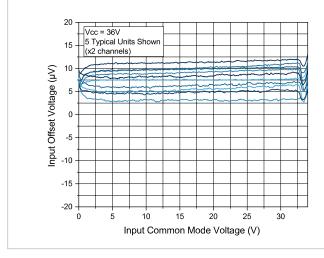

Figure 8. Input offset voltage vs. input common mode voltage at V<sub>CC</sub> = 36 V

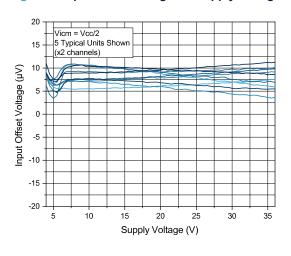

Figure 9. Input offset voltage vs. supply voltage

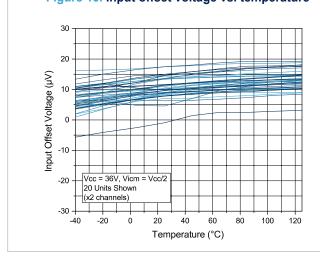

Figure 10. Input offset voltage vs. temperature

Figure 11. Input offset drift distribution

DS14357 - Rev 4 page 11/36

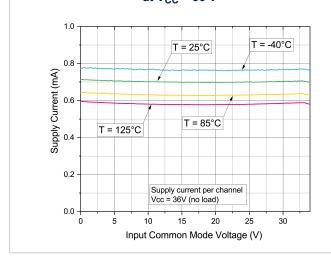

at V<sub>CC</sub> = 5 V

Figure 12. Supply current vs. input common mode voltage | Figure 13. Supply current vs. input common mode voltage at  $V_{CC}$  = 12 V

Figure 14. Supply current vs. input common mode voltage at V<sub>CC</sub> = 36 V

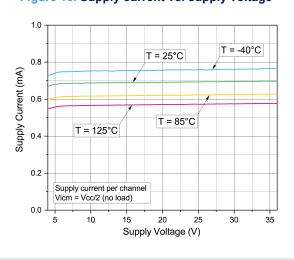

Figure 15. Supply current vs. supply voltage

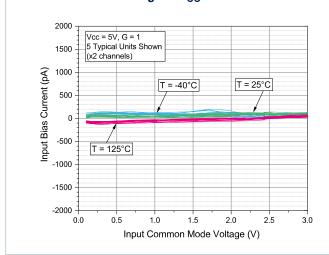

Figure 16. Input bias current vs. input common mode voltage at V<sub>CC</sub> = 5 V

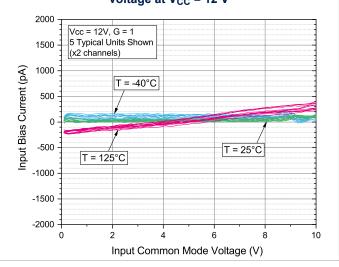

Figure 17. Input bias current vs. input common mode voltage at V<sub>CC</sub> = 12 V

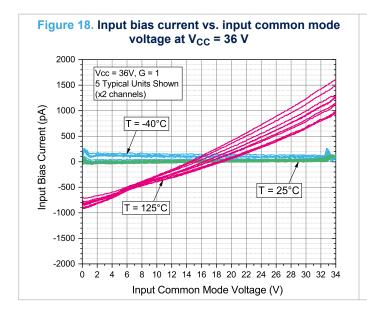

DS14357 - Rev 4 page 12/36

Figure 19. Output current vs. output voltage at  $V_{CC} = 5 \text{ V}$   $\begin{array}{c}

40 \\

30 \\

\hline

20 \\

\hline

10 \\

\hline

10 \\

\hline

-20 \\

\hline

-30 \\

\hline

-40 \\

\hline

-20 \\

\hline

-20 \\

\hline

-30 \\

\hline

-40 \\

\hline

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\

-20 \\$

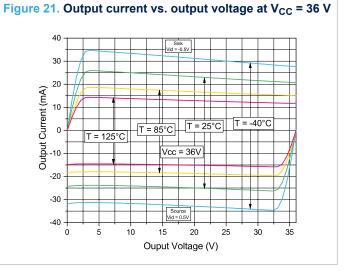

Figure 20. Output current vs. output voltage at  $V_{CC}$  = 12 V

DS14357 - Rev 4 page 13/36

Figure 24. CMRR and PSRR vs. frequency at V<sub>CC</sub> = 12 V

10k

Frequency (Hz)

100k

1M

PSRR-

100

40

10

Figure 25. CMRR and PSRR vs. frequency at V<sub>CC</sub> = 36 V Vcc = 36V, Vicm = Vcc/2 G = +101 120 Rejection Ratio (dB) 100 80 CMRR 60 PSRR-PSRR-40 10 100 100k 1M Frequency (Hz)

Figure 26. Bode plot at  $V_{CC} = 5 \text{ V}$ 60 40 110 -90 20 Gain (dB) Phase ( -20 -270 Vcc = 5V, Vicm = Vcc/2, T -40 G = 101 (1kΩ / 100kΩ) RI = 10kΩ, CI = 100pF, VrI = Vcc/2 -360 -60 -10<sup>2</sup> 10<sup>3</sup> 10<sup>5</sup> 10<sup>7</sup> 10<sup>4</sup> 10<sup>6</sup> Frequency (Hz)

DS14357 - Rev 4 page 14/36

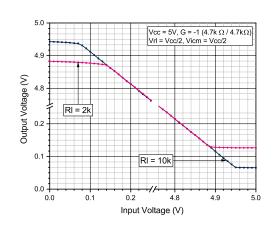

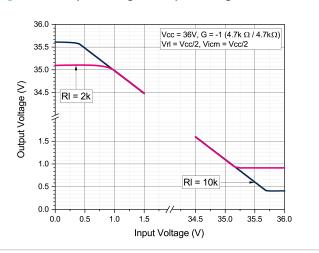

Figure 30. Output voltage vs. input voltage at  $V_{CC}$  = 5 V

Figure 31. Output voltage vs. input voltage at V<sub>CC</sub> = 36 V

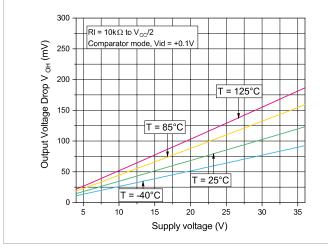

Figure 32. Output drop voltage V<sub>OH</sub> vs. supply voltage

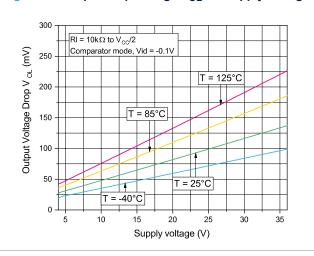

Figure 33. Output drop voltage V<sub>OL</sub> vs. supply voltage

Figure 34. Noise vs. time at V<sub>CC</sub> = 36 V

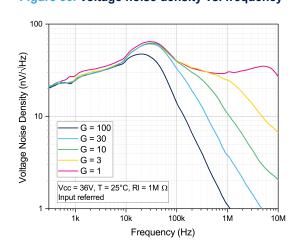

Figure 35. Voltage noise density vs. frequency

DS14357 - Rev 4 page 15/36

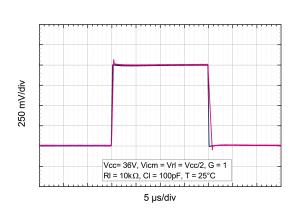

25 mV/div

Vcc= 36V, Vicm = Vrl = Vcc/2, G = 1 RI = 10kΩ, CI = 100pF, T = 25°C

1 µs/div

Figure 36. Small signal response at V<sub>CC</sub> = 36 V

Figure 37. Large signal response at  $V_{CC}$  = 36 V

Figure 38. Settling time on negative input step 10 Vcc = 36V, G = -1, T = 25°C 8 0.01%, 10V Input Negative Step Δ From Final Value (mV) 4 2 0 -2 -4 -6 -8 ----- Average of 10 Acquisitions -10 10µ 20μ 30μ 40µ 60µ 50u

Time (µs)

Figure 39. Settling time on positive input step 10 Vcc = 36V, G = -1, T = 25°C 0.01%, 10V Input Positive Step From Final Value (mV) 2 0 -2 -6 -8 - Average of 10 Acquisitions -10 0 10µ 20μ 30μ 60µ 40u Time (µs)

DS14357 - Rev 4 page 16/36

Figure 44. Channel separation vs. frequency

160

140

120

80

100

80

Vcc = 36V, Vicm = Vcc/2, T = 25°C

G = 101, Vin = 0.5Vpp

40

10 100 1k 10k 100k 1M 10M 100M

Frequency (Hz)

DS14357 - Rev 4 page 17/36

DS14357 - Rev 4 page 18/36

### 5 Application information

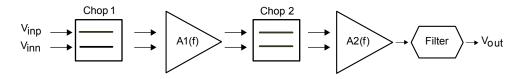

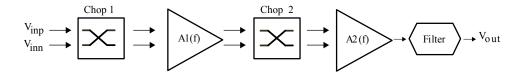

#### 5.1 Chopper operation theory

The TSB182 is a very high precision CMOS device. It achieves a low offset drift and no 1/f noise thanks to its chopper architecture. Chopper-stabilized amps constantly correct low-frequency errors across the inputs of the amplifier.

#### 5.1.1 Time domain

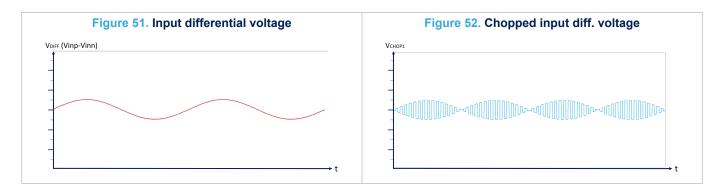

The basis of the chopper amplifier is realized in two steps. These steps are synchronized thanks to a clock running at 400 kHz.

Figure 49. Block diagram in the time domain (step 1)

Figure 50. Block diagram in the time domain (step 2)

Figure 49 shows step 1, the first clock cycle, where Vio is amplified in the normal way.

Figure 50 shows step 2, the second clock cycle, where Chop1 and Chop2 swap paths. At this time, the  $V_{io}$  is amplified in a reverse way as compared to step 1.

At the end of these two steps, the average  $V_{io}$  is close to zero.

The A2(f) amplifier has a small impact on the  $V_{io}$  because the  $V_{io}$  is expressed as the input offset and is consequently divided by A1(f).

The averaging of the input offset could only be done by Chop2 stage, but for amplifying the input signal without distorting it, Chop1 stage is needed so that the input signal is always amplified the same way, and not alternatively up and down as per the Vio.

Here is an example of the time representation of a signal going through the system depicted by Figure 49:

DS14357 - Rev 4 page 19/36

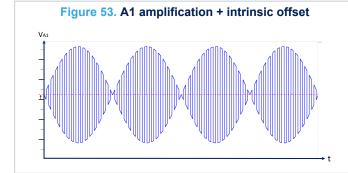

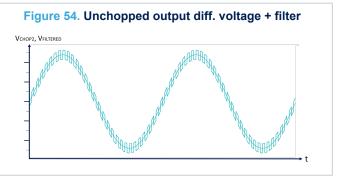

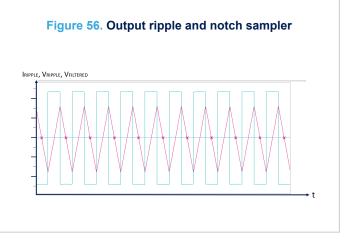

The DC offset and low-frequency noise introduced by A1 are converted to the residual square ripple seen on Figure 54. Due to many non-idealities of the notch filter and some complications in the reconstruction of the signal, the output of the TSB182 operational amplifier can show some of the switching characteristic of the chopping stages, including output ripple and converging steps, especially in some configurations where a fast transient is applied at the input or when driven out of saturation. These non-analog behaviors are drawbacks inherent to the chopper architecture, hence special efforts were made to reduce them as much as possible, such as lowering the output ripple down to the TSB182 operational amplifier's output noise level.

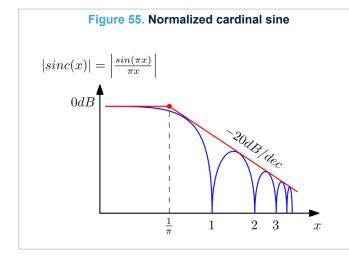

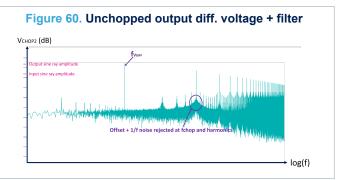

The ripple is in fact not at first visible in terms of steps but is more likely a triangular waveform, as the first amplifying stage is driving its output capacitor in current. The ripple is then reduced by a notch filter, a sample-and-hold system taking a picture of the voltage each period of the triangle wave. If tuned wisely, this notch filter can dramatically reduce the output ripple down to a very low level which is acceptable compared to the achieved  $V_{io}$  performance. This is made possible thanks to the frequency characteristics of the notch filter, totally rejecting some frequencies (in theory), as shown in Figure 55. The filter is made so that the chopping frequency and its harmonics are canceled out, thus eliminating the ripple, and removing the remaining errors that were at or close to the chopping frequency (1/f noise).

DS14357 - Rev 4 page 20/36

#### 5.1.2 Frequency domain

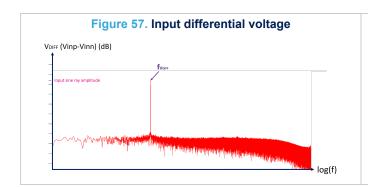

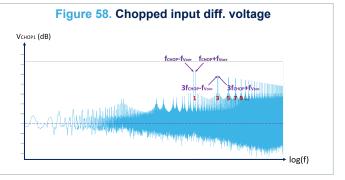

The frequency domain gives a more accurate vision of the chopper-stabilized amplifier architecture, especially due to the chopping circuits it holds.

Figure 59. A1 amplification + intrinsic offset

Val (dB)

Amplification

+ DC Offset (not shown)

log(f)

When chopping the input signal, its frequency gets shifted around the switching frequency of the chop switches (chopping frequency) and all its odd harmonics (frequency signature of a square signal). This enables the signal to be frequency differentiated from the errors introduced by the first amplifying stage A1 (DC offset and flicker noise).

After being amplified, the second chopper stage (Chop 2) demodulates the signal to its original frequency while shifting low frequency errors around the chopping frequency.

These remaining spikes are then faded out by the notch filter, removing the errors introduced by the amplifying stage.

#### 5.2 ESD protection

Internal ESD diodes are present on every output and input pin of the TSB182 ensuring a safe conductive path in case of electrostatic discharge. Should the voltage on the pin exceed the power supply, its ESD diode will become conductive and current will flow through it. This path is designed to resist ESD discharges, however the input pins (IN1-, IN2-, IN2+) are not rated to support a continuous (DC) current over 10 mA. In such cases, a limiting resistor must be added to ensure that the input current absolute maximum rating (AMR) is respected.

In addition, anti-parallel diodes have been added for protecting the safe operating area of the input MOS transistors. These diodes shown on Figure 61 limit the differential input voltage to about 0.7 V. Hence, the input current shares a relation with the differential input voltage: at any time, the differential input voltage should be limited to 0.7 V or the input current to 10 mA, whichever comes first.

DS14357 - Rev 4 page 21/36

Figure 61. Differential anti-parallel diodes and ESD diodes

This is particularly needed when using the TSB182 in a degraded mode as a comparator, where we recommended putting equal resistors on both inputs, sized for limiting the current below 10 mA.

This can also be needed when driving the TSB182 with fast large signals, where the output can't respond instantaneously, creating a differential voltage the time during which the output has not yet reached the input setpoint.

Note that in follower mode, a resistor can be added either on the IN+ pin or in the feedback loop, the difference being that in the feedback loop the resistance will form an RC filter with the input capacitance that can lead to poor stability. We recommend lowering the feedback resistance as much as possible with respect to the maximum 10 mA input current compliance.

Note that differential diodes can also affect the input when short-circuit currents are reached, and the output is not able to maintain the right voltage level.

#### 5.3 EMI filter

Electromagnetic interference (EMI) is a phenomenon where electronic devices create and are affected by electromagnetic fields. In practice, for operational amplifiers, it generally refers to radiated or conducted electromagnetic waves interfering with (for instance, adding to) the signal on one or multiple pins of the operational amplifier and affecting the performances of the operational amplifier (for instance, its input offset voltage). It creates an error on the TSB182 output that wouldn't exist without these interferences.

This is a well-known effect, however difficult to tackle as there are many sources of electromagnetic interferences.

That is why TSB182 comes with built-in EMI filters that help to minimize the output error created by these interferences.

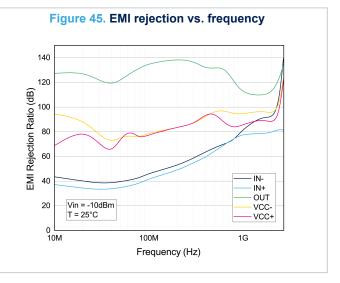

This sensitivity to EMI is measured from 10 MHz to 2.4 GHz and is reported on Figure 45.

For information, TSB182's EMI filters are composed of a single RC network present on both input pins, with R = 1  $k\Omega$  and C = 1.6 pF. It creates a passive filtering with a cutoff frequency around 100 MHz, optimized for maximizing its impact on EMI rejection, and minimizing its impact on TSB182 stability and noise.

#### 5.4 Input offset voltage drift over temperature

The operational amplifier is one of the main circuits of the signal conditioning chain, and the amplifier input offset is a major contributor to the chain accuracy.

The maximum input voltage drift variation over temperature specified in the electrical characteristics Table 4, Table 5, and Table 6 is defined as the offset variation from -40°C to 125°C.

$$\frac{\Delta V_{io}}{\Delta T} = \left(\frac{V_{io} - 40^{\circ}C - V_{io} \cdot 125^{\circ}C}{-40^{\circ}C - 125^{\circ}C}\right) \tag{1}$$

The datasheet maximum value is guaranteed by measurements on a representative sample size ensuring a C<sub>pk</sub> (process capability index) greater than 1.3.

The value reported in the datasheet is the highest value of the |min| and |max| calculated to get this Cpk.

DS14357 - Rev 4 page 22/36

The signal chain accuracy at 25°C can be compensated during production at application level. In this case, the maximum input offset voltage drift over temperature enables the system designer to anticipate the effect of temperature variations. For this purpose can be considered the Table 7 depicting the minimum and maximum values for such drifts computed between T = (Tmin or Tmax) and T = 25°C.

Table 7. Input offset voltage drifts relative to T = 25°C

| $rac{\Delta_{V}{io}}{\Lambda_{T}}$      | T = -40°C to T = 25°C | T = 25°C to T = 125°C |

|------------------------------------------|-----------------------|-----------------------|

| $\frac{\overline{\Lambda_T}}{\Lambda_T}$ | min / max             | min / max             |

| V <sub>CC</sub> = 5 V                    | -70 / 112             | -38 / 114             |

| V <sub>CC</sub> = 12 V                   | -66 / 142             | -47 / 81              |

| V <sub>CC</sub> = 36 V                   | -75 / 173             | -39 / 89              |

The input offset drift values shown in table 7 are computed from the input offset voltage measurements at three temperatures (-40 °C, 25 °C, 125 °C) using the following equation:

$$\frac{\Delta V_{io}}{\Delta T} = \left(\frac{V_{io\_T} - V_{io\_25^{\circ}C}}{T - 25^{\circ}C}\right)_{T = -40^{\circ}C} \text{ or } 125^{\circ}C$$

(2)

These measurements were performed on a representative sample size ensuring a  $C_{pk}$  (process capability index) greater than 1.3.

#### 5.5 Maximum power dissipation

The usable output load current drive is limited by the maximum power dissipation allowed by the device package. The absolute maximum junction temperature for the TSB182 is 150 °C. The junction temperature can be estimated as follows:

$$T_I = P_D \times \theta_{IA} + T_A \tag{3}$$

T<sub>J</sub> is the die junction temperature

$P_{\text{D}}$  is the power dissipated in the package

$\theta_{JA}$  is the junction to thermal resistance of the package

T<sub>A</sub> is the ambient temperature

The power dissipated in the package  $P_D$  is the sum of the quiescent power dissipated and the power dissipated by the output stage transistor. It is calculated as follows:

$P_D = (V_{CC} \times I_{CC}) + (V_{CC+} - V_{OUT}) \times I_{OUT}$  when the op amp is sourcing the current.

$P_D = (V_{CC} \times I_{CC}) + (V_{OUT} - V_{CC}) \times I_{OUT}$  when the op amp is sinking the current.

Do not exceed the 150 °C maximum junction temperature for the device. Exceeding the junction temperature limit can cause degradation in the parametric performance or even destroy the device.

The TSB182 short-circuit current is designed in accordance with the bandwidth for sustaining specific capacitive or resistive loads. It is not intended for delivering its maximum output current continuously. There is no other guarantee than respecting the maximum junction temperature of the device.

#### 5.6 Unused channel

When one of the two channels of the TSB182 is not used, it must be properly connected in order to avoid internal oscillations that can negatively impact the signal integrity on the other channel, as well as the current consumption. Two different configurations can be used:

Gain configuration: the channel can be set in gain, the input can be set to any voltage within the V<sub>icm</sub> operating range.

Buffer configuration: the channel can be set in buffer configuration, with the input set to any voltage within the operating range.

DS14357 - Rev 4 page 23/36

Comparator configuration: the channel can be set to a comparator configuration (without feedback). In this case, positive and negative inputs can be set to any voltage provided that the current on both inputs is limited to 10 mA. The differential voltage will start activating input differential diodes (see ESD protection paragraph in Section 5.2: ESD protection) when reaching a certain threshold (about 0.7 V, can vary in temperature) and must be significantly greater than the input-referred noise (we recommend 100 mV) for ensuring a stable output state.

#### 5.7 PCB layout recommendations

Particular attention must be paid to the layout of the PCB tracks connected to the amplifier, load and power supply. It is good practice to use short and wide PCB traces to minimize voltage drops and parasitic inductance. To minimize parasitic impedance over the entire surface, a multi-via technique that connects the bottom and top layer ground planes together in many locations is often used.

The copper traces that connect the output pins to the load and supply pins should be as wide as possible to minimize trace resistance.

A ground plane generally helps to reduce EMI, which is why it is generally recommended to use a multilayer PCB and use the ground plane as a shield to protect the internal track. In this case, pay attention to separate the digital from the analog ground and avoid any ground loop.

Place external components as close as possible to the op amp and keep the gain resistances,  $R_f$  and  $R_g$ , close to the inverting pin to minimize parasitic capacitances.

DS14357 - Rev 4 page 24/36

#### 5.8 Optimized application recommendation

The TSB182 is based on a chopper architecture. As the device includes internal switching circuitry, it is strongly recommended to place a 0.1 µF capacitor as close as possible to the supply pins.

A good decoupling has several advantages for an application. First, it helps to reduce electromagnetic interference. Due to the modulation of the chopper, the decoupling capacitance also helps to reject the small ripple that may appear on the output.

#### 5.9 Basic applications

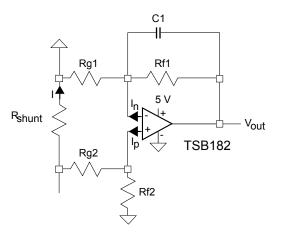

#### Low-side current sensing schematic

Power management mechanisms are found in most electronic systems. Current sensing is useful for protecting applications. The low-side current sensing method consists of placing a sense resistor between the load and the circuit ground. The resulting voltage drop is amplified using the TSB182 (see Figure 62).

Figure 62. Low-side current sensing schematic

Vout can be expressed as follows:

$$V_{out} = R_{shunt} \times I \left( 1 - \frac{R_{g2}}{R_{g2} + R_{f2}} \right) \left( 1 + \frac{R_{f1}}{R_{g1}} \right) - V_{io} \left( 1 + \frac{R_{f1}}{R_{g1}} \right) \tag{4}$$

Assuming that  $R_{f2} = R_{f1} = R_f$  and  $R_{g2} = R_{g1} = R_g$ , Equation 3 can be simplified as follows:

$$V_{out} = R_{shunt} \times I\left(\frac{R_f}{R_g}\right) - V_{io}\left(1 + \frac{R_f}{R_g}\right) \tag{5}$$

Using the TSB182 operational amplifier for low-side current sensing minimizes the error due to  $V_{IO}$  and enables a measurement with better accuracy.

Therefore, for the same accuracy, the shunt resistor can be chosen with a lower value, resulting in lower power dissipation, lower drop in the ground path, and lower cost.

Particular attention must be paid to the matching and precision of  $R_{g1}$ ,  $R_{g2}$ ,  $R_{f1}$ , and  $R_{f2}$ , to maximize the accuracy of the measurement.

The circuit gain must be chosen in line with the minimum operational shunt current and the TSB182 open loop gain above output saturation.

DS14357 - Rev 4 page 25/36

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

DS14357 - Rev 4 page 26/36

## 6.1 SO8 package information

SEATING PLANE

C

SECTION B-B

BASE METAL

DO10023\_S0-807\_fig2\_Rev10

Figure 63. SO8 package outline

Table 8. SO8 package mechanical data

| Dim - |      | mm   |      |

|-------|------|------|------|

| Dilli | Min. | Тур. | Max. |

| Α     |      |      | 1.75 |

| A1    | 0.10 |      | 0.25 |

| A2    | 1.25 |      |      |

| b     | 0.31 |      | 0.51 |

| b1    | 0.28 |      | 0.48 |

| С     | 0.10 |      | 0.25 |

| c1    | 0.10 |      | 0.23 |

| D     | 4.80 | 4.90 | 5.00 |

| Е     | 5.80 | 6.00 | 6.20 |

| E1    | 3.80 | 3.90 | 4.00 |

| е     |      | 1.27 |      |

| h     | 0.25 |      | 0.50 |

| L     | 0.40 |      | 1.27 |

| L1    |      | 1.04 |      |

| L2    |      | 0.25 |      |

| k     | 0°   |      | 8°   |

| ccc   |      |      | 0.10 |

DS14357 - Rev 4 page 27/36

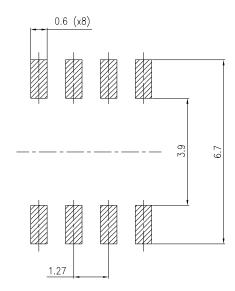

Figure 64. SO8 recommended footprint

DS14357 - Rev 4 page 28/36

## 6.2 MiniSO8 package information

Figure 65. MiniSO8 package outline

Table 9. MiniSO8 package mechanical data

PIN 1 IDENTIFICATION

| Dim   | m    | m    |      | Inches |       |       |

|-------|------|------|------|--------|-------|-------|

| Dilli | Min. | Тур. | Max. | Min.   | Тур.  | Max.  |

| А     |      |      | 1.1  |        |       | 0.043 |

| A1    | 0    |      | 0.15 | 0      |       | 0.006 |

| A2    | 0.75 | 0.85 | 0.95 | 0.03   | 0.033 | 0.037 |

| b     | 0.22 |      | 0.4  | 0.009  |       | 0.016 |

| С     | 0.08 |      | 0.23 | 0.003  |       | 0.009 |

| D     | 2.8  | 3    | 3.2  | 0.11   | 0.118 | 0.126 |

| Е     | 4.65 | 4.9  | 5.15 | 0.183  | 0.193 | 0.203 |

| E1    | 2.8  | 3    | 3.1  | 0.11   | 0.118 | 0.122 |

| е     |      | 0.65 |      |        | 0.026 |       |

| L     | 0.4  | 0.6  | 0.8  | 0.016  | 0.024 | 0.031 |

| L1    |      | 0.95 |      |        | 0.037 |       |

| L2    |      | 0.25 |      |        | 0.01  |       |

| k     | 0°   |      | 8°   | 0°     |       | 8°    |

| ccc   |      |      | 0.1  |        |       | 0.004 |

DS14357 - Rev 4 page 29/36

# 7 Ordering information

Table 10. Order code

| Order code     | Package | Packing       | Marking  |

|----------------|---------|---------------|----------|

| TSB182IDT      | SO8     |               | TSB182I  |

| TSB182IYDT (1) |         | Tana and real | TSB182IY |

| TSB182IST      | MiniSO8 | Tape and reel | K238     |

| TSB182IYST (1) |         |               | K239     |

Qualified and characterized according to AEC Q100 and Q003 or equivalent, advanced screening according to AEC Q001 & Q002 or equivalent.

DS14357 - Rev 4 page 30/36

### **Revision history**

**Table 11. Document revision history**

| Date        | Revision | Changes                                                                                                                     |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| 07-Jul-2023 | 1        | Initial release.                                                                                                            |

| 20-Sep-2023 | 2        | Minor text changes.                                                                                                         |

| 24-Jan-2024 | 3        | Added $ \Delta~V_{IO}/\Delta T $ condition in Table 4, Table 5, Table 6 and new section Section 5: Application information. |

| 12-Mar-2024 | 4        | Minor text changes in Section 5.1.1.                                                                                        |

DS14357 - Rev 4 page 31/36

### **Contents**

| 1  | Pin        | descript               | tion                                           | 2  |  |  |  |  |

|----|------------|------------------------|------------------------------------------------|----|--|--|--|--|

| 2  |            |                        | blute maximum ratings and operating conditions |    |  |  |  |  |

| 3  |            | trical characteristics |                                                |    |  |  |  |  |

| 4  | Турі       | cal perf               | formance characteristics                       |    |  |  |  |  |

| 5  | Арр        | lication               | information                                    |    |  |  |  |  |

|    | 5.1        | Chopp                  | per operation theory                           | 19 |  |  |  |  |

|    |            | 5.1.1                  | Time domain                                    |    |  |  |  |  |

|    |            | 5.1.2                  | Frequency domain                               | 21 |  |  |  |  |

|    | 5.2        | ESD p                  | protection                                     | 21 |  |  |  |  |

|    | <b>5.3</b> | EMI filt               | ter                                            | 22 |  |  |  |  |

|    | 5.4        | Input o                | offset voltage drift over temperature          | 22 |  |  |  |  |

|    | 5.5        | Maxim                  | num power dissipation                          | 23 |  |  |  |  |

|    | 5.6        | Unuse                  | ed channel                                     | 23 |  |  |  |  |

|    | 5.7        | PCB la                 | ayout recommendations                          | 24 |  |  |  |  |

|    | 5.8        | Optimi                 | ized application recommendation                | 25 |  |  |  |  |

|    | 5.9        | Basic a                | applications                                   | 25 |  |  |  |  |

| 6  | Pac        | kage inf               | formation                                      | 26 |  |  |  |  |

|    | 6.1        | SO8 pa                 | package information                            | 27 |  |  |  |  |

|    | 6.2        | MiniSC                 | O8 package information                         | 29 |  |  |  |  |

| 7  | Ord        |                        | formation                                      |    |  |  |  |  |

| Re | vision     | history                | ′                                              | 31 |  |  |  |  |

|    |            |                        |                                                |    |  |  |  |  |

### **List of tables**

| Table 1.  | Pin description                                                                                                                                  | . 2 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings                                                                                                                         | . 3 |

| Table 3.  | Operating conditions                                                                                                                             | . 3 |

| Table 4.  | Electrical characteristics $V_{CC}$ = 5 V, $V_{icm}$ = $V_{CC}/2$ , $R_L$ = 10 k $\Omega$ connected to $V_{CC}/2$ (unless otherwise specified).  |     |

| Table 5.  | Electrical characteristics $V_{CC}$ = 12 V, $V_{icm}$ = $V_{CC}/2$ , $R_L$ = 10 k $\Omega$ connected to $V_{CC}/2$ (unless otherwise specified). | . 6 |

| Table 6.  | Electrical characteristics $V_{CC}$ = 36 V, $V_{icm}$ = $V_{CC}/2$ , $R_L$ = 10 k $\Omega$ connected to $V_{CC}/2$ (unless otherwise specified). | . 8 |

| Table 7.  | Input offset voltage drifts relative to T = 25°C                                                                                                 | 23  |

| Table 8.  | SO8 package mechanical data                                                                                                                      | 27  |

| Table 9.  | MiniSO8 package mechanical data                                                                                                                  | 29  |

| Table 10. | Order code                                                                                                                                       | 30  |

| Table 11. | Document revision history                                                                                                                        | 31  |

DS14357 - Rev 4 page 33/36

# List of figures

| Figure 1.                | Pin connections (top view)                                                                            |    |

|--------------------------|-------------------------------------------------------------------------------------------------------|----|

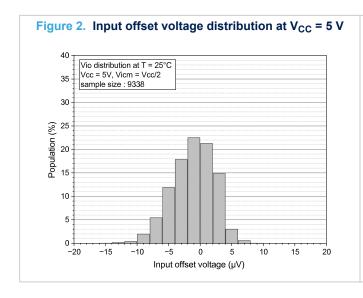

| Figure 2.                | Input offset voltage distribution at V <sub>CC</sub> = 5 V                                            | 10 |

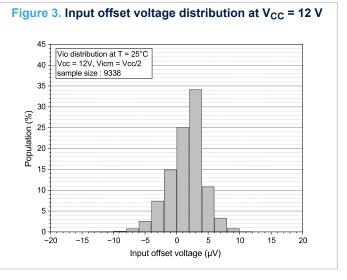

| Figure 3.                | Input offset voltage distribution at V <sub>CC</sub> = 12 V                                           | 10 |

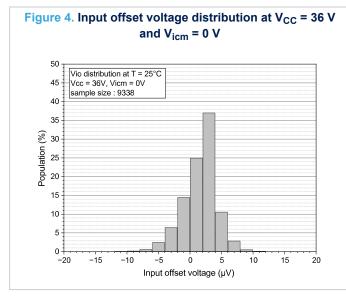

| Figure 4.                | Input offset voltage distribution at V <sub>CC</sub> = 36 V and V <sub>icm</sub> = 0 V                | 10 |

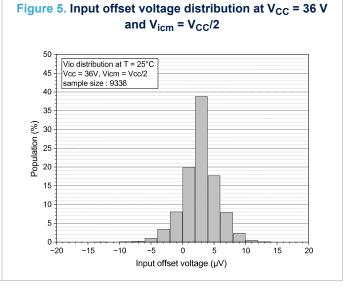

| Figure 5.                | Input offset voltage distribution at V <sub>CC</sub> = 36 V and V <sub>icm</sub> = V <sub>CC</sub> /2 | 10 |

| Figure 6.                | Input offset voltage vs. input common mode voltage at V <sub>CC</sub> = 5 V                           |    |

| Figure 7.                | Input offset voltage vs. input common mode voltage at V <sub>CC</sub> = 12 V                          |    |

| Figure 8.                | Input offset voltage vs. input common mode voltage at V <sub>CC</sub> = 36 V                          |    |

| Figure 9.                | Input offset voltage vs. supply voltage                                                               |    |

| Figure 3.                | Input offset voltage vs. temperature                                                                  |    |

| Figure 11.               | Input offset drift distribution                                                                       |    |

| Figure 12.               | Supply current vs. input common mode voltage at V <sub>CC</sub> = 5 V                                 |    |

| Figure 13.               | Supply current vs. input common mode voltage at V <sub>CC</sub> = 12 V                                |    |

| Figure 14.               | Supply current vs. input common mode voltage at V <sub>CC</sub> = 36 V                                |    |

| Figure 15.               | Supply current vs. supply voltage                                                                     |    |

| Figure 16.               | Input bias current vs. input common mode voltage at V <sub>CC</sub> = 5 V                             |    |

| Figure 17.               | Input bias current vs. input common mode voltage at $V_{CC} = 3 \text{ V}$                            |    |

|                          |                                                                                                       |    |

| Figure 18.               | Input bias current vs. input common mode voltage at V <sub>CC</sub> = 36 V                            |    |

| Figure 19.               | Output current vs. output voltage at V <sub>CC</sub> = 5 V                                            |    |

| Figure 20.               | Output current vs. output voltage at V <sub>CC</sub> = 12 V                                           |    |

| Figure 21.               | Output current vs. output voltage at V <sub>CC</sub> = 36 V                                           |    |

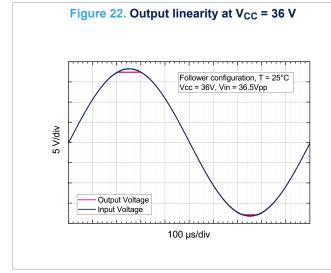

| Figure 22.               | Output linearity at V <sub>CC</sub> = 36 V                                                            |    |

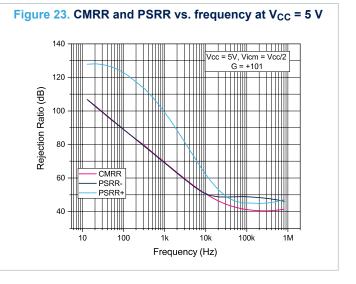

| Figure 23.               | CMRR and PSRR vs. frequency at V <sub>CC</sub> = 5 V                                                  | 13 |

| Figure 24.               | CMRR and PSRR vs. frequency at V <sub>CC</sub> = 12 V                                                 | 14 |

| Figure 25.               | CMRR and PSRR vs. frequency at V <sub>CC</sub> = 36 V                                                 | 14 |

| Figure 26.               | Bode plot at V <sub>CC</sub> = 5 V                                                                    | 14 |

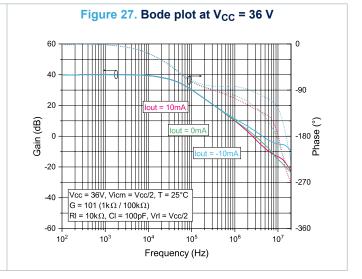

| Figure 27.               | Bode plot at V <sub>CC</sub> = 36 V                                                                   | 14 |

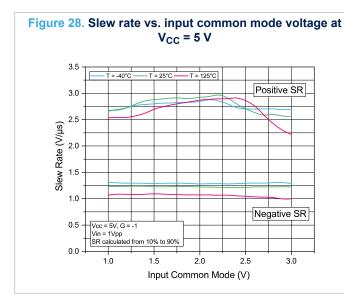

| Figure 28.               | Slew rate vs. input common mode voltage at V <sub>CC</sub> = 5 V                                      | 14 |

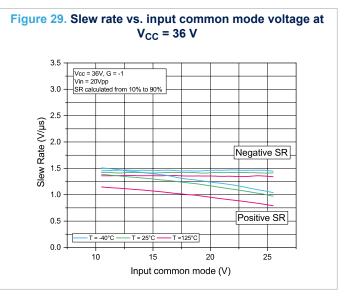

| Figure 29.               | Slew rate vs. input common mode voltage at V <sub>CC</sub> = 36 V                                     |    |

| Figure 30.               | Output voltage vs. input voltage at V <sub>CC</sub> = 5 V                                             |    |

| Figure 31.               | Output voltage vs. input voltage at V <sub>CC</sub> = 36 V                                            |    |

| Figure 32.               | Output drop voltage V <sub>OH</sub> vs. supply voltage                                                |    |

| Figure 33.               | Output drop voltage V <sub>OL</sub> vs. supply voltage                                                |    |

| Figure 34.               | Noise vs. time at $V_{CC}$ = 36 $V_{CC}$ =                                                            |    |

| Figure 34.<br>Figure 35. | Voltage noise density vs. frequency                                                                   |    |

| Figure 35.<br>Figure 36. | Small signal response at V <sub>CC</sub> = 36 V                                                       |    |

| Figure 37.               | Large signal response at V <sub>CC</sub> = 36 V                                                       |    |

|                          |                                                                                                       |    |

| Figure 38.               | Settling time on negative input step                                                                  |    |

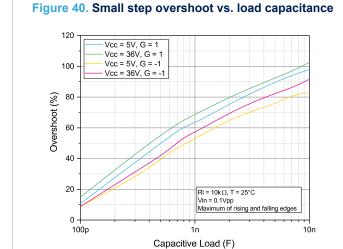

| Figure 39.<br>Figure 40. | Settling time on positive input step                                                                  |    |

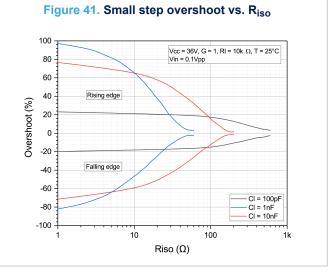

| Figure 40.<br>Figure 41. | Small step overshoot vs. R <sub>iso</sub>                                                             |    |

| Figure 41.               |                                                                                                       |    |

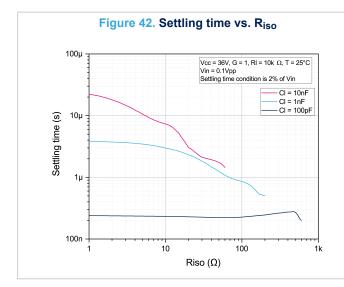

|                          | Settling time vs. R <sub>iso</sub>                                                                    |    |

| Figure 43.               | THD vs. frequency                                                                                     |    |

| Figure 44.<br>Figure 45. | Channel separation vs. frequency                                                                      |    |

| Figure 45.<br>Figure 46. | Positive overvoltage recovery                                                                         |    |

| Figure 40.<br>Figure 47. | Negative overvoltage recovery                                                                         |    |

| Figure 48.               | Startup behavior at V <sub>CC</sub> = 36 V.                                                           |    |

| Figure 49.               | Block diagram in the time domain (step 1)                                                             |    |

| 9410 70.                 | Dioon diagram in the time demain (step 1)                                                             |    |

DS14357 - Rev 4

#### **TSB182**

#### List of figures

| Figure 50. | Block diagram in the time domain (step 2)        | 19 |

|------------|--------------------------------------------------|----|

| Figure 51. | Input differential voltage                       | 19 |

| Figure 52. | Chopped input diff. voltage                      | 19 |

| Figure 53. | A1 amplification + intrinsic offset              | 20 |

| Figure 54. | Unchopped output diff. voltage + filter          | 20 |

| Figure 55. | Normalized cardinal sine                         | 20 |

| Figure 56. | Output ripple and notch sampler                  | 20 |

| Figure 57. | Input differential voltage                       | 21 |

| Figure 58. | Chopped input diff. voltage                      | 21 |

| Figure 59. | A1 amplification + intrinsic offset              | 21 |

| Figure 60. | Unchopped output diff. voltage + filter          | 21 |

| Figure 61. | Differential anti-parallel diodes and ESD diodes | 22 |

| Figure 62. | Low-side current sensing schematic               | 25 |

| Figure 63. | SO8 package outline                              | 27 |

| Figure 64. | SO8 recommended footprint                        | 28 |

| Figure 65. | MiniSO8 package outline                          | 29 |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

DS14357 - Rev 4 page 36/36