MARCH 1985 – REVISED JANUARY 1986

- STL-AS Technology

- Parallel 8-Bit ALU with Expansion Inputs and Outputs

- 13 Arithmetic and Logic Functions

- 8 Conditional Shifts (Single and Double Length)

- 9 Instructions that Manipulate Bytes

- 4 Instructions that Manipulate Bits

- Add and Subtract Immediate Instructions

- Absolute Value Instruction

- Signed Magnitude to/from Two's Complement Conversion

- Single- and Double-Length Normalize

- Select Functions

- Signed and Unsigned Divides with Overflow Detection; Input does not Need to be Prescaled

- Signed, Mixed, and Unsigned Multiplies

- Three-Operand, 16-Word Register File

- Full Carry Look Ahead Support

- Sign, Carry Out, Overflow, and Zero-Detect Status Capabilities

- Excess-3 BCD Arithmetic

- Internal Shift Multiplexers that Eliminate the Need for External Shift Control Parts

- ALU Bypass Path to Increase Speeds of Multiply, Divide, and Normalize Instructions and to Provide New Instructions such as Bit Set, Bit Reset, Bit Test, Byte Subtract, Byte Add, and Byte Logical

- 3-Operand Register Files to Allow an Operation and a Move Instruction to be Combined

- Byte Select Controlled by External 3-State Buffers that may be Eliminated if Bit and Byte Manipulation are not Needed

- Bit and Byte Masks that are Shared with Register Address Fields to Minimize Control Store Word Width

- 3 Data Input/Output Paths to Maximize Data Throughput

#### description

These 8-bit Advanced Schottky TTL integrated circuits are designed to implement high performance digital computers or controllers. An architecture and instruction set has been chosen that supports a fast system clock, a narrow micro-code word width, and a high system throughput. The powerful instruction set allows high-speed system architecture to be implemented and also allows an existing system's performance to be upgraded while protecting software investments. These processors are designed to be cascadable to any word width 16 bits or greater.

The SN54AS888 is characterized for operation over the full military temperature range of  $-55\,^{\circ}$ C to 125  $^{\circ}$ C. The SN74AS888 and SN74AS888-1 are characterized for operation from 0  $^{\circ}$ C to 70  $^{\circ}$ C.

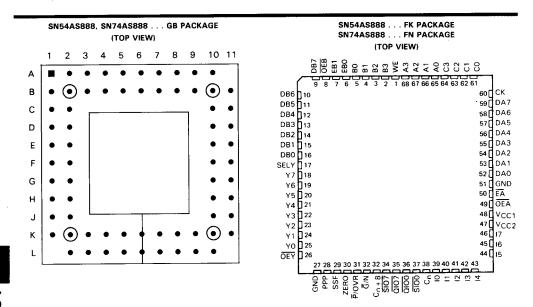

Package options include both plastic and ceramic chip carriers in addition to a 68-pin grid array ceramic package.

#### **GB PACKAGE PIN ASSIGNMENTS**

| PIN  | NAME             | PIN  | NAME             | PIN  | NAME   | PIN  | NAME |

|------|------------------|------|------------------|------|--------|------|------|

| A-2  | Cn               | B-9  | ŌĒŸ              | F-10 | Y3     | K-4  | C2   |

| A-3  | SIOO             | B-10 | YO               | F-11 | DB2    | K-5  | A0   |

| A-4  | <u> </u>         | B-11 | Y1               | G-1  | DA2    | K-6  | А3   |

| A-5  | 0107             | C-1  | 15               | G-2  | DAO    | K-7  | WE   |

| A-6  | C <sub>n+8</sub> | C-2  | V <sub>CC2</sub> | G-10 | DBO    | K-8  | DB7  |

| A-7  | G/N              | C-10 | Y4               | G-11 | DB3    | K-9  | OEB  |

| A-8  | P/OVR            | C-11 | Y6               | H-1  | DA3    | K-10 | EBO  |

| A-9  | ZERO             | D-1  | 16               | H-2  | DA1    | K-11 | EB1  |

| A-10 | PPP              | D-2  | V <sub>CC1</sub> | H-10 | DB6    | L-2  | CK   |

| B-1  | 12               | D-10 | Y5               | H-11 | DB4    | L-3  | C1   |

| B-2  | 13               | D-11 | Y7               | J-1  | DA4    | L-4  | C3   |

| B-3  | 11               | E-1  | 17               | J-2  | DA5    | L-5  | A1   |

| B-4  | 10               | E-2  | ŌEĀ              | J-10 | SELY . | L-6  | A2   |

| B-5  | 14               | E-10 | Y2               | J-11 | DB5    | L-7  | В3   |

| B-6  | SIO7             | E-11 | DB1              | K-1  | DA6    | L-8  | B2   |

| B-7  | SSF              | F-1  | ĒĀ               | K-2  | DA7    | L-9  | В1   |

| B-8  |                  | F-2  | GND              | K-3  | CO     | L-10 | В0   |

# PIN FUNCTIONAL DESCRIPTION

| PIN GRID   | CHIP     | NAME             | 1/0        | DESCRIPTION                                                                                                                                          |  |

|------------|----------|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ARRAY      | CARRIER  | NAME             | 1/0        | DESCRIPTION                                                                                                                                          |  |

| A-10       | 28       | PPP              | ı          | Package position pin. Tri-level input used to define package significance during                                                                     |  |

|            |          |                  |            | instruction execution. Leave open for intermediate positions, tie to VCC for most                                                                    |  |

|            |          |                  |            | significant package, and tie to GND for least significant package.                                                                                   |  |

| B-7        | 29       | SSF              | I/O        | Special shift function. Used to transfer required information between packages during                                                                |  |

|            |          |                  |            | special instruction execution.                                                                                                                       |  |

| A-9        | 30       | ZERO             | 1/0        | Device zero detection, open collector. Input during certain special instructions.                                                                    |  |

| A-8        | 31       | P/OVR            | 0          | ALU propagate/instruction overflow for most significant package, low active.  ALU generate/negative result for most significant package, low active. |  |

| A-7<br>A-6 | 32<br>33 |                  | 0          | ALU ripple carry output.                                                                                                                             |  |

|            |          | Cn + 8           |            | ALO rippie carry output.                                                                                                                             |  |

| B-6        | 34       | SIO7             | 1/0        |                                                                                                                                                      |  |

| A-5<br>A-4 | 35<br>36 | <u> </u>         | I/O<br>I/O | Bidirectional shift pin, low active.                                                                                                                 |  |

| A-4<br>A-3 | 37       | \$100            | 1/0        |                                                                                                                                                      |  |

| A-2        | 38       | Cn               | 1/0        | ALU carry input.                                                                                                                                     |  |

| B-4        | 39       | 10               | -          | ALO Carry Input.                                                                                                                                     |  |

| B-4<br>B-3 | 40       | 11               |            |                                                                                                                                                      |  |

| B-3<br>B-1 | 41       | 12               | i          |                                                                                                                                                      |  |

| B-1<br>B-2 | 42       | 13               | i          |                                                                                                                                                      |  |

| B-5        | 43       | 14               | i          | Instruction input.                                                                                                                                   |  |

| C-1        | 44       | 15               | i          |                                                                                                                                                      |  |

| D-1        | 45       | 16               |            |                                                                                                                                                      |  |

| E-1        | 46       | 17               | 1          |                                                                                                                                                      |  |

| C-2        | 47       | V <sub>CC2</sub> |            | Low voltage power supply (2 V).                                                                                                                      |  |

| D-2        | 48       | V <sub>CC1</sub> |            | I/O interface supply voltage (5 V).                                                                                                                  |  |

| E-2        | 49       | ŌĒĀ              | 1          | DA bus enable, low active.                                                                                                                           |  |

| F-1        | 50       | ĒĀ               |            | ALU input operand select. High state selects external DA bus and low state selects                                                                   |  |

|            |          |                  |            | register file.                                                                                                                                       |  |

| F-2        | 51       | GND              |            | Ground pin.                                                                                                                                          |  |

| G-2        | 52       | DA0              | 1/0        |                                                                                                                                                      |  |

| H-2        | 53       | DA1              | 1/0        |                                                                                                                                                      |  |

| G-1        | 54       | DA2              | 1/0        |                                                                                                                                                      |  |

| H-1        | 55       | DA3              | 1/0        | A port data bus. Outputs register file data ( $\overline{EA} = 0$ ) or inputs external data ( $\overline{EA} = 1$ ).                                 |  |

| J-1        | 56       | DA4              | 1/0        |                                                                                                                                                      |  |

| J-2        | 57       | DA5              | 1/0        |                                                                                                                                                      |  |

| K-1        | 58<br>59 | DA6<br>DA7       | 1/0        |                                                                                                                                                      |  |

| K-2        | 60       |                  |            | Charles all a parkyana un registare en positiva adas                                                                                                 |  |

| L-2<br>K-3 | 61       | CK<br>CO         | 1          | Clocks all synchronous registers on positive edge.                                                                                                   |  |

| L-3        | 62       | C1               |            |                                                                                                                                                      |  |

| K-4        | 63       | C2               | '          | Register file write address select.                                                                                                                  |  |

| L-4        | 64       | C3               |            |                                                                                                                                                      |  |

| K-5        | 65       | AO               | <b>—</b>   |                                                                                                                                                      |  |

| L-5        | 66       | A1               |            |                                                                                                                                                      |  |

| L-6        | 67       | A2               |            | Register file A port read address select.                                                                                                            |  |

| K-6        | 68       | А3               | 1          |                                                                                                                                                      |  |

# PIN FUNCTIONAL DESCRIPTION

| PIN GRID | CHIP | NAME | I/O   | DESCRIPTION                                                                                             |

|----------|------|------|-------|---------------------------------------------------------------------------------------------------------|

| K-7      | 1    | WE   | _     | Register file (RF) write enable. Data is written into RF when WE is low and a low-to-high               |

|          |      |      |       | clock transition occurs. RF write is inhibited when WE is high.                                         |

| L-7      | 2    | B3   | ı     |                                                                                                         |

| L-8      | 3    | B2   | - 1   | Register file B port read address select. (0 = LSB).                                                    |

| L-9      | 4    | B1   | 1     | negister file b port read address select. (0 = LSb).                                                    |

| L-10     | 5    | во   |       |                                                                                                         |

| K-10     | 6    | EBO  | - 1   | ALU input operand select. EBO and EB1 selects the source of data that the S multiplexer                 |

| K-11     | 7    | EB1  | 1     | provides for the S bus. Independent control of the DB bus and data path selection allow                 |

|          |      |      |       | the user to isolate the DB bus while the ALU continues to process data.                                 |

| K-9      | 8    | ŌĔB  | I     | DB bus enable, low active.                                                                              |

| K-8      | 9    | DB7  | 1/0   |                                                                                                         |

| H-10     | 10   | DB6  | 1/0   |                                                                                                         |

| J-11     | 11   | DB5  | 1/0   |                                                                                                         |

| H-11     | 12   | DB4  | I/O   | B port data bus. Outputs register data ( $\overline{OEB} = 0$ ) or used to input external data          |

| G-11     | 13   | DB3  | 1/0   | $(\overline{OEB} = 1)$ , $(0 = LSB)$ .                                                                  |

| F-11     | 14   | DB2  | 1/0   |                                                                                                         |

| E-11     | 15   | DB1  | 1/0   |                                                                                                         |

| G-10     | 16   | DBO  | 1/0   |                                                                                                         |

| J-10     | 17   | SELY | - 1   | Y bus select, high active.                                                                              |

| D-11     | 18   | Y7   | 1/0   |                                                                                                         |

| C-11     | 19   | Y6   | , I/O |                                                                                                         |

| D-10     | 20   | Y5   | 1/0   |                                                                                                         |

| C-10     | 21   | Y4   | I/O   | Y port data bus. Outputs instruction results ( $\overline{OEY} = 0$ ) or used to put external data into |

| F-10     | 22 ` | Y3   | I/O   | register file ( $\overline{OEY} = 1$ ).                                                                 |

| E-10     | 23   | Y2   | 1/0   |                                                                                                         |

| B-11     | 24   | Y1   | 1/0   |                                                                                                         |

| B-10     | 25   | YO   | 1/0   |                                                                                                         |

| B-9      | 26   | ŌĒŸ  | 1     | Y bus output enable, low active.                                                                        |

| F-2      | 27   | GND  |       | Ground pin                                                                                              |

# architectural elements

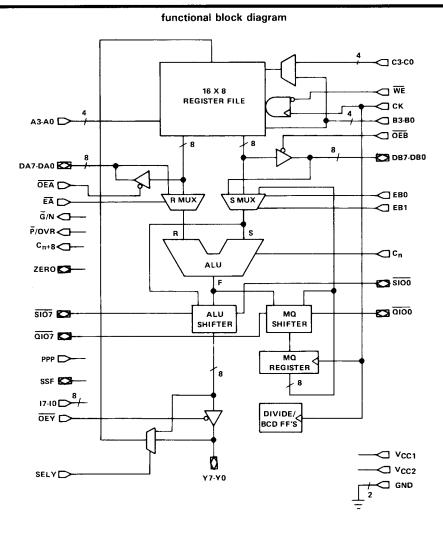

#### 3-port register file

Working registers consist of 128 storage elements organized into sixteen 8-bit words. These storage elements appear to the user as 16 positive edge-triggered registers. The three port addresses, one write (C) and two reads (A and B), are completely independent of each other to implement a 3-operand register file. Data is written into the register file when  $\overline{\rm WE}$  is low and a low-to-high clock transition occurs. The ADD and SUBTRACT immediate instructions require only one source operand. The B address is used as the source address, and the bits of the A address are used to provide a constant field. The SET, RESET, and TEST BIT instructions use the B addressed register as both the source and destination register while the A and C addresses are used as masks. These instructions are explained in more detail in the instruction section.

#### S multiplexer

The S multiplexer selects the ALU operand, as follows:

| EB1  | EB0  | S bus   |

|------|------|---------|

| Low  | Low  | RF data |

| Low  | High | MQ data |

| High | Low  | DB data |

| High | Hiah | MQ data |

# DB port

Data is passed through the ALU or received from the register file on the 8-bit DB port. If  $\overline{OEB}$  is low, the DB bus is active; if  $\overline{OEB}$  is high, the DB bus is in the high impedance state. Notice that the DB port may be isolated at the same time that register file data is passed to the ALU.

#### R multiplexer

The R multiplexer selects the other operand of the ALU. Except for those instructions that require constants or masks, the R bus will contain DA if  $\overline{EA}$  is high or the RF data pointed to by A if  $\overline{EA}$  is low.

#### DA bus

The DA bus is active (with register file data) if  $\overline{OEA}$  is low. Notice that the DA bus may be isolated while register file data is passed to the ALU.

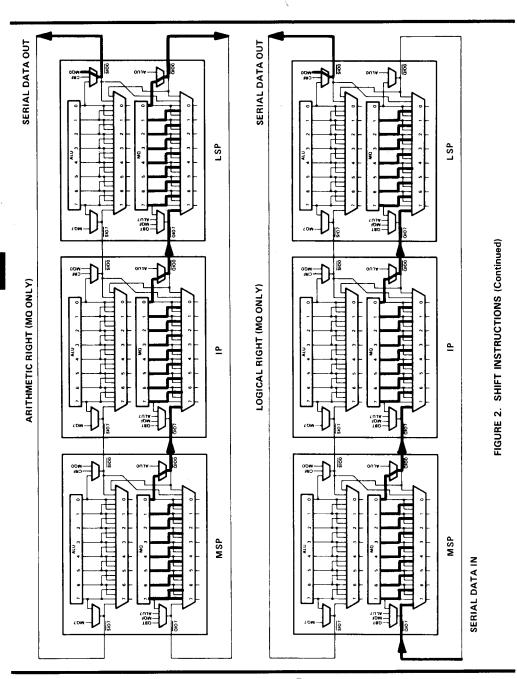

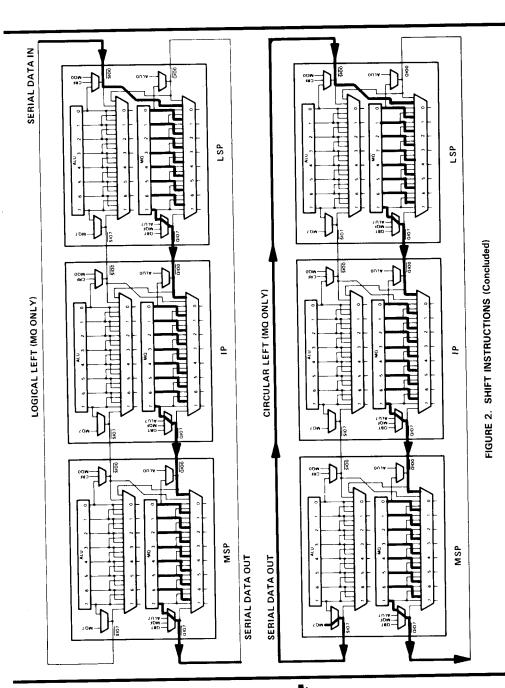

# ALU

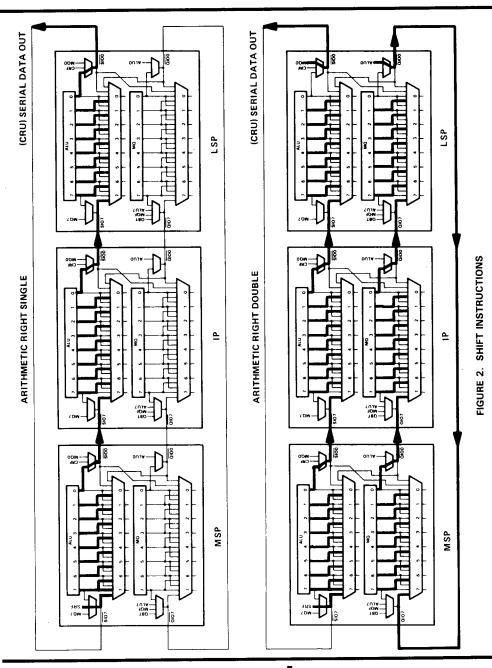

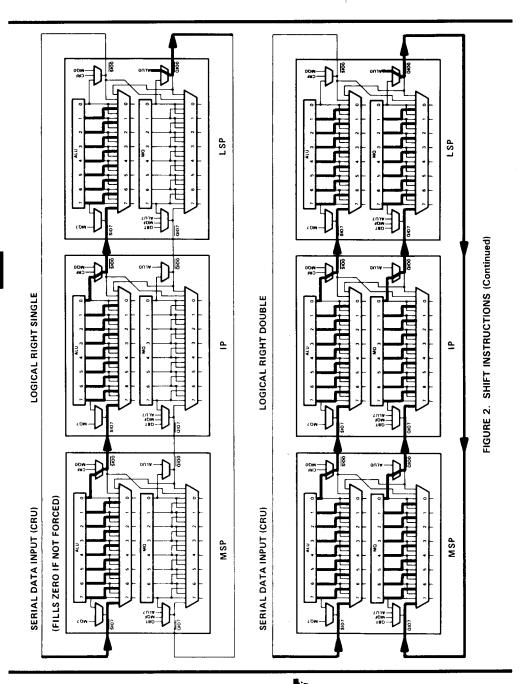

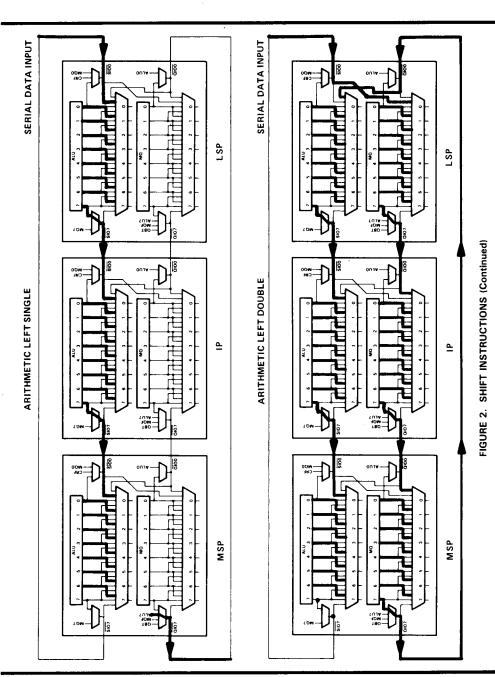

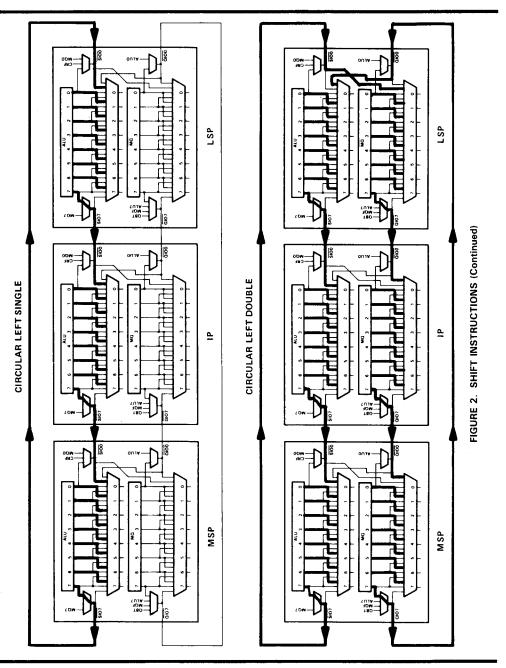

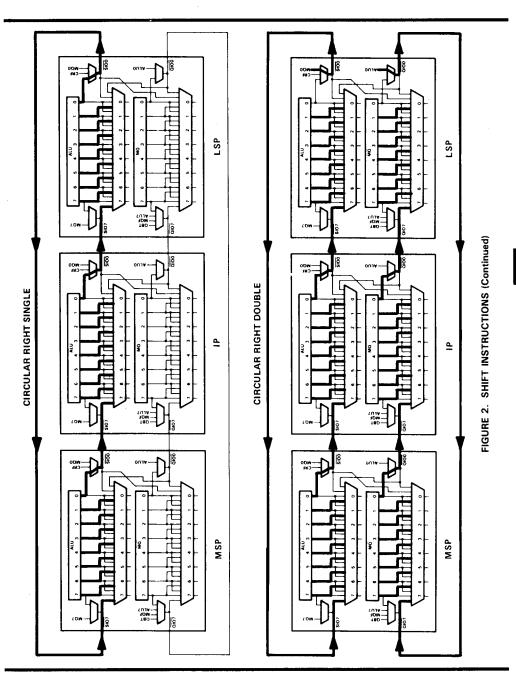

The shift instructions are summarized in Table 4 and illustrated in Figure 2. The ALU can perform seven arithmetic and six logical instructions on two 8-bit operands. It also supports multiplication, division, normalization, bit set, reset, test, byte operations, and excess-3 BCD arithmetic. These source operands are the outputs of the S and R multiplexers.

## ALU and MQ shifters

ALU and MQ shifters perform all of the shift, multiply, divide, and normalize functions. Table 4 shows the value of the  $\overline{SIO7}$  and  $\overline{QIO7}$  pins of the most significant package. The standard shifts may be made into conditional shifts and the serial data may be input or output with the aid of two three-state gates. These capabilities are discussed further in the arithmetic and logic section.

# MQ register

The multiplier-quotient (MQ) register has specific functions in multiplication, division, and normalization. This register may also be used as a temporary storage register. The MQ register may be loaded if the instruction code on pins I7-I0 is E1-E7 or E9-EE (See Table 1).

#### Y bus

The Y bus contains the output of the ALU shifter if  $\overline{OEY}$  is low and is a high impedance input if  $\overline{OEY}$  is high. SELY must be low to pass the internal ALU shift bus and must be high to pass the external Y bus to the register file.

#### status

Four status pins are available on the most significant package, overflow (OVR), sign (N), carry out ( $C_{n+8}$ ), and zero (ZERO). The  $C_{n+8}$  line signifies the ALU result while OVR, ZERO, and N refer the status after the ALU shift has occurred. Notice that the ZERO pin cannot be used to detect whether an input placed on a high impedance Y bus is zero.

#### divide BCD flip-flops

The multiply-divide flip-flops contain the status of the previous multiply or divide instruction. They are affected by the following instructions:

DIVIDE REMAINDER FIX

SIGNED DIVIDE QUOTIENT FIX

SIGNED MULTIPLY

SIGNED MULTIPLY TERMINATE

SIGNED DIVIDE INITIALIZE

SIGNED DIVIDE START

SIGNED DIVIDE ITERATE

UNSIGNED DIVIDE START

UNSIGNED DIVIDE ITERATE

UNSIGNED MULTIPLY

SIGNED DIVIDE TERMINATE

UNSIGNED DIVIDE TERMINATE

The excess-3 BCD flip-flops are affected by all instructions except NOP. The clear function clears these flip-flops. They preserve the carry from each nibble (4-bits) in excess-3/BCD operations.

# package position pin (PPP)

The position of the processor in the system is defined by the voltage level applied to the package position pin (PPP). Intermediate positions are selected by leaving the pin open. Tying the pin to VCC makes the processor the most significant package and tying the pin to GND makes the processor the least significant package.

#### special shift function (SSF) pin

Conditional shifting algorithms may be implemented via control of the SSF pin. The applied voltage to this pin may be set as a function of a potential overflow condition (the two most significant bits are not equal) or any other condition (see Group 1 instructions).

# instruction set

The 'AS888 bit-slice processor uses bits 17-I0 as instruction inputs. A combination of bits I3-I0 (Group 1 instructions) and bits I7-I4 (Group 2-5 instructions) are used to develop the 8-bit op code for a specific instruction. Group 1 and Group 2 instructions can be combined to perform arithmetic or logical functions plus a shift function in one instruction cycle. A summary of the instruction set is given in Table 1.

# TABLE 1. INSTRUCTION SET

# **GROUP 1 INSTRUCTIONS**

| GROUP 1 INSTRUCTIONS                       |                                       |                                    |  |  |

|--------------------------------------------|---------------------------------------|------------------------------------|--|--|

| INSTRUCTION BITS (13-10)                   | MNEMONIC                              | FUNCTION                           |  |  |

| HEX CODE                                   | initziiioiii                          |                                    |  |  |

| 0                                          |                                       | Accesses Group 4 instructions      |  |  |

| 1                                          | ADD                                   | $R + S + C_n$                      |  |  |

| 2                                          | SUBR                                  | $\overline{R} + S + C_n$           |  |  |

| 3                                          | SUBS                                  | $R + \overline{S} + C_n$           |  |  |

| 4                                          | INCS                                  | S+C <sub>n</sub>                   |  |  |

| 5                                          | INCNS                                 | \$ + C <sub>n</sub>                |  |  |

| 6                                          | INCR                                  | R+C <sub>n</sub>                   |  |  |

| 7                                          | INCNR                                 | R+C <sub>n</sub>                   |  |  |

| 8                                          |                                       | Accesses Group 3 instructions      |  |  |

| 9                                          | XOR                                   | R XOR S                            |  |  |

| Α                                          | AND                                   | R AND S                            |  |  |

| В                                          | OR                                    | R OR S                             |  |  |

| С                                          | NAND                                  | R NAND S                           |  |  |

| D                                          | NOR                                   | R NOR S                            |  |  |

| E                                          | ANDNR                                 | R AND S                            |  |  |

| F _                                        |                                       | Accesses Group 5 instructions      |  |  |

|                                            | GROUP 2 INST                          | RUCTIONS                           |  |  |

| INSTRUCTION BITS (17-14) MNEMONIC FUNCTION |                                       |                                    |  |  |

| HEX CODE                                   | MITELLIONIO                           |                                    |  |  |

| 0                                          | SRA                                   | Arithmetic Right Single            |  |  |

| 1 "                                        | SRAD                                  | Arithmetic Right Double            |  |  |

| 2                                          | SRL                                   | Logical Right Single               |  |  |

| 3                                          | SRLD                                  | Logical Right Double               |  |  |

| 4                                          | SLA                                   | Arithmetic Left Single             |  |  |

| 5                                          | SLAD                                  | Arithmetic Left Double             |  |  |

| 6                                          | SLC                                   | Circular Left Single               |  |  |

| • 7                                        | SLCD                                  | Circular Left Double               |  |  |

| 8                                          | SRC                                   | Circular Right Single              |  |  |

| 9                                          | SRCD                                  | Circular Right Double              |  |  |

| A                                          | MQSRA                                 | Pass (F→Y) and Arithmetic Right MQ |  |  |

| В                                          | MOSRL                                 | Pass (F→Y) and Logical Right MQ    |  |  |

| С                                          | MQSLL                                 | Pass (F→Y) and Logical Left MQ     |  |  |

| D                                          | MQSLC Pass (F→Y) and Circular Left MQ |                                    |  |  |

| 1 -                                        | 1                                     | D (E -V) 1     MO (E - MO)         |  |  |

| E                                          | LOADMQ                                | Pass (F→Y) and Load MQ (F = MQ)    |  |  |

# **TABLE 1. INSTRUCTION SET (Continued)**

#### **GROUP 3 INSTRUCTIONS**

| INSTRUCTION BITS (17-10) | MNEMONIC  | FUNCTION                        |  |

|--------------------------|-----------|---------------------------------|--|

| HEX CODE                 | MINEMONIC | PONCTION                        |  |

| 08                       | SET1      | Set Bit                         |  |

| 18                       | SET0      | Reset Bit                       |  |

| 28                       | TB1       | Test Bit (One)                  |  |

| 38                       | TBO       | Test Bit (Zero)                 |  |

| 48                       | ABS       | Absolute Value                  |  |

| 58                       | SMTC      | Sign Magnitude/Two's Complement |  |

| 68                       | ADDI      | Add Immediate                   |  |

| 78                       | SUBI      | Subtract Immediate              |  |

| 88                       | BADD      | Byte Add R to S                 |  |

| 98                       | BSUBS     | Byte Subtract S from R          |  |

| A8                       | BSUBR     | Byte Subtract R from S          |  |

| B8                       | BINCS     | Byte Increment S                |  |

| C8                       | BINCNS    | Byte Increment Negative S       |  |

| D8                       | BXOR      | Byte XOR R and S                |  |

| E8                       | BAND      | Byte AND R and S                |  |

| F8                       | BOR       | Byte OR R and S                 |  |

| CDOLID | 1 | INSTRUCTIONS |  |

|--------|---|--------------|--|

| INSTRUCTION BITS (17-10) HEX CODE | MNEMONIC | FUNCTION                   |

|-----------------------------------|----------|----------------------------|

| 00                                |          | Reserved                   |

| 10                                | SEL      | Select S/R                 |

| 20                                | SNORM    | Single Length Normalize    |

| 30                                | DNORM    | Double Length Normalize    |

| 40                                | DIVRF    | Divide Remainder Fix       |

| 50                                | SDIVQF   | Signed Divide Quotient Fix |

| 60                                | ŞMULI    | Signed Multiply Iterate    |

| 70                                | SMULT    | Signed Multiply Terminate  |

| 80                                | SDIVIN   | Signed Divide Initialize   |

| 90                                | SDIVIS   | Signed Divide Start        |

| AO                                | SDIVI    | Signed Divide Iterate      |

| во                                | UDIVIS   | Unsigned Divide Start      |

| СО                                | UDIVI    | Unsigned Divide Iterate    |

| DO                                | UMULI    | Unsigned Multiply Iterate  |

| EO                                | SDIVIT   | Signed Divide Terminate    |

| FO                                | UDIVIT   | Unsigned Divide Terminate  |

# TABLE 1. INSTRUCTION SET (Concluded)

# **GROUP 5 INSTRUCTIONS**

| INSTRUCTION BITS (17-10) HEX CODE | MNEMONIC | FUNCTION                     |  |

|-----------------------------------|----------|------------------------------|--|

|                                   | CL D     | Class                        |  |

| OF                                | CLR      | Clear                        |  |

| 1F                                | CLR      | Clear                        |  |

| 2F                                | CLR      | Clear                        |  |

| 3F                                | CLR      | Clear                        |  |

| 4F                                | CLR      | Clear                        |  |

| 5F                                | CLR      | Clear                        |  |

| 6F                                | CLR      | Clear                        |  |

| 7F                                | BCDBIN   | BCD to Binary                |  |

| 8F                                | EX3BC    | Excess-3 Byte Correction     |  |

| 9F                                | EX3C     | Excess-3 Word Correction     |  |

| AF                                | SDIVO    | Signed Divide Overflow Check |  |

| BF                                | CLR      | Clear                        |  |

| CF                                | CLR      | Clear                        |  |

| DF                                | BINEX3   | Binary to Excess-3           |  |

| EF                                | CLR      | Clear                        |  |

| FF                                | NOP      | No Operation                 |  |

# group 1 instructions

TABLE 2. GROUP 1 INSTRUCTIONS

| INSTRUCTION BITS (13-10) | MNEMONIC | FUNCTION                      |

|--------------------------|----------|-------------------------------|

| HEX CODE                 |          |                               |

| 0                        |          | Accesses Group 4 instructions |

| 1                        | ADD      | R+S+C <sub>n</sub>            |

| 2                        | SUBR     | R+S+C <sub>n</sub>            |

| 3                        | SUBS     | R+\$+C <sub>n</sub>           |

| 4                        | INCS     | S+C <sub>n</sub>              |

| 5                        | INCNS    | \$+Cn                         |

| 6                        | INCR     | R+C <sub>n</sub>              |

| 7                        | INCNR    | R + C <sub>n</sub>            |

| . 8                      |          | Accesses Group 3 instructions |

| 9                        | XOR      | R XOR S                       |

| A                        | AND      | RANDS                         |

| В                        | OR       | RORS                          |

| С                        | NAND     | RNANDS                        |

| D                        | NOR      | RNORS                         |

| E                        | ANDNR    | R AND S                       |

| F                        | <u> </u> | Accesses Group 5 instructions |

Group 1 instructions (excluding hex codes 0, 8, and F), shown in Table 2, may be used in conjunction with Group 2 shift instructions to perform arithmetic or logical functions plus a shift function<sup>†</sup> in one instruction cycle (hex codes 0, 8, and F are used to access Group 4, 3, and 5 instructions, respectively). Each shift may be made into a conditional shift by forcing the special shift function (SSF) pin into the proper state. If the SSF pin is high or floating, the shifted ALU output will be sent to the output buffers. If the SSF pin is pulled low externally, the ALU result will be passed directly to the output buffers. Conditional shifting is useful for scaling inputs in data arrays or in signal processing algorithms.

These instructions set the BCD flip-flop for the excess-3 correct instruction. The status is set with the following results ( $C_{n+8}$  is ALU carry out and is independent of shift operation; others are evaluated after shift operation).

#### condition code

#### Arithmetic

N — MSB of result

OVR - Signed arithmetic overflow

Cn+8 - Carry out equal one

Z - Result equal zero

# Logic

N - MSB of result

OVR - None (force to zero)

$C_{n+8}$  — None (force to zero)

Z - Result equal zero

# group 2 instructions

TABLE 3. GROUP 2 INSTRUCTIONS

| INSTRUCTION BITS (17-14) HEX CODE | MNEMONIC | FUNCTION                           |

|-----------------------------------|----------|------------------------------------|

| 0                                 | SRA      | Arithmetic Right Single            |

| 1                                 | SRAD     | Arithmetic Right Double            |

| 2                                 | SRL      | Logical Right Single               |

| 3                                 | SRLD     | Logical Right Double               |

| 4                                 | SLA      | Arithmetic Left Single             |

| 5                                 | SLAD     | Arithmetic Left Double             |

| 6                                 | SLC      | Circular Left Single               |

| 7                                 | SLCD     | Circular Left Double               |

| 8                                 | SRC      | Circular Right Single              |

| 9                                 | SRCD     | Circular Right Double              |

| Α                                 | MQSRA    | Pass (F→Y) and Arithmetic Right MQ |

| В                                 | MQSRL    | Pass (F→Y) and Logical Right MQ    |

| С                                 | MQSLL    | Pass (F→Y) and Logical Left MQ     |

| D                                 | MQSLC    | Pass (F→Y) and Circular Left MQ    |

| E                                 | LOADMQ   | Pass (F→Y) and Load MQ (F = MQ)    |

| F.                                | PASS     | Pass (F→Y)                         |

<sup>†</sup>Double-precision shifts involve both the ALU and MQ register.

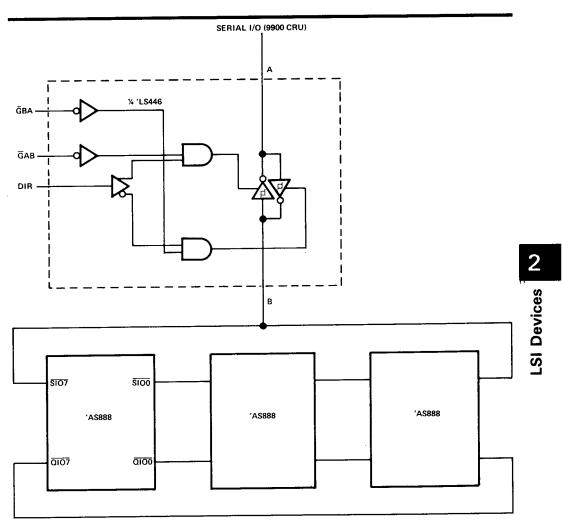

The processor's shift instructions are implemented by a combination of Group 2 instructions (Table 3) and certain wired connections on the packages used. The following external connections are required.

On intermediate packages:

SIO7 is connected to SIOO of the next most significant package

QIO7 is connected to QIOO of the next most significant package

SIOO is connected to SIO7 of the next least significant package

QIOO is connected to QIO7 of the next least significant package

On the two end packages:

\$\overline{SIO7}\$ on the most significant package is connected to \$\overline{SIO0}\$ of the least significant package QIO7 on the most significant package is connected to QIO0 of the least significant package

The connections are the same on all instructions including multiply, divide, CRC, and normalization functions.

Single- and double-precision shifts are supported. Double-precision shifts assume the most significant half has come through the ALU and will be placed (if WE is low) into the register file on the rising edge of the clock and the least significant half lies in the MQ register. All Group 2 shifts may be made conditional (see previous page).

The following definitions apply to Group 2 shift instructions:

Arithmetic right shifts copy the sign of the number if no overflow occurs from the ALU calculation; if overflow occurs, the sign bit is inverted.

Arithmetic left shifts do not retain the sign of the number if an overflow occurs. A zero is filled into the LSB if not forced externally.

Logical right shifts fill a zero in the MSB position if not forced externally.

Circular right shifts fill the LSB in the MSB position.

Circular left shifts fill the MSB in the LSB position.

Shifting left is defined as moving a bit position towards the MSB (doubling).

Shifting right is defined as moving a bit towards the LSB (halving).

Serial input may be performed using the circuitry shown in Figure 1. A single-/or double-precision arithmetic left or logical right shift fills the complement of the data on SIOO and SIO7 into the LSB or MSB of the data word(s). Note that if \$100 and \$107 are floating (HI-Z), a zero will be filled as an end condition.

Serial output may be performed with circular instructions.

FIGURE 1. SERIAL I/O

The shift instructions are summarized in Table 4 and illustrated in Figure 2. In Figure 2 and all succeeding figures that illustrate instruction execution, the following definitions apply:

CRF - CRC accumulator end fill.

QBT ---End fill for signed divide.

MQF - End fill for unsigned divide.

SRF - End fill for signed multiply and the arithmetic right shifts.

**TABLE 4. SHIFT INSTRUCTIONS**

| OP<br>CODE <sup>†</sup> | SHIFT FUNCTION <sup>‡</sup> | SIO7 - SIO0<br>WIRED VALUE | QIO7 • QIO0<br>WIRED VALUE |

|-------------------------|-----------------------------|----------------------------|----------------------------|

| ON                      | Arithmetic Right Single     | ALU-LSB Output             |                            |

| 1 N                     | Arithmetic Right Double     | MQ-LSB Output              | ALU-LSB Qutput             |

| 2N                      | Logical Right Single        | Input to ALU-MSB           | ALU-LSB Output             |

| 3N                      | Logical Right Double        | Input to ALU-MSB           | ALU-LSB Output             |

| 4N                      | Arithmetic Left Single      | Input to ALU-LSB           | ALU-MSB Output             |

| 5N                      | Arithmetic Left Double      | Input to MQ-LSB            | MQ-MSB Output              |

| 6N                      | Circular Left Single        | ALU-MSB Output             | -                          |

| 7N                      | Circular Left Double        | ALU-MSB Output             | MQ-MSB Output              |

| 8N                      | Circular Right Single       | ALU-LSB Output             |                            |

| 9N                      | Circular Right Double       | MQ-LSB Output              | ALU-LSB Output             |

| AN                      | Arithmetic Right (MQ only)  | MQ-LSB Output              | MQ-LSB Output              |

| BN                      | Logical Right (MQ only)     | MQ-LSB Output              | Input to MQ-MSB            |

| CN                      | Logical Left (MQ only)      | Input to MQ-LSB            | MQ-MSB Output              |

| DN                      | Circular Left (MQ only)     | MQ-MSB Output              | MQ-MSB Output              |

<sup>&</sup>lt;sup>†</sup>Op Code N ≠ 0, 8, or F; these select special instruction Groups 4, 3, and 5 respectively. <sup>‡</sup>Shift I/O pins are active low. Therefore, inputs and outputs must be inverted if true

# Status is set with the following results:

# Arithmetic

Ν Result MSB equal one

OVR Signed arithmetic overflow<sup>†</sup>

$C_{n+8}$ Carry out equal one

Z Result equal zero

# Logic

Ν Result MSB equal one

OVR Zero Zero

Result equal zero

logical values are required.

<sup>†</sup> For the SLA and SLAD instructions, OVR is set if signed arithmetic overflow or if the ALU result MSB XOR MSB-1 equals one.

# LSI Device

# group 3 instructions

Hex code 8 of Group 1 instructions is used to access Group 3 instructions. Group 3 instructions are summarized in Table 5.

**TABLE 5. GROUP 3 INSTRUCTIONS**

| INSTRUCTION BITS (17-10) OP CODE (HEX) | MNEMONIC | FUNCTION                        |

|----------------------------------------|----------|---------------------------------|

| 08                                     | SET1     | Set Bit                         |

| 18                                     | SETO     | Reset Bit                       |

| 28                                     | TB1      | Test Bit (One)                  |

| 38                                     | ТВО      | Test Bit (Zero)                 |

| 48                                     | ABS      | Absolute Value                  |

| 58                                     | SMTC     | Sign Magnitude/Two's Complement |

| 68                                     | ADDI     | Add Immediate                   |

| 78                                     | SUBI     | Subtract Immediate              |

| 88                                     | BADD     | Byte Add R to S                 |

| 98                                     | BSUBS    | Byte Subtract S from R          |

| A8                                     | BSUBR    | Byte Subtract R from S          |

| B8                                     | BINCS    | Byte Increment S                |

| C8                                     | BINCNS   | Byte Increment Negative S       |

| D8                                     | BXOR     | Byte XOR R and S                |

| E8                                     | BAND     | Byte AND R and S                |

| F8                                     | BOR      | Byte OR R and S                 |

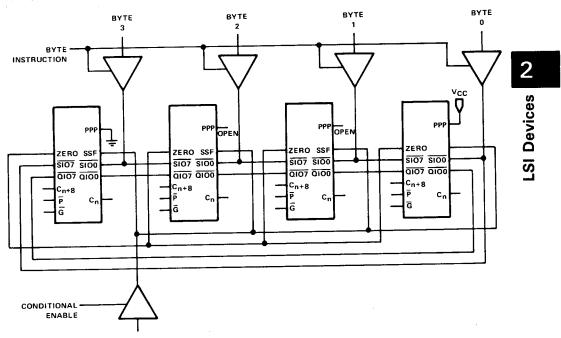

# set bit instruction (set1): 17-10 = 0816

This instruction (Figure 3) is used to force selected bits of a desired byte(s) to one (any combination of zero to eight bits). The desired bits are specified by an 8-bit mask (C3-C0)::(A3-A0) $^{\dagger}$  consisting of register file address ports that are not required to support this instruction. All bits in the selected byte(s) that are in the same bit positions as ones in the mask are forced to a logical one. The B3-B0 address field is used for both source and destination of this instruction. The desired byte is specified by forcing  $\overline{S100}$  to a low value. Nonselected packages pass the byte through unaltered. The S bus is the source word for this instruction. The status set by the set bit instruction is as follows:

$egin{array}{lll} N & &

ightarrow & None (force to zero) \\ OVR &

ightarrow & None (force to zero) \\ C_{n+8} &

ightarrow & None (force to zero) \\ Z &

ightarrow & Result equal zero \\ \end{array}$

† The symbol '::' is concatenation operator

FIGURE 3. SET BIT (OR RESET BIT)

NOTES: 1. Force \$100 low to select byte.

2. Bit mask (C3-C0)::(A3-A0) will set desired bits to one.

# reset bit instruction (set0): 17-10 = 1816

This instruction (Figure 3) is used to force selected bits of a desired byte(s) to zero (any combination of one to eight bits). The desired bits are specified by an 8-bit mask (C3-C0)::(A3-A0) consisting of register file address ports that are not required to support this instruction. All bits in the selected byte(s) that are in the same bit positions as ones in the mask are reset. The B3-B0 address field is used for both source

and destination of this instruction. The desired byte is specified by forcing SIOO to a low value. Nonselected packages pass the byte through unaltered. The S bus is the source word for this instruction. The status set by the reset bit instruction is as follows:

None (force to zero) OVR None (force to zero)  $C_{n+8}$ None (force to zero) Result equal zero

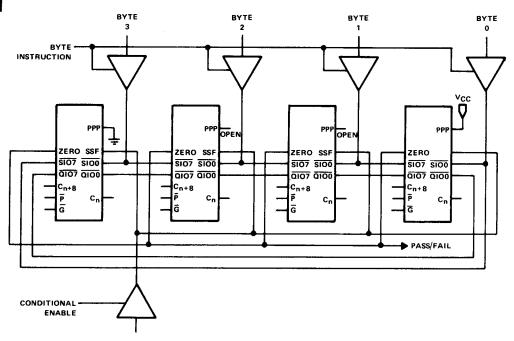

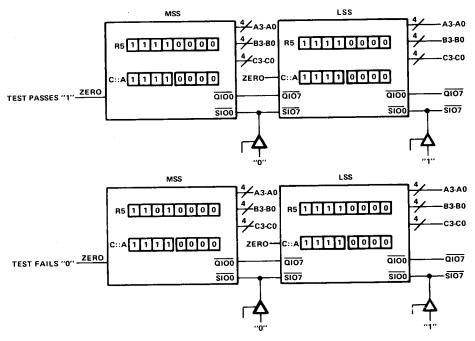

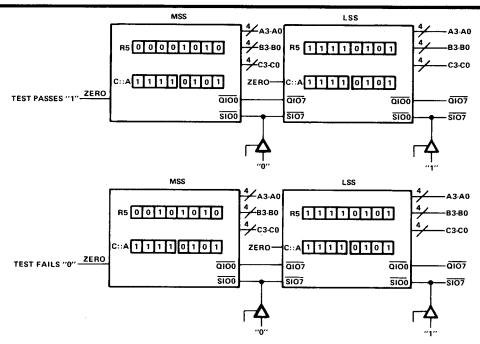

## test bit (one) instruction (TB1): 17-10 = 2816

This instruction (Figure 4) is used to test selected bits of a desired byte(s)(any combination of one to eight bits). Bits to be tested are specified by an 8-bit mask (C3-C0)::(A3-A0) consisting of register file address ports that are not required to support this instruction. Write Enable ( $\overline{WE}$ ) is internally disabled during this instruction. The desired byte is specified by forcing SIOO to a low value. The test will pass if the selected byte has ones at all bit locations specified by the ones of the mask (Figure 5). The S bus is the source word for this instruction. The status set by the test bit (one) instruction is as follows:

Ν None (force to zero) OVR None (force to zero) None (force to zero) **Pass**

FIGURE 4. TEST BIT

NOTES: 1. Force SIOO low to select byte.

2. Bit mask (C3-C0)::(A3-A0) will define bits for testing.

3. Pass/fail is indicated on Z output.

# test bit (zero) instruction (TB0): 17-10 = 3816

This instruction (Figure 4) is used to test selected bits of a desired byte(s) (any combination of one to eight bits). Bits to be tested are specified by an 8-bit mask (C3-C0)::(A3-A0) consisting of register file address ports that are not required to support this instruction. Write Enable (WE) is internally disabled during this instruction. The desired byte is specified by forcing \$100 to a low value. The test will pass if the selected byte has zeros at all bit locations specified by the ones of the mask (Figure 6). The S bus is the source word for this instruction. The status set by the test bit (zero) instruction is as follows:

N None (force to zero) None (force to zero) **OVR** None (force to zero) **Pass**

FIGURE 5. TEST BIT ONE EXAMPLES

FIGURE 6. TEST BIT ZERO EXAMPLES

#### absolute value instruction (ABS): 17-10 = 4816

This instruction is used to convert two's complement numbers to their positive value. The operand placed on the S bus is the source for this instruction. The MSP will test the sign of the S bus and force the SSF pin to the proper value. All other packages use the SSF pin as input to determine instruction execution. The status set by the absolute value instruction is as follows:

# sign magnitude/two's complement instruction (SMTC): 17-10 = 5816

This instruction allows conversion from two's complement representation to sign magnitude representation, or vice-versa, in one clock cycle. The operand placed on the S bus is the source for this instruction.

When a negative zero (8000 hex) is converted, the result is 0000 with an overflow. If the input is in two's complement notation, the overflow indicates an illegal conversion. The status set by the sign magnitude/two's complement instruction is as follows:

$egin{array}{lll} N &

ightharpoonup &$

# add immediate instruction (ADDI): 17-10 = 6816

This instruction is used to add a specified constant value to the operand placed on the S bus. The constant will be between the values of 0 and 15. The constant value is specified by the unused register file address (A port) not required to support this instruction. Forcing the carry input will add an additional one to the result. The status set by the add immediate instruction is as follows:

# subtract immediate instruction (SUBI): 17-10 = 7816

This instruction is used to subtract a specified constant value from the operand placed on the S bus. The constant value is specified by the unused register file address (A port) that is not required to support this instruction. The constant applied is the least significant four bits of a two's complement number. The device sign extends the constant over the entire word length. The status set by the subtract immediate instruction is as follows:

$N \rightarrow Result MSB equal one OVR \rightarrow Arithmetic signed overflow <math>C_{n+8} \rightarrow Carry out equal one Z \rightarrow Result equal zero$

#### byte instructions

There are eight byte instructions in Group 3. These instructions modify selected bytes of the operand on the S bus. A byte is selected by forcing  $\overline{SIOO}$  to a low value (same as SET1, SET0, TB1, and TB0 instructions). Multiple bytes may be selected only if they are adjacent to one another.

NOTE: At least one byte must be nonselected during these instructions.

The nonselected bytes are passed through unaltered. Byte status is forced through the most significant package except for the sign of the result (N), which is forced to zero (low). The status set by the byte instructions is as follows:

# (Most Significant Package)

$\begin{array}{cccc} N & \rightarrow & \text{None (force to zero)} \\ \text{OVR} & \rightarrow & \text{Byte signed overflow} \\ \text{$C_{n+8}$} & \rightarrow & \text{Byte carry out equal one} \\ \text{$z$} & \rightarrow & \text{Byte result equal to zero} \end{array}$

# (Selected BYTES—other than MSP)

$\overline{G}$   $\rightarrow$  Normal generate  $\overline{P}$   $\rightarrow$  Normal propagate  $C_{n+8}$   $\rightarrow$  Normal carry out Z  $\rightarrow$  Result equal to zero

#### (Nonselected BYTES-other than MSP)

$\overline{G}$   $\rightarrow$  No generate (force to one)  $\overline{P}$   $\rightarrow$  Propagate (force to zero)  $C_{n+8}$   $\rightarrow$   $C_{n}$

Cn + 8 ' Cn '

#### group 4 instructions

Hex code 0 of Group 1 instructions is used to access Group 4 instructions. Group 4 instructions are summarized in Table 6.

**TABLE 6. GROUP 4 INSTRUCTIONS**

| INSTRUCTION BITS (17-10) OP CODE (HEX) | MNEMONIC | FUNCTION                   |

|----------------------------------------|----------|----------------------------|

| 00                                     |          | Reserved                   |

| 10                                     | SEL      | Select S/R                 |

| 20                                     | SNORM    | Single Length Normalize    |

| 30                                     | DNORM    | Double Length Normalize    |

| 40                                     | DIVRF    | Divide Remainder Fix       |

| 50                                     | SDIVQF   | Signed Divide Quotient Fix |

| 60                                     | SMULI    | Signed Multiply Iterate    |

| 70                                     | SMULT    | Signed Multiply Terminate  |

| 80                                     | SDIVIN   | Signed Divide Initialize   |

| 90                                     | SDIVIS   | Signed Divide Start        |

| AO                                     | SDIVI    | Signed Divide Iterate      |

| во                                     | UDIVIS   | Unsigned Divide Start      |

| СО                                     | UDIVI    | Unsigned Divide Iterate    |

| DO                                     | UMULI    | Unsigned Multiply Iterate  |

| EO                                     | SDIVIT   | Signed Divide Terminate    |

| F0                                     | UDIVIT   | Unsigned Divide Terminate  |

## select S/R instruction (SEL): 17-10 = 1016

This instruction is used to pass either the S bus or the R bus to the output depending on the state of the SSF input pin. Normally, the preceding instruction would test the two operands and the resulting status information would be used to force the SSF input pin. SSF = 0 will output the R bus and SSF = 1 will output the S bus. The status set by the select S/R instruction is as follows:

Result MSB equal one OVR None (force to zero) None (force to zero) Result equal zero

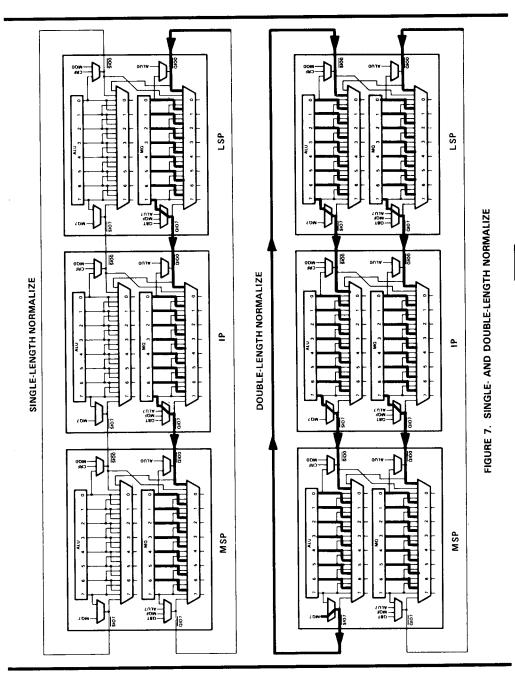

#### single-length normalize instruction (SNORM): 17-10 = 20<sub>16</sub>

This instruction will cause the contents of the MQ register to shift toward the most significant bit. Zeros are shifted in via the QIOO input. The number of shifts performed can be counted and stored in one of the register files by forcing a high at the Cn input. When the two most significant bits are of opposite value, normalization is complete. This condition is indicated on the microcycle that completes the normalization at the OVR output.

The chip contains conditional logic that inhibits the shift function (and also inhibits the register file increment) if the number within the MQ register is already normalized at the beginning of the instruction (Figure 7). The status set by the single-length normalize instruction is as follows:

Ν MSB of result OVR MSB XOR 2nd MSB Carry out equal one Result equal zero

# double-length normalize instruction (DNORM): 17-10 = 3016

This instruction will cause the contents of a double-length word (register file contains the most significant half and the MQ register contains the least significant half) to shift toward the most significant bit. Zeros are shifted in via the  $\overline{\text{QIOO}}$  input. When the two most significant bits are of opposite value, normalization is complete. This condition is indicated on the microcycle that completes the normalization at the OVR output.

The chip contains conditional logic which inhibits the shift function if the number is already normalized at the beginning of the instruction (Figure 7). The most significant half of the operand must be placed on the S bus. The status set by the double-length normalize instruction is as follows:

$\begin{array}{ccc} N & \rightarrow & \text{MSB of result} \\ \text{OVR} & \rightarrow & \text{MSB XOR 2nd MSB} \\ \text{C}_{n+8} & \rightarrow & \text{None (force to zero)} \\ \text{Z} & \rightarrow & \text{Result equal zero} \end{array}$

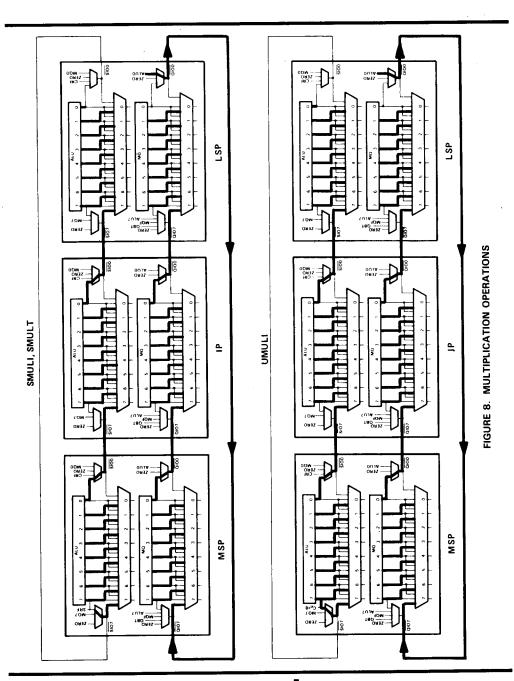

# multiply operations

The ALU performs three unique types of N by N multiplies each of which produces a 2N-bit result (Figure 8). All three types of multiplication proceed via the following recursion:

$P(J+1) = 2[P(J) + Multiplicand \times M (8N-J)]$  where P(J) = partial product at iteration number J N = number of 'AS888 packages that are cascaded P(J+1) = partial product at iteration number J+1  $J \text{ varies from 0 to } 8N \text{ } [N=2 \text{ for } 16 \times 16 \text{ multiply}]$  M (8N-J) = mode bit (unique to multiply type) 2 denotes some type of shift (unique to multiply)

Notice that by proper choice of mode terms and shifting operations, signed, unsigned, and mixed multiplies (signed times unsigned) may be performed.

All multiplies assume that the multiplier is stored in MQ before the operation begins (in the case of mixed multiply, the unsigned number must be the multiplier).

The processor has the following multiply instructions:

- SIGNED MULTIPLY ITERATE (SMULI): 17-I0 = 6016

SIGNED MULTIPLY TERMINATE (SMULT): 17-I0 = 7016

- 3. UNSIGNED MULTIPLY ITERATE (UMULI): 17-10 = D016

The signed multiply iterate (SMULI) instruction performs a signed times signed iteration. This instruction interprets M(8N-J) as the 8N-J bit of the multiplier. The shift is a double-precision right shift one bit. This instruction is repeated 15 times for a 16 × 16 signed multiply. This instruction will be used 16 consecutive times for a mixed multiplication.

The signed multiply terminate (SMULT) instruction provides correct (negative) weighting of the sign bit of a negative multiplier in signed multiplication. The instruction is identical to signed multiply iterate (SMULI) except that M(8N-J) is interpreted as -1 if the sign bit of the multiplier is 1, and 0 if the sign bit of the multiplier is 0.

The unsigned multiply iterate (UMULI) performs an unsigned multiplication iteration. This instruction interprets M(8N-J) as the 8N-J bit of the multiplier. The shift is a double-precision right shift with the carry out from the P(J) + Multiplicand × M(8N-J) operation forced into bit 8N of P(J + 1). This instruction is used in unsigned and mixed multiplication.

# signed multiplication

Signed multiplication performs an 8N + 2 clock two's complement multiply. The instructions necessary to produce an algebraically correct result proceed in the following manner:

Zero register to be used for accumulator

Load MQ with multiplier

SMULI (repeat 8N-1 times) S port = Accumulator

> R port = Multiplicand F port = Iteration result

SMULT S port = Accumulator

R port = Multiplicand F port = Product (MSH)

At completion, the accumulator will contain the 8N most significant bits and the MQ contains the 8N least significant bits of the product.

The status for the signed multiply iterate should not be used for any testing (overflow is not set by SMULI). The following status is set for the signed multiply terminate instruction:

Result MSB equal one OVR Forced to zero

$C_{n+8}$ Carry out equal to one

Double precision result is zero

#### unsigned multiplication

Unsigned multiplication produces an unsigned times unsigned product in 8N + 2 clocks. The instructions necessary to produce an algebraically correct result proceed in the following manner:

Zero register to be used for accumulator

Load MQ with multiplier

UMULI (8N times) S port = Accumulator

R port = Multiplicand

F port = Iteration result (product MSH on final result)

Upon completion, the accumulator will contain the 8N most significant bits and the MQ contains the 8N least significant bits of the product.

The status set by the unsigned multiply iteration is meaningless except on the final execution of the instruction. The status set by the unsigned multiply iteration instruction is as follows:

N → Result MSB equal one

OVR → Forced to zero

Cn+8 → Carry out equal to one

Z → Double-precision result is zero

# mixed multiplication

Mixed multiplication multiplies a signed multiplicand times an unsigned multiplier to produce a signed result in 8N + 2 clocks. The steps are as follows:

Zero register used for accumulator

Load MQ with unsigned multipler

SMULI (8N times) S port = Accumulator

R port = Multiplicand F port = Iteration result

Upon completion, the accumulator will contain the 8N most significant bits and the MQ will contain the 8N least significant bits of the product.

The following status is set by the last SMULI instruction:

N → Result MSB equal one

OVR → Forced to zero

$C_{n+8} \rightarrow Carry out equal to one$

Z → Double-precision result is zero

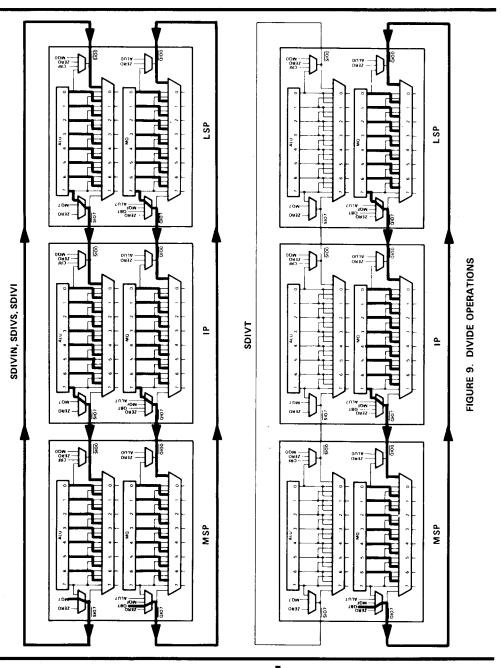

#### divide operations

The divide uses a nonrestoring technique to perform both signed and unsigned division of a 16N bit integer dividend and an 8N bit integer divisor (Figure 9). It produces an 8N integer quotient and remainder.

The remainder and quotient will be such that the following equation is satisfied:

(Quotient) × (Divisor) + Remainder = Dividend

The processor has the following divide instructions:

- 1. UNSIGNED DIVIDE START (UDIVIS): 17-10 = B016

- 2. UNSIGNED DIVIDE ITERATE (UDIVI): 17-10 = C016

- 3. UNSIGNED DIVIDE TERMINATE (UDIVIT): 17-10 = F016

- 4. SIGNED DIVIDE INITIALIZE (SDIVIN): 17-10 = 8016

- 5. SIGNED DIVIDE OVERFLOW TEST (SDIVO): 17-10 = AF16

- 6. SIGNED DIVIDE START (SDIVIS): 17-10 = 9016

- 7. SIGNED DIVIDE ITERATE (SDIVI): 17-10 = A016

- 8. SIGNED DIVIDE TERMINATE (SDIVIT): 17-10 = E016

- 9. DIVIDE REMAINDER FIX (DIVRF): 17-10 = 4016

- 10. SIGNED DIVIDE QUOTIENT FIX (SDIVQF): 17-10 = 5016

The unsigned divide iterate start (UDIVIS) instruction begins the iterate procedure while testing for overflow. Overflow is reported when the first subtraction of the divisor from the MSH of the dividend produces carry out. The test detects quotient overflow and divide by zero.

The unsigned divide iterate terminate (UDIVIT) instruction completes the iterate procedure generating the last quotient bit.

The signed divide initialize (SDIVIN) instruction prepares for iteration by shifting the dividend and storing the sign of the dividend for use in the following instructions and overflow tests.

The signed divide overflow test (SDIVO) checks for overflow possibilities. This instruction may be deleted from the divide operation if the OVR pin is ignored. If it is removed some overflow conditions will go undetected. WE must be high (writing inhibited) when this instruction is used.

The signed divide iterate start (SDIVIS) instruction calculates the difference between the divisor and MSH of the dividend. Partial detection of overflow is also done during this instruction. Operations with like signs (positive quotient) and division by zero will overflow during this instruction (including zero divisor). Operations with unlike signs are tested for overflow during the signed divide quotient fix instruction (SDIVQF). Partial overflow results are saved and will be used during SDIVQF when overflow is reported.

The signed divide iterate (SDIVI) instruction forms the quotient and remainder through iterative subtract/addshift operations of the divisor and dividend. One quotient bit is generated on each clock.

The signed divide iterate terminate (SDIVIT) instruction completes the iterate procedure, generating the last quotient bit. It also tests for a remainder equal to zero, which determines the action to be taken in the following correction (fix) instructions.

The divide remainder fix (DIVRF) instruction corrects the remainder. If a zero remainder was detected by the previous instructions, the remainder is forced to zero. For nonzero remainder cases where the remainder and dividend have the same sign, the remainder is correct. When the remainder and dividend have unlike signs, a correction add/subtract of the divisor to the remainder is performed.

The signed divide quotient fix (SDIVQF) instruction corrects the quotient if necessary. This correction requires adding one to the incorrect quotient. An incorrect quotient results if the signs of the divisor and dividend differ and the remainder is nonzero. An incorrect quotient also results if the sign of the divisor is negative and the remainder is zero.

Overflow detection is completed during this instruction. Overflow may be generated for differing signs of the dividend and divisor. The partial overflow test result performed during SDIVIS is ORed with this test result to produce a true overflow indication.

#### signed divide usage

The instructions necessary to perform an algebraically correct division of signed numbers are as follows:

Load MQ with the least significant half of the dividend

SDIVIN S port = MSH of dividend Divisor Intermediate result F port = SDIVO Result of SDIVIN S port =

> Divisor R port = F port = Test result (WE must be high)

S port = SDIVIS Result of SDIVIN

> R port = Divisor

F port = Intermediate result

| SDIVI (8N-2 times) | S port | = | Result of SDIVIS (or SDIVI) |

|--------------------|--------|---|-----------------------------|

|                    | R port | = | Divisor                     |

|                    | F port | = | Intermediate result         |

| SDIVIT             | S port | = | Result of last SDIVI        |

|                    | R port | = | Divisor                     |

|                    | F port | = | Intermediate result         |

| DIVRF              | S port | = | Result of SDIVIT            |

|                    | R port | = | Divisor                     |

|                    | F port | = | Remainder                   |

| SDIVQF             | S port | = | MQ register                 |

|                    | R port | = | Divisor                     |

|                    | F port | = | Quotient                    |

The status of all signed divide instructions except SDIVIN, DIVRF, and SDIVQF is as follows:

```

Forced to zero

OVR

Forced to zero

C_{n+8}

Carry out equal to one

Intermediate result is zero

```

The status of the SDIVIN instruction is as follows:

```

Ν

Forced to zero

OVR

Forced to zero

C_{n+8}

Forced to zero

Divisor is zero

```

The status of the DIVRF instruction is as follows:

```

Forced to zero

OVR

Forced to zero

Carry out equal to one

Remainder is zero

```

The status of the SDIVQF instruction is as follows:

```

Sign of quotient

OVR

Divide overflow

C_{n+8}

Carry out equal to one

Quotient is zero

```

The quotient is stored in the MQ register and the remainder is stored in the register file location that originally held the most significant word of the dividend. If fractions are divided, the quotient must be shifted right one bit and the remainder right three bits to obtain the correct fractional representations.

The signed division algorithm is summarized in Table 7.

TABLE 7. SIGNED DIVISION ALGORITHM

| OP       | MNEMONIC  | CLOCK               | INPUT               | INPUT   | OUTPUT              |

|----------|-----------|---------------------|---------------------|---------|---------------------|

| E4<br>80 | MINEMONIC | CYCLES              | S PORT              | R PORT  | F PORT              |

| E4       | LOADMQ    | 1                   | Dividend (LSH)      | _       | Dividend (LSH)      |

| 80       | SDIVIN    | 1                   | Dividend (MSH)      | Divisor | Remainder (N)       |

| AF       | SDIVO     | 1                   | Remainder (N)       | Divisor | Test Result         |

| 90       | SDIVIS    | 1                   | Remainder (N)       | Divisor | Remainder (N)       |

| AO       | SDIVI     | 8N - 2 <sup>†</sup> | Remainder (N)       | Divisor | Remainder (N)       |

| EO       | SDIVIT    | 1                   | Remainder (N)       | Divisor | Remainder (Unfixed) |

| 40       | DIVRF     | 1                   | Remainder (Unfixed) | Divisor | Remainder           |

| 50       | SDIVQF    | 1                   | MQ Register         | Divisor | Quotient            |

<sup>&</sup>lt;sup>†</sup>N = Number of cascaded packages.

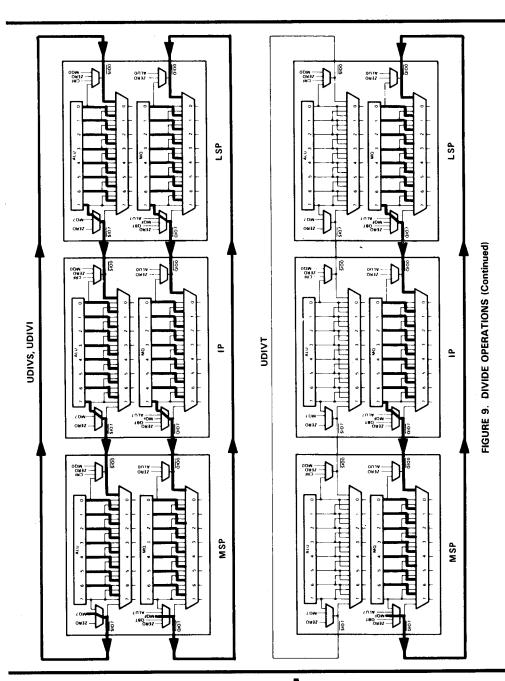

### unsigned divide usage

The instructions necessary to perform an algebraically correct division of unsigned numbers are as follows:

Load MQ with the least significant half of the dividend

UDIVIS S port = MSH of dividend

R port = Divisor

F port = Intermediate result

UDIVI (8N-1 times) S port = Result of UDIVIS (OR UDIVI) R port = Divisor

F port = Intermediate result

UDIVIT S port = Result of last UDIVI

R port = Divisor

F port = Remainder (unfixed)

DIVRF S port = Result of UDIVIT

R port = Divisor F port = Remainder

The status of all unsigned divide instructions except UDIVIS is as follows:

N → Forced to zero

OVR → Forced to zero

$C_{n+8} \rightarrow C_{arry}$  out equal to one

Z → Intermediate result is zero

The status of the UDIVIS instruction is as follows:

N → Forced to zero

OVR → Divide overflow

Cn+8 → Carry out equal to one

Z → Intermediate result is zero

If fractions are divided, the remainder must be shifted right two bits to obtain the correct fractional representation. The quotient is correct as is. The quotient is stored in the MQ register at the completion of the divide.

The unsigned division algorithm is summarized in Table 8.

**TABLE 8. UNSIGNED DIVISION ALGORITHM**

| OP<br>CODE | MNEMONIC | CLOCK<br>CYCLES     | INPUT<br>S PORT     | INPUT<br>R PORT | OUTPUT<br>F PORT    |

|------------|----------|---------------------|---------------------|-----------------|---------------------|

| E4         | LOADMQ   | 1                   | Dividend (LSH)      | -               | Dividend (LSH)      |

| во         | UDIVIS   | 1                   | Dividend (MSH)      | Divisor         | Remainder (N)       |

| co         | UDIVI    | 8N - 1 <sup>†</sup> | Remainder (N)       | Divisor         | Remainder (N)       |

| FO         | UDIVIT   | 1                   | Remainder (N)       | Divisor         | Remainder (Unfixed) |

| 40         | DIVRF    | 1                   | Remainder (Unfixed) | Divisor         | Remainder           |

<sup>†</sup> N = Number of cascaded packages.

## group 5 instructions

Hex code F of Group 1 instructions is used to access Group 5 instructions. Group 5 instructions are summarized in Table 9.

**TABLE 9. GROUP 5 INSTRUCTIONS**

| INSTRUCTION BITS (17-10) OP CODE (HEX) | MNEMONIC | FUNCTION `                   |

|----------------------------------------|----------|------------------------------|

| OF                                     | CLR      | Clear                        |

| 1F                                     | CLR      | Clear                        |

| 2F                                     | CLR      | Clear                        |

| 3F                                     | CLR      | Clear .                      |

| 4F                                     | CLR      | Clear                        |

| 5F                                     | CLR      | Clear                        |

| 6F                                     | CLR      | Clear                        |

| 7F                                     | BCDBIN   | BCD to Binary                |

| 8F                                     | EX3BC    | Excess-3 Byte Correction     |

| 9F                                     | EX3C     | Excess-3 Word Correction     |

| AF                                     | SDIVO    | Signed Divide Overflow Check |

| BF                                     | CLR      | Clear                        |

| CF                                     | CLR      | Clear                        |

| DF                                     | BINEX3   | Binary to Excess-3           |

| EF                                     | CLR      | Clear                        |

| FF                                     | NOP      | No Operation                 |

#### clear instructions (CLR)

There are 11 clear instructions listed in Table 9. The instructions force the ALU output to be zero and the BCD flip-flops to be cleared. The status set by the clear instruction is as follows:

Ν None (force to zero) None (force to zero) OVR  $C_{n+8}$ None (force to zero) Active (one)

## no operation instruction (NOP): 17-10 = FF16

This instruction is identical to the clear instructions except that the BCD flip-flops retain their old value.

# excess-3 correction instructions (EX3BC, EX3C)

Two excess-3 correction instructions are available:

- 1. Excess-3 byte correction (EX3BC): 17-10 = 8F16

- 2. Excess-3 word correction (EX3C): 17-I0 = 9F16

One instruction supports the byte mode and the other supports the word mode. These instructions correct the excess-3 additions (subtractions) in either the byte or word mode. For correct excess-3 arithmetic, this instruction must follow each add/subtract. The operand must be on the S port.

NOTE: The previous arithmetic overflow should be ignored.

The status of the EX3C instruction is as follows:

$\begin{array}{ccc} N & \rightarrow & \text{MSB of result} \\ \text{OVR} & \rightarrow & \text{Signed overflow} \\ \text{$C_{n+8}$} & \rightarrow & \text{Carry out equal one} \\ \text{$z$} & \rightarrow & \text{None (force to one)} \end{array}$

The status of the EX3BC instruction is as follows:

N  $\rightarrow$  None (force to zero) OVR  $\rightarrow$  Byte signed overflow  $C_{n+8}$   $\rightarrow$  Carry out equal one Z  $\rightarrow$  None (force to one)

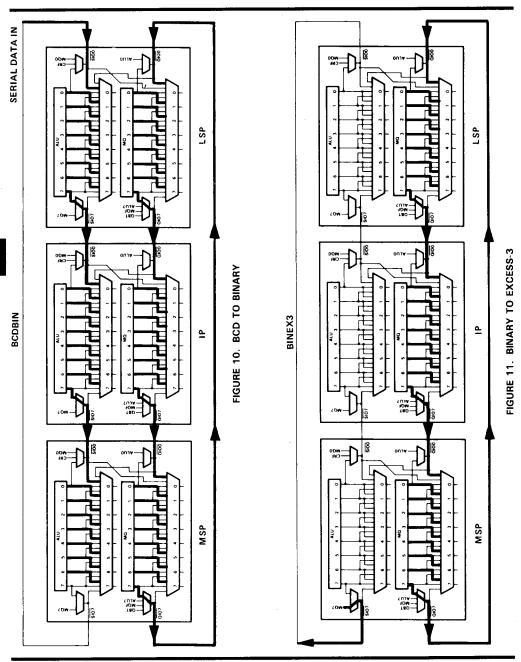

#### radix conversions

Conversions between decimal and binary number representations are performed with the aid of two special instructions: BINEX3 and BCDBIN.

## BCD to binary instructions (BCDBIN): 17-10 = 7F16

This instruction (Figure 10) allows the user to convert an N-digit BCD number to a 4N-bit binary number in 4(N-1) plus 8 clocks. This function sums the R bus, the S bus, and the  $C_n$  bit, performs an arithmetic left shift on the ALU result, and simultaneously circular shifts the MQ left. The status set by the BCD to binary instruction is as follows:

N  $\rightarrow$  MSB of result OVR  $\rightarrow$  Signed arithmetic overflow<sup>†</sup>  $C_{n+8}$   $\rightarrow$  Carry out equal one Z  $\rightarrow$  Result equal zero

<sup>†</sup> Overflow may be the result of an ALU operation or the arithmetic left shift operation.

The following code illustrates the BCD to binary conversion technique.

Let ACC be an accumulator register Let NUM be the register which contains the BCD number Let MSK be a mask register

| M1:   | LOADMQ NUM                      | ; LOAD MQ WITH BCD NUMBER       |

|-------|---------------------------------|---------------------------------|

| M2:   | SUB ACC, ACC, SLCMQ             | ; CLEAR ACC AND ALIGN MQ        |

| M3:   | SUB, MSK, MSK, SLCMQ            | ; CLEAR MSK AND ALIGN MQ        |

| M4:   | SLCMQ                           | ; ALIGN                         |

| M5:   | SLCMQ                           | ; ALIGN                         |

| M6:   | ADDI ACC, MSK, 15 <sub>10</sub> | ; $MSK = 15_{10}$               |

|       |                                 | ; REPEAT L1 THRU L4             |

|       |                                 | ; $N-1$ TIMES ( $N = number of$ |

|       |                                 | ; BCD digits)                   |

| L1:   | AND MQ, MSK, R1, SLCMQ          | ; EXTRACT ONE DIGIT             |

|       |                                 | ; ALIGN MQ                      |

| L2:   | ADD, ACC, R1, R1, SLCMQ         | ; ACC +- DIGIT                  |

|       |                                 | ; IS STORED IN R1               |

|       |                                 | ; ALIGN MQ                      |

| L3:   | BCDBIN, R1, R1, ACC             | ; $4 \times (ACC + DIGIT)$      |

|       |                                 | ; IS STORED IN ACC              |

|       |                                 | ; ALIGN MQ                      |

| L4:   | BCDBIN, ACC, R1, ACC            | $: 10 \times (ACC + DIGIT)$     |

|       | ,,,,,                           | : IS STORED IN ACC              |

|       |                                 | ; ALIGN MQ                      |