# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## Dependable Texas Instruments Quality and Reliability

## description

These latches are ideally suited for use as temporary storage for binary information between processing units and input/output or indicator units. Information present at a data (D) input is transferred to the Q output when the enable (G) is high and the Q output will follow the data input as long as the enable remains high. When the enable goes low, the information (that was setup at the data input at the time the transition occurred) is retained at the Q output until the enable is permitted to go high.

These circuits are completely compatible with all popular TTL families. All inputs are diode-clamped to minimize transmission-line effects and simplify system design. Typical power dissipation is 40 milliwatts per latch.

The SN54100 is characterized for operation over the full military temperature range of  $\sim 55^\circ$  to 125°°C; the SN74100 is characterized for operation from 0°°C to 70°°C.

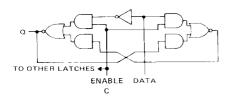

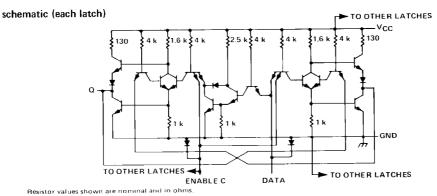

#### logic diagram (each latch)

#### SN54100 ... J OR W PACKAGE SN74100 ... J OR N PACKAGE (TOP VIEW)

| NC[   | 1  | U 24 | □vcc         |

|-------|----|------|--------------|

| 1D1[  | 2  | 23   | ]1C          |

| 1D2   | 3  | 22   | □1D3         |

| 102[  | 4  | 21   | ]1D4         |

| 101   | 5  | 20   | 104          |

| NC[   | 6  | 19   | ]103         |

| GND[  | 7  | 18   | 203          |

| 2Q1 [ | 8  | 17   | <b>]</b> 2Q4 |

| 202   | 9  | 16   | ]2D4         |

| 2D2[  | 10 | 15   | ]2D3         |

| 2D1   | 11 | 14   | □NC          |

| 2C[   | 12 | 13   | ]NC          |

NC -No internal connection

#### FUNCTION TABLE (Each Latch)

| INP | UTS | OUTPUTS    |                      |  |  |  |  |

|-----|-----|------------|----------------------|--|--|--|--|

| D   | G   | Q          | ā                    |  |  |  |  |

| L   | Н   | L          | н                    |  |  |  |  |

| н   | н   | н          | L                    |  |  |  |  |

| x   | L   | $\alpha_0$ | $\bar{\mathbf{q}}_0$ |  |  |  |  |

H = high level, X = irrelevant Ω<sub>0</sub> = the level of Ω before the high-to-low transition of G

# TYPES SN54100, SN74100 8-BIT BISTABLE LATCHES

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1) |         |  |  |  |  |  |  |   |  |   | 7 V            |

|----------------------------------------------|---------|--|--|--|--|--|--|---|--|---|----------------|

| Input voltage                                |         |  |  |  |  |  |  |   |  |   | 5.5 V          |

| Interemitter voltage (see Note 2) .          |         |  |  |  |  |  |  | , |  |   | 5.5 V          |

| Operating free-air temperature range:        | SN54100 |  |  |  |  |  |  |   |  | - | –55°C to 125°C |

|                                              | SN74100 |  |  |  |  |  |  |   |  |   | . 0°C to 70°C  |

| Storage temperature range                    |         |  |  |  |  |  |  |   |  | _ | -65°C to 150°C |

NOTES: 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter input transistor. For this circuit, this rating applies between the enable and D inputs of any latch.

## recommended operating conditions

|                                    |     | N5410 | 0    | . :  |     |      |      |

|------------------------------------|-----|-------|------|------|-----|------|------|

|                                    | MIN | NOM   | MAX  | MIN  | NOM | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>    | 4.5 | 5     | 5.5  | 4.75 | 5   | 5.25 | ٧    |

| High-level output current, IOH     |     |       | -400 |      |     | 400  | μА   |

| Low-level output current, IOL      |     |       | 16   |      |     | 16   | mA   |

| Width of enabling pulse, tw        | 20  |       |      | 20   | _   |      | ns   |

| Setup time, t <sub>SU</sub>        | 20  |       |      | 20   | _   |      | ns   |

| Hold time, th                      | 5   |       |      | 5    |     |      | ns   |

| Operating free-air temperature, TA | 55  |       | 125  | 0    |     | 70   | °C   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                              |                    | TEST CO                                            | NDIT                                    | IONS†                   | MIN           | TYP      | MAX           | UNIT |

|-----------------|----------------------------------------|--------------------|----------------------------------------------------|-----------------------------------------|-------------------------|---------------|----------|---------------|------|

| VIH             | High-level input voltage               |                    |                                                    |                                         |                         | 2             |          |               | V    |

| VIL             | Low-level input voltage                |                    |                                                    |                                         |                         |               |          | 0.8           | V    |

| Vik             | Input clamp voltage                    | _                  | V <sub>CC</sub> = MIN,                             | 11=                                     | -12 mA                  |               |          | 1.5           | ٧    |

| v <sub>он</sub> | High-level output voltage              |                    | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | • • • • • • • • • • • • • • • • • • • • | i = 2 V,<br>i = −400 μA | 2.4           | 3.4      |               | V    |

| VOL             | Low-level output voltage               |                    | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, |                                         | j = 2 V,<br>= 16 mA     |               | 0.2      | 0.4           | v    |

| 11              | Input current at maximum input voltage |                    | V <sub>CC</sub> = MAX,                             | VI                                      | = 5.5 V                 |               |          | 1             | mΑ   |

| ЧН              | High-level input current               | D input<br>C input | V <sub>CC</sub> = MAX,                             | V <sub>I</sub>                          | = 2.4 V                 | _             |          | 80<br>320     | μА   |

| IL              | Low-level input current                | D input<br>C input | V <sub>CC</sub> = MAX,                             | ٧ı                                      | = 0.4 V                 |               |          | -3.2<br>-12.8 | mA   |

| los             | Short-circuit output current §         |                    | V <sub>CC</sub> = MAX                              |                                         | SN54100<br>SN74100      | -20<br>-18    |          | -57<br>-57    | mA   |

| lcc             | Supply current                         | _                  | V <sub>CC</sub> = MAX,<br>See Note 3               |                                         | SN54100<br>SN74100      | <del> -</del> | 64<br>64 | 92<br>106     | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

NOTE 3: ICC is tested with all inputs grounded and all outputs open.

$<sup>^{\</sup>ddagger}$  All typical values are at V  $_{CC}$  = 5 V, T  $_{A}$  = 25 °C.

Not more than one output should be shorted at a time.

## switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETER¶       | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                       | MIN | TYP | MAX | UNIT  |

|------------------|-----------------|----------------|---------------------------------------|-----|-----|-----|-------|

| t <sub>PLH</sub> |                 |                | 0 45 5                                | -   | 16  | 30  | ns    |

| tPHL             | D               | l a            | C <sub>L</sub> = 15 pF,               |     | 14  | 25  | 1 113 |

| tPLH             |                 |                | R <sub>L</sub> = 400 Ω,<br>See Note 4 |     | 16  | 30  | ns    |

| tpHI             | C               | l a            | See Note 4                            |     | 7   | 15  | ] ""_ |

<sup>¶</sup>tpLH = propagation delay time, low-to-hgih-level output tpHL = propagation delay time, high-to low-level output

NOTE 4: Load circuits and voltage waveforms are the same as those shown for the '75, '77, 'L75, and 'L77.