# **SOIC Thin Film on Ceramic Resistor Networks**

### **SOIC-C Series**

### **Features**

- Tested for COTS applications

- Both narrow and wide body versions available

- Standard JEDEC 8, 14, 16, and 20 pin packages

- Ultra-stable TaN resistors on ceramic substrate

- Lower crosstalk than silicon substrate types

All parts are Pb-free and comply with EU Directive 2011/65/EU amended by (EU) 2015/863 (RoHS3)

SOIC-C resistor networks are high density, low crosstalk networks which combine high precision with the stability and reliability associated with the self-passivating tantalum nitride film system.

### **Electrical Data**

| Resistance Range                                                      | 100R – 200K               |              |  |

|-----------------------------------------------------------------------|---------------------------|--------------|--|

| Absolute Tolerance                                                    | To ±0.1%                  |              |  |

| Ratio Tolerance to R1                                                 | To ±0.05%                 |              |  |

| Absolute TCR                                                          | To ±25ppm/°C              |              |  |

| Tracking TCR                                                          | To ±5ppm/°C               |              |  |

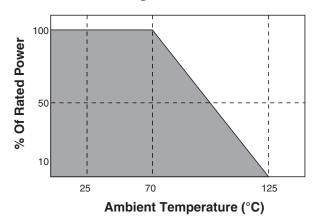

| Element Power Rating @ 70°C<br>Isolated Schematic<br>Bussed Schematic | 100mW<br>50mW             |              |  |

| Power Rating @ 70°C<br>SOIC-N Package                                 | 8-Pin<br>14-Pin<br>16-Pin | 700mW        |  |

| Power Rating @ 70°C<br>SOIC-W Package                                 | 16-Pin<br>20-Pin          | 1.2W<br>1.5W |  |

| Rated Operating Voltage (not to exceed √Power X Resistance)           | 100 Volts                 |              |  |

| Operating Temperature                                                 | -55°C to ±125°C           |              |  |

| Noise                                                                 | <-25dB                    |              |  |

### **Environmental Data**

| Test Per<br>MIL-PRF-83401    | Typical<br>Delta R | Max<br>Delta R |

|------------------------------|--------------------|----------------|

| Thermal Shock                | ±0.02%             | ±0.1%          |

| Power<br>Conditioning        | ±0.03%             | ±0.1%          |

| High Temperature<br>Exposure | ±0.03%             | ±0.05%         |

| Short-time<br>Overload       | ±0.02%             | ±0.05%         |

| Low Temperature<br>Storage   | ±0.03%             | ±0.05%         |

| Life                         | ±0.05%             | ±0.1%          |

## **SOIC Thin Film on Ceramic Resistor Networks**

### **SOIC-C Series**

# Physical and Schematic Data

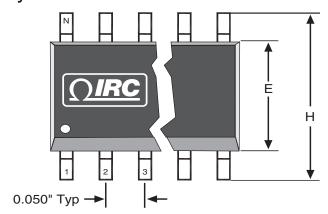

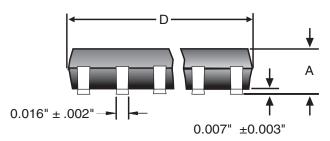

|   | SOIC-N                              |                                 |                                  | SOIC-W                           |                                  |  |

|---|-------------------------------------|---------------------------------|----------------------------------|----------------------------------|----------------------------------|--|

|   | 8-Pin 14-Pin                        |                                 | 16-Pin                           | 16-Pin                           | 20-Pin                           |  |

| D | 0.193"±0.004                        |                                 | 0.390"±0.004<br>(9.906 ± 0.102)  | 0.402"±0.004<br>(10.211 ± 0.102) | 0.502"±0.004<br>(12.751 ± 0.102) |  |

| н |                                     | 0.236"±0.008<br>(5.994 ± 0.203) | 0.406"±0.008<br>(10.312 ± 0.203) |                                  |                                  |  |

| Е | 0.153"±.004<br>(3.886 ± 0.102)      |                                 |                                  | 0.295"±0.004<br>(7.493 ± 0.102)  |                                  |  |

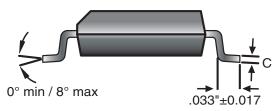

| Α | 0.064"±0.004<br>(1.626 ± 0.102)     |                                 |                                  | 0.100"±0.004<br>(2.540 ± 0.102)  |                                  |  |

| С | 0.0075" - 0.010"<br>(0.191 ± 0.254) |                                 |                                  | 0.011"±0.002<br>(0.279 ± 0.051)  |                                  |  |

Note: All dimesions exclude mold flash and end flash which shall not exceed 0.006" per side.

Note: Lead Coplanarity 0.004" Max.

# Schematic A Isolated Schematic B Bussed

# **Power Derating Curve**

For additional information or to discuss your specific requirements, please contact our Applications Team using the contact details below.

# **SOIC Thin Film on Ceramic Resistor Networks**

**SOIC-C Series**

# **Ordering Procedure**

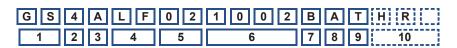

**Example: GS4ALF021002BATHR** (8 pin narrow SOIC, isolated elements, 50ppm/°C, 10 kilohms, absolute tolerance ±0.1%, ratio tolerance ±0.05%, tube packed, variant HR, Pb-free)

| 1      | 2        | 3          | 4           | 5             | 6            | 7                     | 8                  | 9       | 10       |

|--------|----------|------------|-------------|---------------|--------------|-----------------------|--------------------|---------|----------|

| Туре   | Size     | Schematic  | Termination | TCR           | Value        | Absolute<br>Tolerance | Ratio<br>Tolerance | Packing | Variant  |

| GS =   | 4=8 pin  | A=Isolated | LF=Pb-free  | 01=±100ppm/°C | 3 digits +   | B=±0.1%               | A=±0.05%           | T=Tube  | Optional |

| Narrow | 7=14 pin | B=Bussed   |             | 02=±50ppm/°C  | multiplier   | C=±0.25               | B=±0.1%            | R=Reel  | code -   |

| SOIC   | 8=16 pin |            |             | 03=±25ppm/°C  | R = ohms for | D=±0.5%               | C=±0.25%           |         | see      |

| GL =   | 0=20 pin |            |             |               | values < 100 | F=±1%                 | D=±0.5%            |         | below    |

| Wide   |          | •          |             |               | ohms         | G=±2%                 | F=±1%              |         |          |

| SOIC   |          |            |             |               |              | J=±5%                 | G=±2%              |         |          |

| Variant codes |                                                      |  |  |  |

|---------------|------------------------------------------------------|--|--|--|

| Blank         | Standard                                             |  |  |  |

| HR            | High reliability screened (50 cycles, thermal shock) |  |  |  |

Note: The Variant code may be placed between Schematic and Termination. Type may be preceded by the optional prefix **GUL**-, e.g. **GUL-GS4ALF021002BATHR**