# Supertex inc.

# **High-Voltage Ring Generator**

#### **Ordering Information**

| Operating Voltage | Package Options |

|-------------------|-----------------|

| V <sub>NN1</sub>  | SOW-16          |

| -220V             | HV450WG         |

#### **Features**

- Integrated high voltage transistors

- ☐ 67V<sub>RMS</sub> ring signal

- Output over current protection

- Can drive external MOSFETs for larger loads

#### **Applications**

- High voltage ring generator

- Set-top/Street box ring generator

- Pair gain ring generator

### General Description

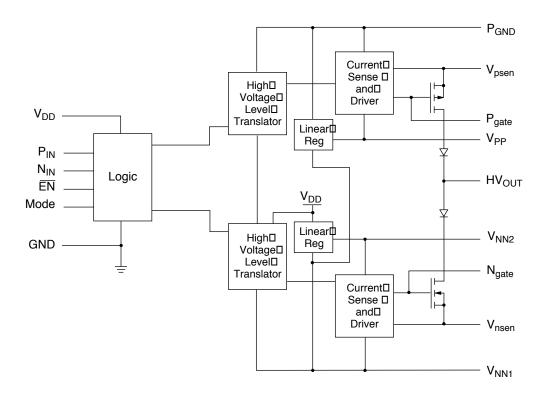

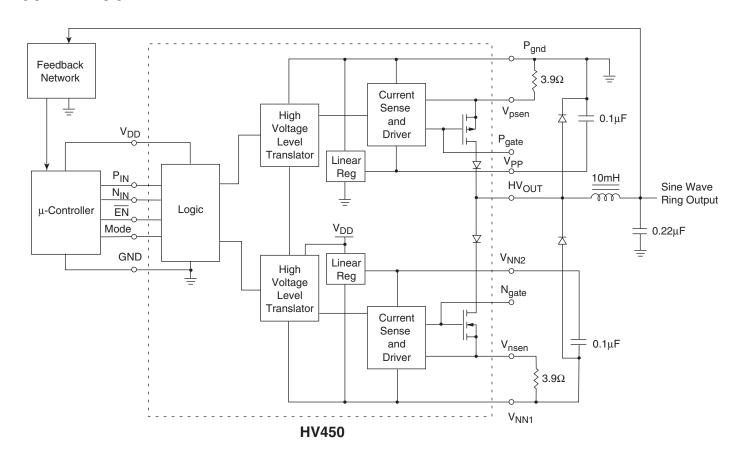

The Supertex HV450 is a PWM high voltage ring generator. The high voltage output P- and N-channel transistors are controlled independently by the logic inputs  $P_{\rm IN}$  and  $N_{\rm IN}$ . For application where a single control pin  $(N_{\rm IN})$  is desired, the mode pin should be connected to Gnd. This adds a 200ns deadband on the control logic to avoid cross conduction on the high voltage output. A logic high on  $N_{\rm IN}$  will turn the high voltage P-Channel on and the N-Channel off. The outputs can drive up to 5 RENs. The HV450 can drive external MOSFETs for applications requiring larger loads. The IC can be powered down by connecting the enable pin to  $V_{\rm DD}$ . The high voltage outputs have pulse by pulse over current protection.

### **Absolute Maximum Ratings\***

| V <sub>NN1</sub> , power supply voltage          | -240V                 |

|--------------------------------------------------|-----------------------|

| V <sub>PP</sub> , P-channel gate voltage supply  | -20V                  |

| V <sub>NN2</sub> , N-channel gate voltage supply | V <sub>NN1</sub> +20V |

| V <sub>DD</sub> , logic supply                   | +7.5V                 |

| Storage temperature                              | -65°C to +150°C       |

| Power dissipation                                | 600mW                 |

<sup>\*</sup> All voltages referenced to ground

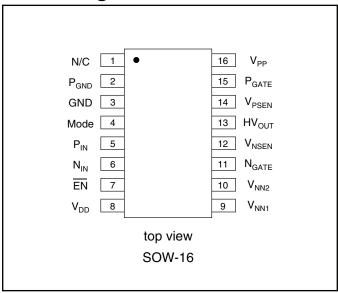

#### **Pin Configuration**

# **Electrical Characteristics**

(Over operating supply voltages unless otherwise specified,  $T_A$  = -40°C to +85°C.)

| Symbol            | Parameters                                | Min                    | Тур | Max                     | Unit | Conditions                                                           |

|-------------------|-------------------------------------------|------------------------|-----|-------------------------|------|----------------------------------------------------------------------|

| V <sub>PP</sub>   | P-channel linear regulator output voltage | -10                    |     | -18                     | V    |                                                                      |

| V <sub>NN1</sub>  | High voltage negative supply              | - 220                  |     | -110                    | V    |                                                                      |

| V <sub>NN2</sub>  | Negative linear regulator output voltage  | V <sub>NN1</sub> + 6.0 |     | V <sub>NN1</sub> + 10.0 | ٧    |                                                                      |

| $V_{DD}$          | Logic supply voltage                      | 4.5                    |     | 5.5                     | ٧    |                                                                      |

| I <sub>NN1Q</sub> | V <sub>NN1</sub> quiescent current        |                        | 300 | 500                     | μA   | $P_{IN} = N_{IN} = \overline{EN} = L$                                |

|                   |                                           |                        |     | 25                      | μΑ   | $P_{IN} = N_{IN} = L, \overline{EN} = H$                             |

| I <sub>DDQ</sub>  | V <sub>DD1</sub> quiescent current        |                        | 90  | 200                     | - μΑ | $P_{IN} = N_{IN} = \overline{EN} = L$                                |

|                   |                                           |                        | 35  | 100                     |      | $P_{IN} = N_{IN} = L, \overline{EN} = H$                             |

| I <sub>NN1</sub>  | V <sub>NN1</sub> operating current        |                        | 1.4 |                         | mA   | No load, $V_{\text{OUTP}}$ and $V_{\text{OUTN}}$ switching at 100KHz |

| I <sub>DD</sub>   | V <sub>DD</sub> operating current         |                        |     | 1.0                     | mA   |                                                                      |

| I <sub>IL</sub>   | Mode logic input low current              |                        | 25  |                         | μΑ   | Mode = 0V                                                            |

| V <sub>IL</sub>   | Logic input low voltage                   | 0                      |     | 1.0                     | V    | $V_{DD} = 5.0V$                                                      |

| V <sub>IH</sub>   | Logic input high voltage                  | 4.0                    |     | 5.0                     | V    | V <sub>DD</sub> = 5.0V                                               |

#### **High Voltage Output**

| Symbol              | Parameters                                                               | Min                    | Тур | Max                    | Unit | Conditions                          |

|---------------------|--------------------------------------------------------------------------|------------------------|-----|------------------------|------|-------------------------------------|

| R <sub>SOURCE</sub> | V <sub>OUT</sub> P source resistance                                     |                        | 65  |                        | Ω    | I <sub>OUT</sub> = 100mA            |

| R <sub>SINK</sub>   | V <sub>OUT</sub> P sink resistance                                       |                        | 65  |                        | Ω    | I <sub>OUT</sub> = -100mA           |

| t <sub>d(ON)</sub>  | HV <sub>OUT</sub> delay time                                             |                        | 150 |                        | ns   | $P_{IN}$ = high to low, Mode = high |

| t <sub>rise</sub>   | HV <sub>OUT</sub> rise time                                              |                        | 50  |                        | ns   | P <sub>IN</sub> = high to low       |

| t <sub>d(OFF)</sub> | HV <sub>OUT</sub> delay time                                             |                        | 200 |                        | ns   | $N_{IN}$ = low to high, Mode = high |

| t <sub>fall</sub>   | HV <sub>OUT</sub> fall time                                              |                        | 50  |                        | ns   | N <sub>IN</sub> = low to high       |

| t <sub>db</sub>     | Logic deadband time                                                      |                        | 250 |                        | ns   | Mode = low                          |

| V <sub>psen</sub>   | HV <sub>OUT</sub> current source sense voltage                           | -1.2                   |     | -0.8                   | V    |                                     |

| V <sub>nsen</sub>   | HV <sub>OUT</sub> current sink sense voltage                             | V <sub>NN1</sub> + 0.8 |     | V <sub>NN1</sub> + 1.2 | V    |                                     |

| t <sub>shortP</sub> | HV <sub>OUT</sub> off delay time when current source sense is activiated |                        | 70  | 150                    | ns   |                                     |

| t <sub>shortN</sub> | HV <sub>OUT</sub> off delay time when current sink sense is activated    |                        | 70  | 150                    | ns   |                                     |

| t <sub>whout</sub>  | Minimum pulse width for HV <sub>OUT</sub> at P <sub>GND</sub>            |                        |     | 500                    | ns   |                                     |

| t <sub>wlout</sub>  | Minimum pulse width for $HV_{OUT}$ at $V_{NN1}$                          |                        |     | 500                    | ns   |                                     |

### **Truth Table**

| N <sub>IN</sub> | P <sub>IN</sub> | Mode | EN | $HV_out$              |

|-----------------|-----------------|------|----|-----------------------|

| L               | L               | Н    | L  | Pgnd                  |

| L               | Н               | Н    | L  | High Z                |

| H*              | L*              | Н    | L  | *                     |

| Н               | Н               | Н    | L  | V <sub>NN1</sub>      |

| L               | X               | L    | L  | $V_{_{\mathrm{NN1}}}$ |

| Н               | X               | L    | L  | Pgnd                  |

| Х               | X               | X    | Н  | High Z                |

<sup>\*</sup>This state will short  $\boldsymbol{V}_{_{\boldsymbol{NN1}}}$  to Pgnd and should therefore be avoided.

# **Block Diagram**

#### **Pin Description**

| V <sub>PP</sub>   | P-channel gate voltage supply. Generated by an internal linear regulator. A $0.1\mu F$ capacitor should be connected between $P_{GND}$ and $V_{PP}$ .                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>NN1</sub>  | Negative high voltage supply.                                                                                                                                                                          |

| V <sub>NN2</sub>  | N-channel gate voltage supply. Generated by an internal linear regulator. A $0.1\mu F$ capacitor should be connected between $V_{NN2}$ and $V_{NN1}$ .                                                 |

| $V_{DD}$          | Logic supply voltage.                                                                                                                                                                                  |

| GND               | Low voltage ground.                                                                                                                                                                                    |

| $P_{GND}$         | High voltage power ground.                                                                                                                                                                             |

| P <sub>IN</sub>   | Logic control input. When mode is high, logic input high turns OFF output high voltage P-Channel.                                                                                                      |

| N <sub>IN</sub>   | Logic control input. When mode is high, logic input high turns ON output high voltage N-Channel.                                                                                                       |

| EN                | Logic enable input. Logic low enables IC.                                                                                                                                                              |

| Mode              | Logic mode input. Logic low activates 200nsec deadband. When mode is low, $N_{IN}$ turns on and off the high voltage N- and P-Channels. Pin is not used and should be connected to $V_{DD}$ or ground. |

| HV <sub>OUT</sub> | High voltage output. Voltage swings from P <sub>GND</sub> to V <sub>NN1</sub> .                                                                                                                        |

| $V_{\rm psen}$    | Pulse by pulse over current sensing for P-Channel MOSFET.                                                                                                                                              |

| V <sub>nsen</sub> | Pulse by pulse over current sensing for N-Channel MOSFET.                                                                                                                                              |

| P <sub>gate</sub> | Gate drive for external P-channel MOSFET.                                                                                                                                                              |

| N <sub>gate</sub> | Gate drive for external N-channel MOSFET.                                                                                                                                                              |

|                   |                                                                                                                                                                                                        |

# **Typical Application Circuit**

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip:

HV450DB2 HV450DB1