#### **Descriptions**

FSA4480UCX is a high performance USB Type-C switch combo of High-Speed Data, Hi-Fi Audio and Side Band Use(SBU). The Audio path is capable of wide audio swing and results in ultra-low distortion. With excellent THD+N performance and wide frequency response, FSA4480UCX is an ideal device for Hi-Fi system application. The USB path of wide bandwidth has very low bit-to-bit skew and channel-to-channel cross-talk, and it is compatible with high-speed USB 2.0 eye diagram and maintains good signal integrity.

The Side Band Use (SBU) configures internal switches to Ground and MIC connections on headset. GND sense path supports quasi-differential amplifier architectures, which reduces cross-talk and improves sound quality. SBU ports can also be configured to deliver eDP AUX signal.

FSA4480UCX incorporates High Voltage Protection (OVP) to both SBU and USB ports on Type-C receptacle side. Both GPIO and I2C controls are 1.8V logic compatible. 25-Ball Wafer Level Chip Scale Package (WLCSP) 2.04mm x 2.04mm with Pb-free and Halogen-free, makes it ideal for mobile device.

#### **Features**

- Wide VCC Supply Range (2.5v~25v) can be powered by either LDO or VBUS

- USB Path Insertion loss: -1dB@430MHz, -2dB@930MHz, -3dB@1.4GHz

- Hi-Fi Audio Path: THD+N=-110dB, 0.707Vrms, f=100Hz, 32Ω Load,

- Audio Path Insertion loss: -1dB@500MHz, -2dB@860MHz, -3dB@1.2GHz

- In-Built OVP to both DC 16V-tolerant SBUx/GSBUx ports and DC 17V-tolerant DP\_R/DN\_L ports on Type-C receptacle

- IEC 64000-4-5 Surge Protection w/o External TVS: DP\_R/DN\_L ports 20V, SBUx/GSBUx ports: 80V

- OMTP and CTIA Pinout Support and Audio Sense Path for Quasi Differential Configuration

- Audio Path Soft Turn-On/Off for Pop & Click Elimination

- Power-off Truly Isolated and Noise Removal

- Configurable to Deliver eDP AUX Signal

### **Applications**

USB Type-C Receptacle, 4G/5G Smart Phone, Mobile and Al Device

#### Order Information

| Part Number | Pack   | age           |

|-------------|--------|---------------|

| FSA4480UCX  | CSP-25 | Tape and Reel |

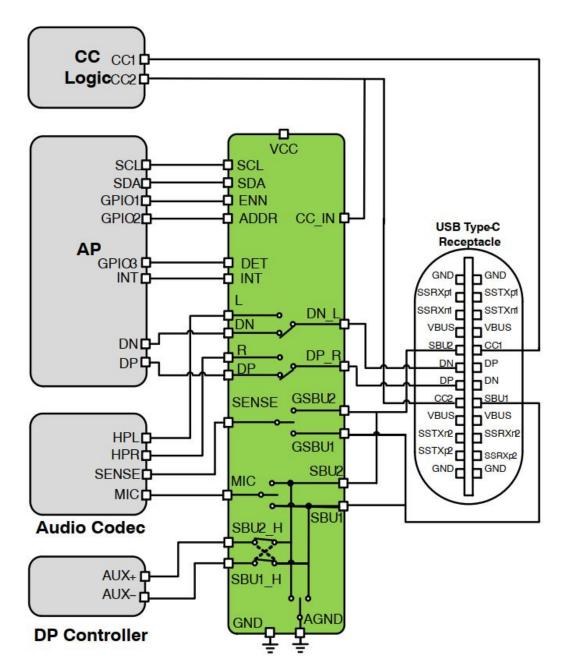

## **Functional Diagram**

Fig.1 Functional Diagram

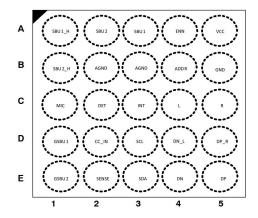

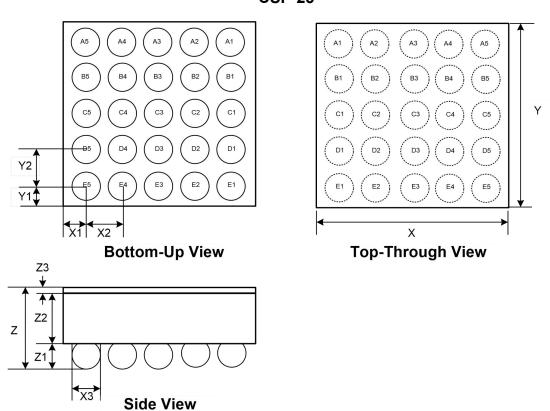

# **Pin Configuration**

CSP-25

## **Pin Descriptions**

| Pin# | Name   | Туре | Description                                                              |

|------|--------|------|--------------------------------------------------------------------------|

| A5   | VCC    | PWR  | 2.5~25V Positive Supply                                                  |

| B5   | GND    | GND  | Primary Ground Connection. Must be Connected to System Ground            |

| D5   | DP_R   | I/O  | Right Audio / Positive USB2.0 Data Common Line                           |

| D4   | DN_L   | I/O  | Left Audio / Negative USB2.0 Data Common Line                            |

| E5   | DP     | I/O  | Positive USB2.0 Data Line                                                |

| E4   | DN     | I/O  | Negative USB2.0 Data Line                                                |

| C5   | R      | I/O  | Right Line for Audio Signals                                             |

| C4   | L      | I/O  | Left Line for Audio Signals                                              |

| А3   | SBU1   | I/O  | Sideband Use wire 1                                                      |

| A2   | SBU2   | I/O  | Sideband Use wire 2                                                      |

| C1   | MIC    | 0    | Analog Audio Microphone                                                  |

| B2   | AGND2  | GND  | Analog Ground 2                                                          |

| В3   | AGND1  | GND  | Analog Ground 1                                                          |

| E2   | SENSE  | 0    | Analog Ground Sense Return                                               |

| C3   | INT    | 0    | Open Drain Interrupt Output                                              |

| D2   | CC_IN  | I    | Audio Accessory Attachment Detection Input                               |

| D1   | GSBU1  | I/O  | Star-connection with SBU1 to Headset Jack as Audio Ground Sense Path 1   |

| E1   | GSBU2  | I/O  | Star-connection with SBU2 to Headset Jack as Audio Ground Sense Path 2   |

| C2   | DET    | 0    | Push-pull output. DET changes status in response to CC_IN voltage level. |

| D3   | SCL    | I    | I2C Clock wire                                                           |

| E3   | SDA    | I/O  | I2C Data wire                                                            |

| B1   | SBU2_H | I    | System Side Sideband Use wire 2, can be configured as eDP AUX path       |

| A1   | SBU1_H | I    | System Side Sideband Use wire 1, can be configured as eDP AUX path       |

| A4   | ENN    | I    | Chip Enable, Active Low, Internal Pull-Down by 470KΩ                     |

| B4   | ADDR   | I    | I2C Slave Address                                                        |

**Table-1 Pin Descriptions**

# FSA4480UCX High-Speed Data/Hi-Fi Audio Switch

## Absolute Maximum Ratings over operating free-air temperature range (unless otherwise noted) (1)

|                           |                                          | Range      | Unit |

|---------------------------|------------------------------------------|------------|------|

| Power Supply Voltage      | VCC                                      | -0.5 ~ 25  | V    |

| Central Dina              | SCL, SDA, ADDR, ENN, INT_N               | -0.5 ~ 6.5 | V    |

| Control Pins              | CC_IN                                    | -0.5 ~ 25  | V    |

|                           | DP_R, DN_L                               | -3.3 ~ 17  | V    |

| Signal Pins               | L, R, DP, DN, MIC, SENSE, SBU1_H, SBU2_H | -0.3 ~ 6.5 | V    |

|                           | SBU1, GSBU1, SBU2, GSBU2                 | -0.3 ~ 16  | V    |

| Storage Temperature Range | TSTG                                     | -55 ~ 150  | οС   |

|                           | VCC                                      | ±8         | kV   |

| ESD HBM, ANSI/            | SCL, SDA, ADDR, ENN, INT_N               | ±8         | kV   |

| ESDA/JEDEC                | CC_IN                                    | ±8         | kV   |

| JS-001-2012               | DP_R, DN_L                               | ±8         | kV   |

|                           | L, R, DP, DN, MIC, SENSE, SBU1_H, SBU2_H | ±8         | kV   |

|                           | SBU1, GSBU1, SBU2, GSBU2                 | ±8         | kV   |

|                           | VCC                                      | ±400       | V    |

|                           | SCL, SDA, ADDR, ENN, INT_N               | ±400       | V    |

| ECD MM JECDOO A445        | CC_IN                                    | ±400       | V    |

| ESD MM, JESD22-A115       | DP_R, DN_L                               | ±300       | V    |

|                           | L, R, DP, DN, MIC, SENSE, SBU1_H, SBU2_H | ±400       | V    |

|                           | SBU1, GSBU1, SBU2, GSBU2                 | ±800       | V    |

| ESD CDM, JESD22-C101      | All Pins                                 | ±1500      | V    |

#### **Table-2 Absolute Maximum Ratings**

## **Recommend Operating Conditions**

|                       |                                    | Range      | Unit |

|-----------------------|------------------------------------|------------|------|

| Power Supply Voltage  | VCC                                | 2.7 ~ 20   | V    |

| Control Pins          | SCL, SDA, ADDR, ENN, INT_N         | 0 ~ 5.0    | V    |

| Control Pins          | CC_IN                              | 0 ~ 20     | V    |

|                       | L, R, DP_R, DN_L                   | -3.6 ~ 5.0 | V    |

| Signal Pins           | DP, DN, MIC, SENSE, SBU1_H, SBU2_H | 0 ~ 5.0    | V    |

|                       | SBU1, GSBU1, SBU2, GSBU2           | 0 ~ 3.6    | V    |

| Operating Temperature | T <sub>A</sub>                     | -40 ~ 85   | οС   |

### **Table-3 Recommend Operating Conditions**

(1) In USB mode, any signal applied to the off-state audio inputs R, L may not swing below ground or above 1V

Stresses beyond those listed in Table-2 Absolute Maximum Ratings may cause permanent damage to the device. They are stress ratings only, which do not imply functional operation of the device at these or any other conditions. Beyond those indicated under Recommended Operating Conditions, exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Electrical Characteristics (Ta=25°C, VCC=3.3V, unless otherwise specified)

| Parameter                                                | Symbol                | Conditions                                              | Min. | Typ. | Max. | Unit |

|----------------------------------------------------------|-----------------------|---------------------------------------------------------|------|------|------|------|

| Power Supplies                                           |                       |                                                         |      |      |      | I.   |

| Under Voltage Lock Out (UVLO)                            | V <sub>UVLO</sub>     |                                                         | 2.2  | 2.4  | 2.6  | V    |

| UVLO Hysteresis                                          | V <sub>UVLO-HYS</sub> |                                                         | 150  | 200  | 250  | mV   |

| •                                                        | 0,10,1110             | ENN=H, All switches off                                 |      | 180  |      | uA   |

|                                                          |                       | USB switches on                                         |      | 180  |      | uA   |

| VCC Quiescent Current                                    | $I_{Q}$               | Audio switches on along                                 |      |      |      |      |

|                                                          |                       | with MIC and SENSE                                      |      | 270  |      | uA   |

| Digital I/O                                              |                       | switches on                                             |      |      | 1    | I    |

| Input logic high                                         | V <sub>IH</sub>       | VCC=3.3~20V                                             | 1.6  |      | 5.5  | V    |

| Input logic low                                          | V <sub>IL</sub>       | VCC=3.3~20V                                             | -0.1 |      | 0.5  | V    |

| INT Internal pull-up resistor                            | R <sub>UP-INT</sub>   |                                                         |      | 2    |      | МΩ   |

| CC_IN Internal pull-up resistor                          | R <sub>UP-CC</sub>    |                                                         |      | 2    |      | МΩ   |

| SCL, SDA Internal pull-up resistor                       | R <sub>UP-I2C</sub>   |                                                         |      | 2    |      | МΩ   |

| ADDR Internal pull-down resistor                         | R <sub>DN-ADDR</sub>  |                                                         |      | 2    |      | МΩ   |

| ENN Internal pull-down resistor                          | R <sub>DN-ENN</sub>   |                                                         |      | 470  |      | kΩ   |

| Audio Switch On Resistance                               |                       |                                                         |      |      |      |      |

| On-Resistance                                            | R <sub>AUDIO</sub>    | V <sub>IS</sub> = -3.3V~+3.3V I <sub>OUT</sub> =30mA    |      | 1.3  |      | Ω    |

| R <sub>ON</sub> Flatness <sup>(1)</sup>                  | R <sub>FLAT(A)</sub>  | V <sub>IS</sub> = -3.3V~+3.3V I <sub>OUT</sub> =30mA    |      | 0.01 |      | Ω    |

| R <sub>ON</sub> Matching Between Channels <sup>(2)</sup> | $\Delta R_{ON(A)}$    | V <sub>IS</sub> = -3.3V~+3.3V I <sub>OUT</sub> =30mA    |      | 0.02 |      | Ω    |

| Audio Switch Dynamics                                    |                       |                                                         |      |      |      |      |

|                                                          |                       | f=20Hz to 22KHz, A-weighted                             |      | -106 |      | dB   |

| Total Harmonic Distortion                                | THD+N                 | $V_{IS}$ =1 $V$ rms @ $R_L$ =1 $k\Omega$                |      |      |      | ub   |

| Total Haimonic Distortion                                | THD+N₁                | f=20Hz to 22kHz, A-weighted                             | -110 | -103 |      | dB   |

|                                                          |                       | $V_{IS}$ =0.7Vrms @RL=32 $\Omega$                       | -110 | -103 |      | uБ   |

| Signal-to-Noise Ratio                                    | SNR₁                  | f=20Hz to 22KHz,                                        |      | >120 |      | dBrA |

| Signal-to-Noise Italio                                   | SINIX <sub>1</sub>    | Inputs grounded @R <sub>L</sub> =32Ω                    | >120 |      |      | UDIA |

| Audio Switches OFF Isolation                             | OIRR                  | f=20Hz to 22KHz,                                        |      | -91  |      | dB   |

| Addio Owitories Of F Isolation                           | Oliviv                | $V_L = V_R = 0.3 Vrms @R_L = 32\Omega$                  |      | -51  |      | ub   |

| Audio Switches Crosstalk (3)                             |                       | f=20Hz to 22KHz,                                        |      |      |      |      |

| (Channel-to-Channel)                                     | ACRX                  | $V_{L \text{ or R}} = 0.3 \text{Vrms } @R_L = 32\Omega$ |      | -115 |      | dB   |

| (Griannier to Griannier)                                 |                       | Source Impedance= $0\Omega R_L = 1k\Omega$              |      |      |      |      |

| Audio Switch -3dB Bandwidth                              | $BW_{Audio}$          | R <sub>L</sub> =50Ω                                     |      | 1.2  |      | GHz  |

| AUDIO Switch Turn-on Time                                | t <sub>ON-A</sub>     | $V_{IS}$ = 50mV R <sub>L</sub> =32 $\Omega$             |      | 60   |      | mS   |

| AUDIO Switch Turn-off Time                               | t <sub>OFF-A</sub>    | $V_{IS}$ = 50mV R <sub>L</sub> =32 $\Omega$             |      | 5    |      | mS   |

| USB Switch On Resistance                                 |                       |                                                         |      |      | i    | 1    |

| On-Resistance                                            | Rusa                  | $V_{IS} = 0V \sim 0.4V$ , $I_{ON} = 8mA$                |      | 3.5  |      | Ω    |

| R <sub>ON</sub> Flatness                                 | R <sub>FLAT(U)</sub>  | $V_{IS} = 0V \sim 3.3V$ , $I_{ON} = 8mA$                |      | 4.8  |      | Ω    |

| R <sub>ON</sub> Matching Between Channels                | $\Delta R_{ON(U)}$    | $V_{IS} = 0V \sim 0.4V$ , $I_{ON} = 8mA$                |      | 0.2  |      | Ω    |

| USB Switch Dynamics                                      |                       |                                                         | 1    |      |      | 1    |

| USB Switch On Capacitance                                | C <sub>ON</sub>       | $V_{Bias} = 0.2V, f = 1MHz$                             |      | 4    |      | pF   |

| USB Switch Off Capacitance                               | $C_{OFF}$             | $V_{Bias} = 0.2V$ , $f = 1MHz$                          |      | 3    |      | pF   |

# High-Speed Data/Hi-Fi Audio Switch

| USB Switch Off Isolation     | Off <sub>USB</sub>       | $f = 100MHz, R_T = 50\Omega, C_L = 0pF$           |     | -46 |     | dB   |

|------------------------------|--------------------------|---------------------------------------------------|-----|-----|-----|------|

| USB Switches Crosstalk       | ODV                      | 6 400MU- D 500 0 0 5                              |     | 47  |     | I.D. |

| (Channel-to-Channel)         | CKX <sub>USB</sub>       | f = 100MHz, $R_T$ = 50Ω, $C_L$ = 0pF              |     | -47 |     | dB   |

| USB Switch -3dB Bandwidth    | BW <sub>USB</sub>        | $R_T$ =50 $\Omega$ , $C_L$ =0pF Signal Power 0dBm |     | 1.4 |     | GHz  |

| DP_R, DN_L Ports Over-Vol    | tage Prote               | ection                                            |     |     |     |      |

| OVP Lockout Threshold        | $V_{\text{COM-OVP}}$     | Rising Edge                                       | 4.6 | 4.8 | 5.0 | V    |

| OVP Hysteresis               | V <sub>COM-HYS</sub>     |                                                   |     | 400 |     | mV   |

| GSBU1, GSBU2 Over-Voltage I  | Protection               |                                                   |     |     |     |      |

| OVP Lockout Threshold        | $V_{\text{SBU-OVP}}$     | Rising Edge                                       | 4.6 | 4.8 | 5.0 | V    |

| OVP Hysteresis               | V <sub>SBU-HYS</sub>     |                                                   |     | 400 |     | mV   |

| Audio Ground Switches ON     | RESISTAN                 | CE                                                |     |     |     |      |

| AGND-to-SBUx On-Resistance   | R <sub>AGND</sub>        | I <sub>AGND</sub> = 100 mA                        |     | 60  |     | mΩ   |

| MIC Switch                   |                          |                                                   |     |     |     |      |

| MIC Switch On-Resistance     | R <sub>MIC</sub>         | V <sub>IS</sub> = 0V~2.0V, I <sub>ON</sub> = 10mA |     | 2.1 |     | Ω    |

| MIC Switch RON Flatness      | R <sub>FLAT(MIC)</sub>   | V <sub>IS</sub> = 0V~2.0V, I <sub>ON</sub> = 10mA |     | 1   |     | Ω    |

| MIC Switch -3dB Bandwidth    | BW <sub>MIC</sub>        | R <sub>L</sub> =50Ω, GSBUx ties to SBUx           |     | 24  |     | MHz  |

| MIC Switch Off Isolation     | Off <sub>MIC</sub>       | $f = 100MHz, R_T = 50\Omega$                      |     | -48 |     | dB   |

| MIC Switch Turn-on Time      | t <sub>ON-M</sub>        | GSBUx = $2.0V R_L = 1k\Omega$                     |     | 200 |     | uS   |

| MIC Switch Turn-off Time     | t <sub>OFF-M</sub>       | GSBUx = $2.0V R_L=1k\Omega$                       |     | 2   |     | uS   |

| SENSE Switch                 |                          |                                                   |     | •   |     |      |

| SENSE Switch On-Resistance   | R <sub>SENSE</sub>       | V <sub>IS</sub> = 0V~50mV, I <sub>ON</sub> = 10mA |     | 0.4 |     | Ω    |

| SENSE Switch -3dB Bandwidth  | BW <sub>SENSE</sub>      | R <sub>L</sub> =50Ω, GSBUx ties to SBUx           |     | 21  |     | MHz  |

| SENSE Switch Off Isolation   | Offsense                 | $f = 100MHz, R_T = 50Ω$                           |     | -47 |     | dB   |

| SENSE Switch Turn-on Time    | t <sub>ON-S</sub>        | GSBUx = $50$ mV R <sub>L</sub> = $1$ k $\Omega$   |     | 200 |     | uS   |

| SENSE Switch Turn-off Time   | t <sub>OFF-S</sub>       | GSBUx = $50$ mV R <sub>L</sub> = $1$ k $\Omega$   |     | 2   |     | uS   |

| SBUx_H Switch                |                          |                                                   | •   |     |     |      |

| SBUx_H Switch On-Resistance  | R <sub>SBUx_H</sub>      | V <sub>IS</sub> = 0V~0.4V, I <sub>ON</sub> = 10mA |     | 7   |     | Ω    |

| SBUx_H Switch RON Flatness   | R <sub>FLAT(SBU_H)</sub> | V <sub>IS</sub> = 0V~3.3V, I <sub>ON</sub> = 10mA |     | 2   |     | Ω    |

| SBUx_H Switch -3dB Bandwidth | BW <sub>SBU_H</sub>      | R <sub>L</sub> =50Ω, GSBUx ties to SBUx           |     | 21  |     | MHz  |

| SBUx_H Switch Off Isolation  | Off <sub>SBU_H</sub>     | $f = 100MHz, R_T = 50Ω$                           |     | -51 |     | dB   |

#### **Table-4 Electrical Characteristics**

### Note:

- (1) Flatness is defined as the difference between maximum and minimum value of ON-resistance at the specified analog signal voltage points.

- (2) Ron matching between channels is calculated by subtracting the channel with the lowest max Ron value from the channel with the highest max Ron value.

- (3) Crosstalk is inversely proportional to source impedance

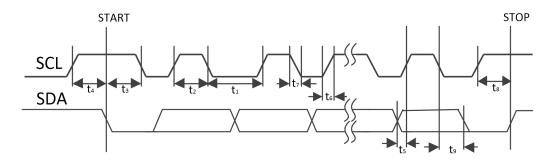

## **I2C Controlling:**

FSA4480UCX switching functions are controlled by 2 I2C pins: SCL and SDA pin. The timing characteristics and diagrams, as well as internal register meaning and usage are listed below:

## **I2C Timing Diagrams**

Fig.4 I2C Timing Diagrams

**Note:** Each of SDA and SCL pins should be pulled up by a  $2.2k\Omega$  resistor.

### **I2C Timing Characteristics**

## (Ta=25°C, VCC=3.3V, unless otherwise specified)

| Parameter                              | Symbol           | Conditions | Min. | Тур. | Max. | Unit |

|----------------------------------------|------------------|------------|------|------|------|------|

| SCL Frequency                          | f <sub>CLK</sub> |            |      |      | 400  | kHz  |

| SCL Low Pulse-Width                    | t <sub>1</sub>   |            | 1.3  |      |      | us   |

| SCL High Pulse-Width                   | t <sub>2</sub>   |            | 0.6  |      |      | us   |

| Hold Time (Start Condition)            | t <sub>3</sub>   |            | 0.6  |      |      | us   |

| Setup Time (Start Condition)           | t <sub>4</sub>   |            | 0.6  |      |      | us   |

| Data setup time                        | t <sub>5</sub>   |            | 0.1  |      |      | us   |

| SDA, SCL Rise Time                     | t <sub>6</sub>   |            |      |      | 0.3  | us   |

| SDA, SCL Fall Time                     | t <sub>7</sub>   |            |      |      | 0.3  | us   |

| Setup Time (Stop Condition)            | t <sub>8</sub>   |            | 0.6  |      |      | us   |

| Data Hold Time                         | t <sub>9</sub>   |            |      |      | 0.9  | us   |

| Pulse Width of Spikes being Suppressed | t <sub>ps</sub>  |            |      |      | 5    | ns   |

**Table-5 I2C Timing Characteristics**

## **I2C Slave Address**

| ADDR   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| ADDR=L | 1     | 0     | 0     | 0     | 0     | 1     | 0     | R/W   |

| ADDR=H | 1     | 0     | 0     | 0     | 0     | 1     | 1     | R/W   |

**Table-6 I2C Slave Address**

## **Mode Register**

Address: 0x01

Reset Value: 8'b 0000\_0000

Type: Read/Write

|       | T Caa, v v i i c |      |                                                                    |

|-------|------------------|------|--------------------------------------------------------------------|

| Bits  | Name             | Size | Description                                                        |

| [7:3] | Reserved         | 5    | Do Not Use                                                         |

|       |                  |      | 000: DN_L to DN switch ON, DP_R to DP switch ON                    |

|       |                  |      | SBU1 to SBU1_H switch ON, SBU2 to SBU2_H switch ON                 |

|       |                  |      | 001: DN_L to DN switch ON, DP_R to DP switch ON                    |

|       |                  |      | SBU1 to SBU2_H switch ON, SBU2 to SBU1_H switch ON                 |

|       | Switch           |      | 010: DN_L to L switch ON, DP_R to R switch ON, AGND2 to SBU2       |

| [2:0] | Mode             | 3    | switch ON MIC to GSBU1 switch ON, SENSE to GSBU2 switch ON         |

|       |                  |      | 011: DN_L to L switch ON, DP_R to R switch ON,AGND1 to SBU1 switch |

|       |                  |      | ON MIC to GSBU2 switch ON, SENSE to GSBU1 switch ON                |

|       |                  |      | 100: All switches OFF                                              |

|       |                  |      | 101: All switches OFF                                              |

|       |                  |      | 110: All switches OFF                                              |

|       |                  |      | 111: AGND1 to SBU1 switch ON, AGND2 to SBU2 switch ON              |

**Table-7 Mode Register**

# Manual and Interrupt Register

Address: 0x02

Reset Value: 8'b 0000\_0000

Type: Read/Write

| Bits  | Name     | Size | Description                                                   |  |  |

|-------|----------|------|---------------------------------------------------------------|--|--|

| [7:2] | Reserved | 6    | o Not Use                                                     |  |  |

| 1     | Manual   | 1    | 0: Switch Status is controlled by Mode Register 0x01          |  |  |

|       |          |      | 1: Switch Status is controlled by 3-bit GPIO (ENN, ADDR, INT) |  |  |

| 0     | INTC     | 1    | 0: Enable interrupt feature                                   |  |  |

|       |          |      | 1: Disable interrupt feature                                  |  |  |

**Table-8 Manual and Interrupt Register**

## **DET Direction Register**

Address: 0x03

Reset Value: 8'b 0000\_0000

Type: Read/Write

| Bits  | Name     | Size | Description                                                       |

|-------|----------|------|-------------------------------------------------------------------|

| [7:1] | Reserved | 7    | Do Not Use                                                        |

| 0     | DET      | 1    | 0: DET goes high when CC_IN <1.2v , DET goes low when CC_IN >1.5v |

|       |          |      | 1: DET goes low when CC_IN <1.2v , DET goes high when CC_IN >1.5v |

**Table-9 DET Direction Register**

## **DET Register**

Address: 0x04

Reset Value: 8'b 0000\_0000

Type: Read/Write

| Bits  | Name     | Size | Description                                                   |

|-------|----------|------|---------------------------------------------------------------|

| [7:1] | Reserved | 7    | Do Not Use                                                    |

| 0     | DET      | 1    | 0: DET Direction is controlled by DET Direction Register 0x03 |

|       |          |      | 1: DET remains high, independent of CC_IN                     |

**Table-10 DET Register**

#### **Manual Mode Control**

The function is active during control Register 0x02 bit[1] = 1. It will provide manual control for device. During this configuration, ADDR and INT pins will be set as logic control input

| vcc | ENN | ADDR | INT | SENSE             | USB        | Audio     | MIC/GND       | SBU            |

|-----|-----|------|-----|-------------------|------------|-----------|---------------|----------------|

|     |     |      |     | switch            | switch     | switch    | switch        | switch         |

| OFF | X   | X    | X   | OFF               | OFF        | OFF       | SBU1 to AGND1 | OFF            |

|     |     |      |     |                   |            |           | SBU2 to AGND2 |                |

| ON  | H   | X    | X   | OFF               | OFF        | OFF       | OFF           | OFF            |

| ON  | ٦   | L    | L   | OFF               | DP_R to DP | OFF       | OFF           | SBU1 to SBU1_H |

|     |     |      |     |                   | DN_L to DN |           |               | SBU2 to SBU2_H |

| ON  | L   | L    | Н   | OFF               | DP_R to DP | OFF       | OFF           | SBU1 to SBU2_H |

|     |     |      |     |                   | DN_L to DN |           |               | SBU2 to SBU1_H |

| ON  | L   | Н    | L   | SENSE to<br>GSBU2 | OFF        | DP_R to R | MIC to GSBU1  | OFF            |

|     |     |      |     |                   |            | DN_L to L | SBU2 to AGND2 |                |

| ON  | L   | Н    | Н   | SENSE to<br>GSBU1 | OFF        | DP_R to R | MIC to GSBU2  | OFF            |

|     |     |      |     |                   |            | DN_L to L | SBU1 to AGND1 |                |

| ON  | Н   | L    | L   | OFF               | OFF        | OFF       | OFF           | OFF            |

| ON  | Н   | L    | Н   | OFF               | OFF        | OFF       | OFF           | OFF            |

| ON  | Н   | Н    | L   | OFF               | OFF        | OFF       | OFF           | OFF            |

| ON  | Н   | Н    | Н   | OFF               | OFF        | OFF       | SBU1 to AGND1 | OFF            |

|     |     |      |     |                   |            |           | SBU2 to AGND2 |                |

**Table-11 Manual Mode Control**

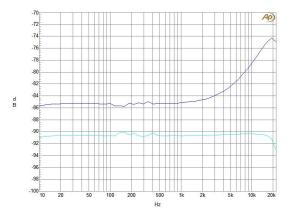

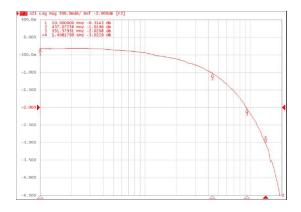

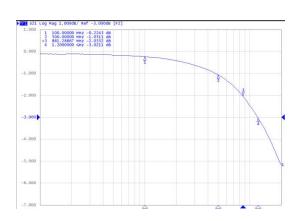

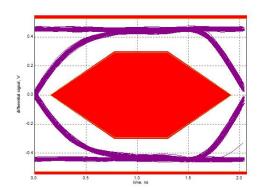

### Typical Performance Curves (Ta=25°C, VCC=3.3V, CAP=0.1uF, unless otherwise noted)

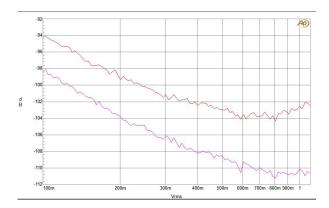

Fig.5 wi/wo A-Weighted Audio Switch THD+N vs Signal Swing @RL=32 $\Omega$  f=100Hz

Fig.6 wi/wo A-Weighted Audio Switch THD+N vs Frequency @RL=32 $\Omega$  Vs=0.7Vrms

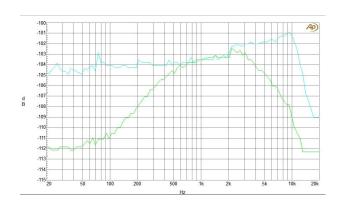

Fig.7 wi/wo A-Weighted Audio Switch THD+N vs Signal Swing @RL=1KΩ f=100Hz

Fig.8 wi/wo A-Weighted Audio Switch THD+N vs Frequency @RL=1KΩ Vs=2.3Vrms

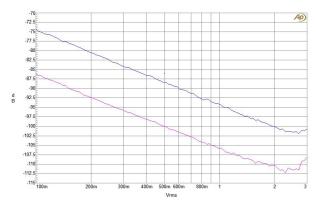

Fig.9 Audio Switch OFF-Isolation vs Frequency @RL=32 $\Omega$ /1K $\Omega$  Vs=0.3Vrms

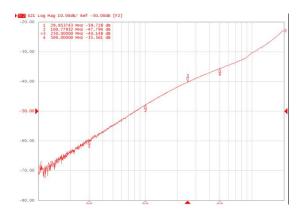

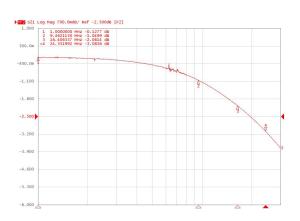

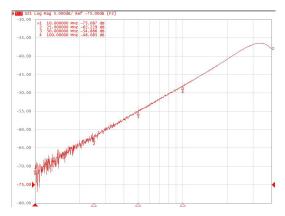

Fig.10 USB Switch Bandwidth

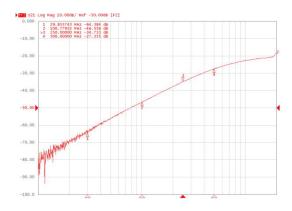

Fig.11 AUDIO Switch Bandwidth

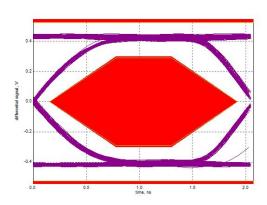

Fig.12 USB2.0 Eye Diagram of Signal Path without Switch

Fig.13 USB2.0 Eye Diagram of Signal Path with FSA4480UCX

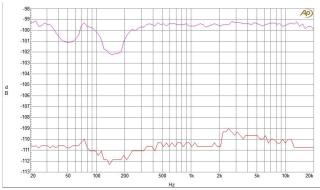

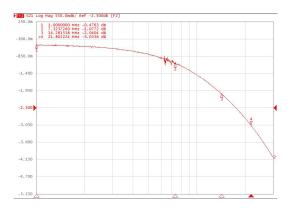

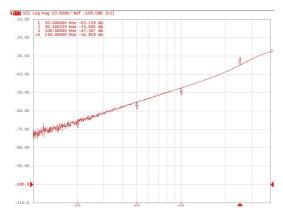

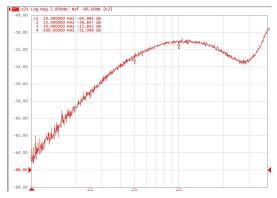

Fig.14 USB Switches Channel-to-Channel Crosstalk

Fig.15 USB Switch OFF-Isolation

Fig.16 SBUx-to-SBUx\_H Switch Insertion Loss

Fig.17 GSBUx-to-MIC Switch Insertion Loss

Fig.18 MIC Switch OFF Isolation

Fig.19 SENSE Switch OFF Isolation

Fig.20 SBUx\_H Switch OFF Isolation

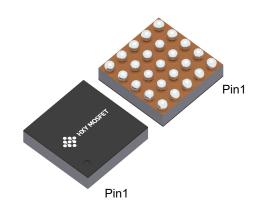

## **Package Outline Dimensions**

## **CSP-25**

Fig.21 Package Outline Dimensions

| Cumb al | Dimensions In Millimeter |       |       |  |  |

|---------|--------------------------|-------|-------|--|--|

| Symbol  | Min.                     | Тур.  | Max.  |  |  |

| X       | 2.01                     | 2.04  | 2.07  |  |  |

| Υ       | 2.01                     | 2.04  | 2.07  |  |  |

| X1      |                          | 0.18  |       |  |  |

| X2      |                          | 0.40  |       |  |  |

| X3      | 0.175                    | 0.205 | 0.235 |  |  |

| Y1      |                          | 0.18  |       |  |  |

| Y2      |                          | 0.40  |       |  |  |

| Z       | 0.550                    | 0.600 | 0.650 |  |  |

| Z1      | 0.145                    | 0.170 | 0.195 |  |  |

| Z2      | 0.340                    | 0.365 | 0.390 |  |  |

| Z3      | 0.395                    | 0.040 | 0.045 |  |  |

**Table-12 Package Outline Dimensions**

#### **Attention**

- Any and all HUA XUAN YANG ELECTRONICS products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your HUA XUAN YANG ELECTRONICS representative nearest you before using any HUA XUAN YANG ELECTRONICS products described or contained herein in such applications.

- HUA XUAN YANG ELECTRONICS assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein.

- Specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- HUA XUAN YANG ELECTRONICS CO.,LTD. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all HUA XUAN YANG ELECTRONICS products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of HUA XUAN YANG ELECTRONICS CO.,LTD.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

HUA XUAN YANG ELECTRONICS believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the HUA XUAN YANG ELECTRONICS product that you intend to use.