# **SECTION 6 ELECTRICAL CHARACTERISTICS**

The AC specifications presented consist of output delays, input setup and hold times, and signal skew times. All signals are specified relative to an appropriate edge of the clock (CL-KO pin) and possibly to one or more other signals.

### **6.1 MAXIMUM RATINGS**

| Rating                                             | Symbol           | Value                 | Unit |

|----------------------------------------------------|------------------|-----------------------|------|

| Supply Voltage                                     | V <sub>DD</sub>  | - 0.3 to + 7.0        | ٧    |

| Input Voltage                                      | V <sub>in</sub>  | - 0.3 to + 7.0        | ٧    |

| Operating Temperature Range<br>MC68302<br>MC68302C | T <sub>A</sub>   | 0 to 70<br>- 40 to 85 | °C   |

| Storage Temperature Range                          | T <sub>stg</sub> | - 55 to + 150         | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to his high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or VDD)

### **6.2 THERMAL CHARACTERISTICS**

| Characteristic                  | Symbol          | Value | Unit |

|---------------------------------|-----------------|-------|------|

| The small Projectors of the DCA | θ <sub>JA</sub> | 25    | °C/W |

| Thermal Resistance for PGA      | θ <sub>JC</sub> | 2     | °C/W |

| Th                              | θја             | 40    | °C/W |

| Thermal Resistance for CQFP     | θ <sub>JC</sub> | 15    | °C/W |

| The small Projector on for POED | $\theta_{JA}$   | 42    | °C/W |

| Thermal Resistance for PQFP     | θ <sub>JC</sub> | 20    | °C/W |

$$T_J = T_A + (P_D \cdot A)$$

$$P_D = (V_{DD} \cdot I_{DD}) + P_{I/O}$$

P<sub>I/O</sub> is the power dissipation on pins.

For  $T_A = 70$ °C and  $P_{I/O} + 0$  W, 16.67 MHz, 5.5 V, and CQFP

package, the worst case value of T<sub>J</sub> is:

$T_J = 70^{\circ}\text{C} + (5.5 \text{ V} \cdot 30 \text{ mA} \cdot 40^{\circ}\text{C/W}) = 98.65\text{C}$

### **6.3 POWER CONSIDERATIONS**

The average chip-junction temperature, T.I. in °C can be obtained from:

$$T_{.1} = T_A + (P_D \bullet \theta_{.1A})(1)$$

where:

T<sub>A</sub> = Ambient Temperature, °C

θ.IA = Package Thermal Resistance, Junction to Ambient, °C/W

$P_D = P_{INT} + P_{I/O}$

P<sub>INT</sub> = I<sub>DD</sub> x V<sub>DD</sub>. Watts—Chip Internal Power

P<sub>1/O</sub> = Power Dissipation on Input and Output Pins—User Determined

For most applications  $P_{I/O} < 0.3 \bullet P_{INT}$  and can be neglected.

If  $P_{I/O}$  is neglected, an approximate relationship between  $P_D$  and  $T_J$  is

$$P_D = K \div (T_J + 273^{\circ}C)(2)$$

Solving equations (1) and (2) for K gives:

$$K = P_D \bullet (T_A + 273^{\circ}C) + \theta_{JA} \bullet P_D^2(3)$$

6

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $P_D$  and  $P_D$  are obtained by solving equations (1) and (2) iteratively for any value of  $P_D$ .

### **6.4 POWER DISSIPATION**

| Characteristic                                             | Symbol | Тур | Max | Unit |

|------------------------------------------------------------|--------|-----|-----|------|

| Power Dissipation at 25 MHz- Rev C.8μ (see Notes 1 & 2)    | PD     | 85  | 130 | mA   |

| Power Dissipation at 25 MHz -Rev C.65μ (see Notes 1 & 2)   | PD     | 65  | 90  | mA   |

| Power Dissipation at 20 MHz-Rev C.8μ (see Notes 1 & 2)     | PD     | 65  | 100 | mA   |

| Power Dissipation at 20 MHz-Rev C.65μ (see Notes 1 & 2)    | PD     | 50  | 80  | mA   |

| Power Dissipation at 16.67 MHz-Rev C.8μ (see Notes 1 & 2)  | PD     | 54  | 85  | mA   |

| Power Dissipation at 16.67 MHz-Rev C.65μ (see Notes 1 & 2) | PD     | 44  | 70  | mA   |

| Power Dissipation at 4 MHz-Rev C.8µ (see Notes 1,2 & 3)    | PD     | 40  | -   | mA   |

| Power Dissipation at 4 MHz-Rev C.65μ (see Notes 1, 2 & 3)  | PD     | 27  | -   | mA   |

| Power Dissipation at 3.3V 20 MHz-Rev C.65µ (see Note 2)    | PD     | 30  | 60  | mA   |

| Power Dissipation at 3.3V 16.67 MHz-Rev C.65µ (see Note 2) | PD     | 25  | 50  | mA   |

- 1. Values measured with maximum loading of 130 pF on all output pins. Typical means 5.0 V at 25°C. Maximum means guaranteed maximum over maximum temperature (85°C) and voltage (5.5 V).

- 2. The IMP is tested with the M68000 core executing, all three baud rate generators enabled and clocking at a rate of 64 kHz, and the two general-purpose timers running with a prescaler of 256. Power measurements are not significantly impacted by baud rate generators or timers until their clocking frequency becomes a much more sizable fraction of the system frequency than in these test conditions.

- 3. The M68000 core will not operate at 4 MHz. This is only for low power mode.

## **6.5 DC ELECTRICAL CHARACTERISTICS**

|                                                                                                          | Characteristic                                                                                                                                                                                                                                          | Symbol                                                   | Min                   | Max                     | Unit                 |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|-------------------------|----------------------|

| Input High Voltage                                                                                       | (Except EXTAL)                                                                                                                                                                                                                                          | V <sub>IH</sub>                                          | 2.0                   | V <sub>DD</sub>         | V                    |

| Input Low Voltage                                                                                        | (Except EXTAL)                                                                                                                                                                                                                                          | V <sub>IL</sub>                                          | V <sub>SS</sub> - 0.3 | 0.8                     | V                    |

| Input High Voltage                                                                                       | (EXTAL)                                                                                                                                                                                                                                                 | V <sub>CIH</sub>                                         | 4.0                   | VDD                     | V                    |

| Input Low Voltage                                                                                        | (EXTAL)                                                                                                                                                                                                                                                 | V <sub>CIL</sub>                                         | V <sub>SS</sub> - 0.3 | 0.6                     | ٧                    |

| Input Leakage Cu                                                                                         | rrent                                                                                                                                                                                                                                                   | II <sub>N</sub>                                          | _                     | 20                      | μА                   |

| Input Capacitance                                                                                        | All Pins                                                                                                                                                                                                                                                | CiN                                                      | _                     | 15                      | ρF                   |

| Three-State Leaka                                                                                        | age Current (2.4/0.5 V)                                                                                                                                                                                                                                 | I <sub>TSI</sub>                                         | _                     | 20                      | μА                   |

| Open Drain Leaka                                                                                         | ge Current (2.4 V)                                                                                                                                                                                                                                      | l <sub>OD</sub>                                          | _                     | 20                      | μА                   |

| Output High Volta                                                                                        | ge (I <sub>OH</sub> = 400 μA) (see Note)                                                                                                                                                                                                                | V <sub>OH</sub>                                          | V <sub>DD</sub> -1.0  |                         | V                    |

| Output Low Voltage ( $I_{OL} = 3.2 \text{ mA}$ ) $(I_{OL} = 5.3 \text{ mA})$ $(I_{OL} = 7.0 \text{ mA})$ | A1-A23, PB0-PB11, FC0-FC2, CS0-CS3  IAC, AVEC, BG, RCLK1, RCLK2, RCLK3, TCLK1, TCLK2, TCLK3, RTS1, RTS2, RTS3, SDS2, PA12, RXD2, RXD3, CTS2, CD2, CD3 DREQ, BRG1 AS, UDS, LDS, R/W, BERR BGACK, BCLR, DTACK, DACK, RMC, D0-D15, RESET  TXD1, TXD2, TXD3 | V <sub>OL</sub>                                          | _                     | 0.5<br>0.5              | V                    |

| $(I_{OL} = 8.9 \text{ mA})$<br>$(I_{OL} = 3.2 \text{ mA})$                                               | DONE, HALT, BR (as output) CLKO                                                                                                                                                                                                                         |                                                          | _<br>_                | 0.5<br>0.4              |                      |

| Output Drive CLK<br>Output Drive ISDN<br>Output Drive All C                                              | I I/F (GCI Mode)                                                                                                                                                                                                                                        | O <sub>CLK</sub><br>O <sub>GCI</sub><br>O <sub>ALL</sub> | <u>-</u>              | 50<br>150<br>130        | pF<br>pF<br>pF       |

| Output Drive Dera<br>Output Drive Dera                                                                   | ting Factor for CLKO of 0.030 ns/pF<br>ting Factor for CLKO of 0.035 ns/pF<br>ting Factor for All Other Pins 0.035 ns/pF<br>ting Factor for All Other Pins 0.055 ns/pF                                                                                  | O <sub>KF</sub> O <sub>KF</sub> O <sub>KF</sub>          | 20<br>50<br>20<br>130 | 50<br>130<br>130<br>220 | pF<br>pF<br>pF<br>pF |

| Power                                                                                                    |                                                                                                                                                                                                                                                         | V <sub>DD</sub>                                          | 4.5                   | 5.5                     | V                    |

| Common                                                                                                   |                                                                                                                                                                                                                                                         | V <sub>SS</sub>                                          | 0                     | 0                       | V                    |

NOTE: The maximum  $I_{OH}$  for a given pin is one-half the  $I_{OL}$  rating for that pin. For an  $I_{OH}$  between 400  $\mu$ A and  $I_{OL}/2$  mA, the minimum  $V_{OH}$  is calculated as:  $V_{DD}$  - (1 +.05 V/mA( $I_{OH}$  -.400 mA)). NOTE: All AC specs are assume an output load of 130pf (except for CLKO).

### 6.6 DC ELECTRICAL CHARACTERISTICS—NMSI1 IN IDL MODE

| Characteristic            | Symbol          | Min                   | Max                   | Unit | Condition                         |

|---------------------------|-----------------|-----------------------|-----------------------|------|-----------------------------------|

| Inp                       | ut Pin Characte | ristics: L1CLK, L     | .1SY1, L1RXD, L       | IGR  |                                   |

| Input Low Level Voltage   | V <sub>IL</sub> | -10%                  | + 20%                 | ٧    | (% of V <sub>DD</sub> )           |

| Input High Level Voltage  | V <sub>IH</sub> | V <sub>DD</sub> - 20% | V <sub>DD</sub> + 10% | ٧    |                                   |

| Input Low Level Current   | IIL             | _                     | ± 10                  | μА   | $V_{in} = V_{ss}$                 |

| Input High Level Current  | IIH             | _                     | ± 10                  | μА   | V <sub>in</sub> = V <sub>DD</sub> |

| Ou                        | tput Pin Charac | teristics: L1TXD      | , SDS1- SDS2, L1      | IRQ  |                                   |

| Output Low Level Voltage  | V <sub>OL</sub> | 0                     | 1.0                   | ٧    | I <sub>OL</sub> = 5.0 mA          |

| Output High Level Voltage | V <sub>OH</sub> | V <sub>DD</sub> - 1.0 | V <sub>DD</sub>       | V    | I <sub>OH</sub> = 400 μA          |

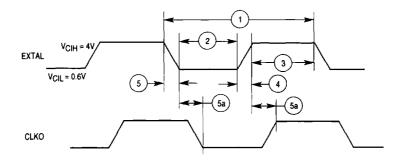

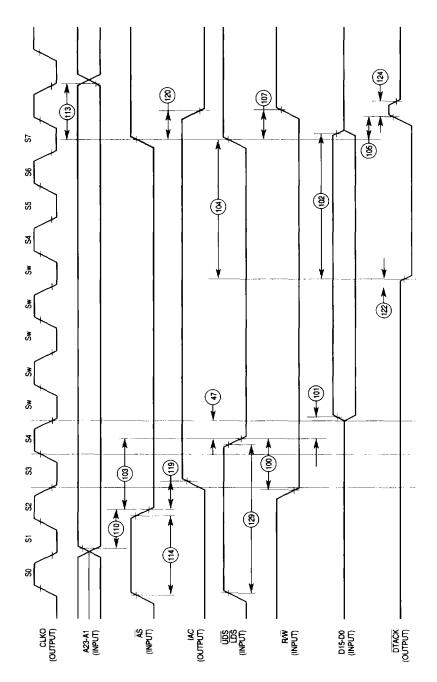

### 6.7 AC ELECTRICAL SPECIFICATIONS—CLOCK TIMING

(see Figure 6-1, Figure 6-2, Figure 6-3, and Figure 6-4)

|      |                                         |                                   | 16.67 MHz |       | 20 MHz |      | 25 MHz |      |      |  |

|------|-----------------------------------------|-----------------------------------|-----------|-------|--------|------|--------|------|------|--|

| Num. | Characteristic                          | Symbol                            | Min       | Max   | Min    | Max  | Min    | Max  | Unit |  |

|      | Frequency of Operation                  | f                                 | 8         | 16.67 | 8      | 20   | 8      | 25   | MHz  |  |

| 1    | Clock Period (EXTAL) (See note 3)       | t <sub>cyc</sub>                  | 60        | 125   | 50     | 125  | 40     | 125  | ns   |  |

| 2, 3 | Clock Pulse Width (EXTAL)               | t <sub>CL</sub> , t <sub>CH</sub> | 25        | 62.5  | 21     | 62.5 | 16     | 62.5 | ns   |  |

| 4, 5 | Clock Rise and Fall Times (EXTAL)       | t <sub>Cr</sub> , t <sub>Cf</sub> | -         | 5     | _      | 4    | _      | 4    | ns   |  |

| 5a   | EXTAL to CLKO Delay (See Notes 1 and 2) | t <sub>CD</sub>                   | 2         | 11    | 2      | 9    | 2      | 7    | ns   |  |

- 1. CLKO loading is 50 pF max.

- CLKO skew from the rising and falling edges of EXTAL will not differ from each other by more than 1 ns, if the EXTAL rise time equals the EXTAL fall time.

- 3. You may not stop the clock input at any time.

Figure 6-1. Clock Timing Diagram

# D

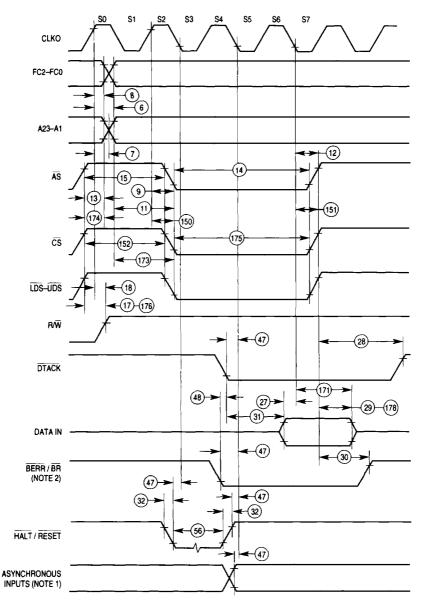

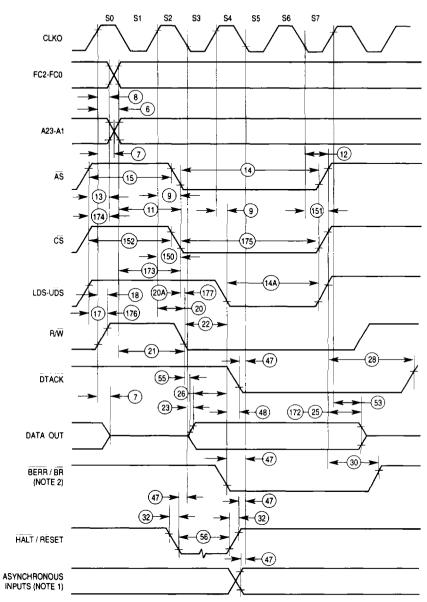

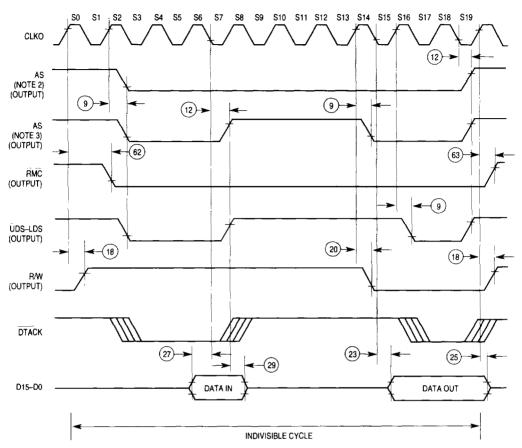

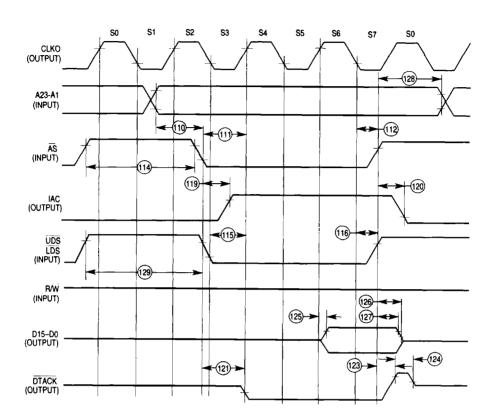

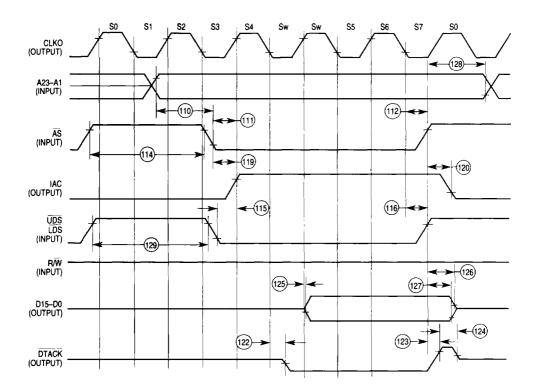

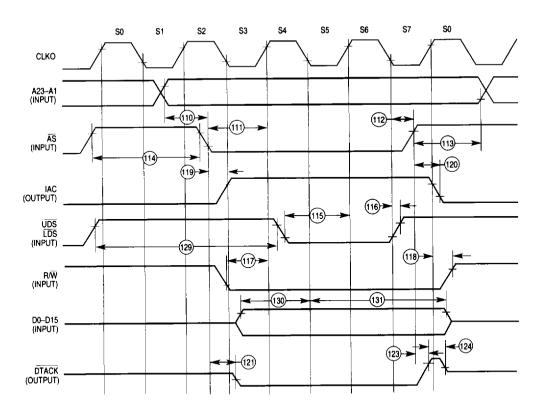

## 6.8 AC ELECTRICAL SPECIFICATIONS—IMP BUS MASTER CYCLES

(see Figure 6-2, Figure 6-3, Figure 6-4, and Figure 6-5))

|      |                                                                                             |                                     | 16.67 | MHz | 20  | ИНZ | 25 I | MHz |      |

|------|---------------------------------------------------------------------------------------------|-------------------------------------|-------|-----|-----|-----|------|-----|------|

| Num. | Characteristic                                                                              | Symbol                              | Min   | Max | Min | Max | Min  | Max | Unit |

| 6    | Clock High to FC, Address Valid                                                             | t <sub>CHFCADV</sub>                | 0     | 45  | 0   | 40  | 0    | 30  | ns   |

| 7    | Clock High to Address, Data Bus High Impedance (Maximum)                                    | t <sub>CHADZ</sub>                  | _     | 50  | -   | 42  | _    | 33  | ns   |

| 8    | Clock High to Address, FC Invalid (Minimum)                                                 | t <sub>CHAFI</sub>                  | 0     |     | 0   | _   | 0    | _   | ns   |

| 9    | Clock High to AS, DS Asserted (see Note 1)                                                  | t <sub>CHSL</sub>                   | 3     | 30  | 3   | 25  | 3    | 20  | ns   |

| 11   | Address, FC Valid to AS, DS Asserted (Read) AS Asserted Write (see Note 2)                  | †AFCVSL                             | 15    | _   | 12  | _   | 10   | _   | ns   |

| 12   | Clock Low to AS, DS Negated (see Note 1)                                                    | t <sub>CLSH</sub>                   | _     | 30  | _   | 25  | _    | 20  | ns   |

| 13   | $\overline{\text{AS}}$ , $\overline{\text{DS}}$ Negated to Address, FC Invalid (see Note 2) | t <sub>SHAFI</sub>                  | 15    | _   | 12  | _   | 10   | _   | ns   |

| 14   | AS (and DS Read) Width Asserted (see Note 2)                                                | t <sub>SL</sub>                     | 120   |     | 100 |     | 80   |     | ns   |

| 14A  | DS Width Asserted, Write (see Note 2)                                                       | t <sub>DSL</sub>                    | 60    |     | 50  |     | 40   |     | ns   |

| 15   | AS, DS Width Negated (see Note 2)                                                           | t <sub>SH</sub>                     | 60    |     | 50  | _   | 40   |     | ns   |

| 16   | Clock High to Control Bus High Impedance                                                    | t <sub>CHCZ</sub>                   | _     | 50  | 1   | 42  | _    | 33  | ns   |

| 17   | AS, DS Negated to R/W Invalid (see Note 2)                                                  | t <sub>SHRH</sub>                   | 15    |     | 12  |     | 10   | _   | ns   |

| 18   | Clock High to R/W High (see Note 1)                                                         | tCHRH                               | _     | 30  |     | 25  |      | 20  | ns   |

| 20   | Clock High to R/W Low (see Note 1)                                                          | t <sub>CHRL</sub>                   | _     | 30  |     | 25  |      | 20  | ns   |

| 20A  | AS Asserted to R/W Low (Write) (see Notes 2 and 6)                                          | †ASRV                               | _     | 10  |     | 10  | -    | 7   | ns   |

| 21   | Address FC Valid to R/W Low (Write) (see Note 2)                                            | tAFCVRL                             | 15    | _   | 12  | _   | 10   | _   | ns   |

| 22   | R/W Low to DS Asserted (Write) (see Note 2)                                                 | t <sub>RLSL</sub>                   | 30    | _   | 25  | _   | 20   | _   | ns   |

| 23   | Clock Low to Data-Out Valid                                                                 | tcldo                               |       | 30  |     | 25  |      | 20  | ns   |

| 25   | AS, DS, Negated to Data-Out Invalid (Write) (see Note 2)                                    | t <sub>SHDOI</sub>                  | 15    | _   | 12  | _   | 10   | _   | ns   |

| 26   | Data-Out Valid to DS Asserted (Write) (see Note 2)                                          | tDOSL                               | 15    | _   | 12  | _   | 10   | _   | ns   |

| 27   | Data-In Valid to Clock Low (Setup Time on Read) (see Note 5)                                | t <sub>DICL</sub>                   | 7     |     | 6   | _   | 5    | _   | ns   |

| 28   | AS, DS Negated to DTACK Negated (Asynchronous Hold) (see Note 2)                            | <sup>†</sup> SHDAH                  | 0     | 110 | 0   | 95  | 0    | 75  | ns   |

| 29   | AS, DS Negated to Data-In Invalid (Hold Time on Read)                                       | t <sub>SHDII</sub>                  | 0     | _   | 0 . | _   | 0    | _   | ns   |

| 30   | AS, DS Negated to BERR Negated                                                              | tshbeh                              | 0     |     | 0   | _   | 0    |     | ns   |

| 31   | DTACK Asserted to Data-In Valid (Setup Time) (see Notes 2 and 5)                            | †DALDI                              | _     | 50  |     | 42  | _    | 33  | ns   |

| 32   | HALT and RESET Input Transition Time                                                        | t <sub>HHr</sub> , t <sub>HHf</sub> | _     | 150 |     | 150 | -    | 150 | ns   |

| 33   | Clock High to BG Asserted                                                                   | t <sub>CHGL</sub>                   |       | 30  |     | 25  | _    | 20  | ns   |

| 34   | Clock High to BG Negated                                                                    | t <sub>CHGH</sub>                   | _     | 30  |     | 25  |      | 20  | ns   |

| 35   | BR Asserted to BG Asserted (see Note 11)                                                    | t <sub>BRLGL</sub>                  | 2.5   | 4.5 | 2.5 | 4.5 | 2.5  | 4.5 | clks |

| 36   | BR Negated to BG Negated (see Note 7)                                                       | t <sub>BRHGH</sub>                  | 1.5   | 2.5 | 1.5 | 2.5 | 1.5  | 2.5 | ciks |

|             |                                                                          |                     | 16.67 | MHz | 20 I | MHz | 25  | VHz |             |

|-------------|--------------------------------------------------------------------------|---------------------|-------|-----|------|-----|-----|-----|-------------|

| Num.        | Characteristic                                                           | Symbol              | Min   | Max | Min  | Max | Min | Max | Unit        |

| 37          | BGACK Asserted to BG Negated                                             | <sup>t</sup> GALGH  | 2.5   | 4.5 | 2.5  | 4.5 | 2.5 | 4.5 | clks        |

| 37A         | BGACK Asserted to BR Negated (see Note 8)                                | t <sub>GALBRH</sub> | 10    | 1.5 | 10   | 1.5 | 10  | 1.5 | ns/<br>clks |

| 38          | BG Asserted to Control, Address, Data Bus<br>High Impedance (AS Negated) | t <sub>GLZ</sub>    | _     | 50  | _    | 42  |     | 33  | ns          |

| 39          | BG Width Negated                                                         | t <sub>GH</sub>     | 1.5   | _   | 1.5  | _   | 1.5 |     | clks        |

| 40          | BGACK Asserted to Address Valid                                          | tGALAV              | 15    | _   | 15   | _   | 15  |     | ns          |

| 41          | BGACK Asserted to AS Asserted                                            | t <sub>GALASA</sub> | 30    | _   | 30   |     | 20  |     | ns          |

| 44          | AS, DS Negated to AVEC Negated                                           | tshvph              | 0     | 50  | 0    | 42  | 0   | 33  | ns          |

| 46          | BGACK Width Low                                                          | t <sub>GAL</sub>    | 1.5   | _   | 1.5  |     | 1.5 | _   | clks        |

| 47          | Asynchronous Input Setup Time (see Note 5)                               | t <sub>ASI</sub>    | 10    | _   | 10   | _   | 7   | _   | ns          |

| 48          | BERR Asserted to DTACK Asserted (see Notes 2 and 3)                      | t <sub>BELDAL</sub> | 10    | _   | 10   | _   | 7   | _   | ns          |

| 53          | Data-Out Hold from Clock High                                            | t <sub>CHDOI</sub>  | 0     |     | 0    |     | 0   | _   | ns          |

| 55          | R/W Asserted to Data Bus Impedance<br>Change                             | t <sub>ALDBD</sub>  | 0     | _   | 0    | _   | 0   | _   | ns          |

| 56          | HALT/RESET Pulse Width (see Note 4)                                      | t <sub>HRPW</sub>   | 10    |     | 10   | _   | 10  |     | clks        |

| 57          | BGACK Negated to AS, DS, R/W Driven                                      | t <sub>GASD</sub>   | 1.5   | 1   | 1.5  | _   | 1.5 | _   | clks        |

| 57 <b>A</b> | BGACK Negated to FC                                                      | t <sub>GAFD</sub>   | 1     |     | 1    | _   | 1   | _   | clks        |

| 58          | BR Negated to AS, DS, R/W Driven (see Note 7)                            | t <sub>RHSD</sub>   | 1.5   | 1   | 1.5  | _   | 1.5 | _   | clks        |

| 58A         | BR Negated to FC (see Note 7)                                            | t <sub>RHFD</sub>   | 1     | _   | 1    | _   | 1   | -   | clks        |

| 60          | Clock High to BCLR Asserted                                              | t <sub>CHBCL</sub>  | _     | 30  | _    | 25  | _   | 20  | ns          |

| 61          | Clock High to BCLR High Impedance (See Note 10)                          | <sup>t</sup> CHBCH  | _     | 30  | _    | 25  | _   | 20  | ns          |

| 62          | Clock Low (S0 Falling Edge during read) to RMC Asserted                  | <sup>t</sup> CLRML  | _     | 30  | _    | 25  | _   | 20  | ns          |

| 63          | Clock High (during write) to RMC Negated                                 | t <sub>CHRMH</sub>  |       | 30  |      | 25  |     | 20  | ns          |

| 64          | RMC Negated to BG Asserted (see Note 9)                                  | tRMHGL              | _     | 30  | _    | 25  | _   | 20  | ns          |

### NOTES:

- 1. For loading capacitance of less than or equal to 50 pF, subtract 4 ns from the value given in the maximum columns.

- Actual value depends on clock period since signals are driven/latched on different CLKO edges. To calculate the actual spec for other clock frequencies, the user may derive the formula for each specification. First, derive the margin factor as:

M = N(P/2) - Sa

where N is the number of one-half CLKO periods between the two events as derived from the timing diagram, P is the rated clock period of the device for which the specs were derived (e.g., 60 ns with a 16.67-MHz device or 50 ns with a 20 MHz device), and Sa is the actual spec in the data sheet. Thus, for spec 14 at 16.67 MHz:

M = 5(60 ns/2) - 120 ns = 30 ns.

Once the margin (M) is calculated for a given spec, a new value of that spec (Sn) at another clock frequency with period (Pa) is calculated as:

Sn = N(Pa/2) - M

Thus for spec 14 at 12.5 MHz:

Sn = 5(80 ns/2) - 30 ns = 170 ns.

These two formulas assume a 50% duty cycle. Otherwise, if N is odd, the previous values N(P/2) and N(Pa/2) must be reduced by X, where X is the difference between the nominal pulse width and the minimum pulse width of the EXTAL input clock for that duty cycle.

3. If #47 is satisfied for both DTACK and BERR, #48 may be ignored. In the absence of DTACK, BERR is a

- synchronous input using the asynchronous input setup time (#47).

- 4. For power-up, the MC68302 must be held in the reset state for 100 ms to allow stabilization of on-chip circuit. After the system is powered up #56 refers to the minimum pulse width required to reset the processor.

- 5. If the asynchronous input setup (#47) requirement is satisfied for DTACK, the DTACK asserted to data setup time (#31) requirement can be ignored. The data must only satisfy the data-in to clock low setup time (#27) for the following clock cycle.

- 6. When  $\overline{AS}$  and RW are equally loaded ( $\pm 20\%$ ), subtract 5 ns from the values given in these columns.

- 7. The MC68302 will negate  $\overline{BG}$  and begin driving the bus if external arbitration logic negates  $\overline{BR}$  before asserting

- 8. The minimum value must be met to guarantee proper operation. If the maximum value is exceeded, BG may be reasserted.

- 9. This specification is valid only when the RMCST bit is set in the SCR register.

- 10.Occurs on S0 of SDMA read/write access when the SDMA becomes bus master.

- 11. Specification may be exceeded during the TAS instruction if the RMCST bit in the SCR is set.

6

- Setup time for the asynchronous inputs IPL2-IPL0 guarantees their recognition at the next falling edge of the clock.

- 2. BR need fall at this time only to insure being recognized at the end of the bus cycle.

- 3. Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall is linear between 0.8 volts and 2.0 volts.

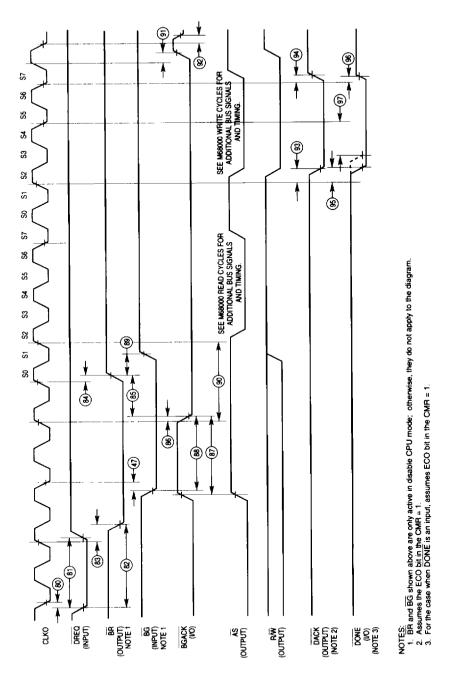

Figure 6-2. Read Cycle Timing Diagram

- Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall is <u>linear</u> between between 0.8 volt and 2.0 volts.

Because of loading variations, R/W may be valid after AS even though both are initiated by the rising edge

- of S2 (specification #20A)

- 3. Each wait state is a full clock cycle inserted between S4 and S5.

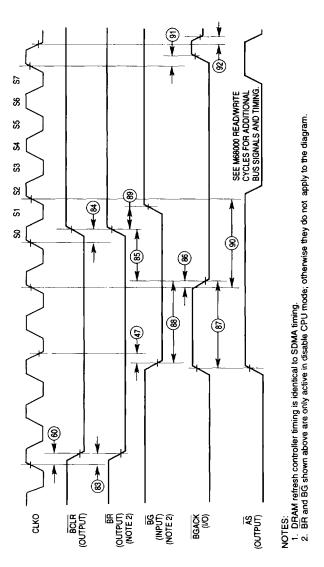

Figure 6-3. Write Cycle Timing Diagram

- 1. For other timings than RMC, see Figures 6-2 and 6-3.

- 2. RMCST = 0 in the SCR.

- 3. RMCST = 1 in the SCR.

- 4. Wait states may be inserted between S4 and S5 during the write cycle and between S16 and S17 during the read cycle.

- 5. Read-modify-write cycle is generated only by the TAS instruction.

Figure 6-4. Read-Modify-Write Cycle Timing Diagram

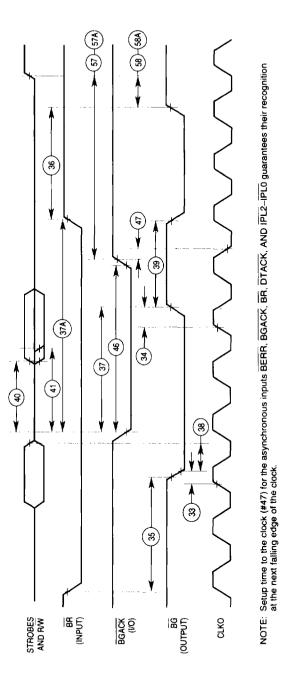

Figure 6-5. Bus Arbitration Timing Diagram

# 6.9 AC ELECTRICAL SPECIFICATIONS—DMA (see Figure 6-6 and Figure 6-7)

|      |                                                                       |                     | 16.6 | 7 MHz      | 20  | MHz        | 25  | MHz        | Γ          |

|------|-----------------------------------------------------------------------|---------------------|------|------------|-----|------------|-----|------------|------------|

| Num. | Characteristic                                                        | Symbol              | Min  | Max        | Min | Max        | Min | Max        | Unit       |

| 80   | DREQ Asynchronous Setup Time (see Note 1)                             | tREQASI             | 15   | _          | 15  |            | 10  | -          | ns         |

| 81   | DREQ Width Low (see Note 2)                                           | t <sub>REQL</sub>   | 2    | _          | 2   | _          | 2   |            | clks       |

| 82   | DREQ Low to BR Low (see Notes 3 and 4)                                | TREQLBRL            | _    | 2          | _   | 2          | _   | 2          | clks       |

| 83   | Clock High to BR Low (see Notes 3 and 4)                              | t <sub>CHBRL</sub>  | _    | 30         | _   | 25         |     | 20         | ns         |

| 84   | Clock High to BR High Impedance (see Notes 3 and 4)                   | t <sub>CHBRZ</sub>  | _    | 30         | _   | 25         | _   | 20         | ns         |

| 85   | BGACK Low to BR High Impedance (see Notes 3 and 4)                    | t <sub>BKLBRZ</sub> | 30   | _          | 25  | _          | 20  | _          | ns         |

| 86   | Clock High to BGACK Low                                               | t <sub>CHBKL</sub>  | _    | 30         | _   | 25         |     | 20         | ns         |

| 87   | AS and BGACK High (the Latest One) to BGACK Low (when BG Is Asserted) | † <sub>ABHBKL</sub> | 1.5  | 2.5<br>+30 | 1.5 | 2.5<br>+25 | 1.5 | 2.5<br>+20 | clks<br>ns |

| 88   | BG Low to BGACK Low (No Other Bus<br>Master) (see Notes 3 and 4)      | t <sub>BGLBKL</sub> | 1.5  | 2.5<br>+30 | 1.5 | 2.5<br>+25 | 1.5 | 2.5<br>+20 | clks<br>ns |

| 89   | BR High Impedance to BG High (see Notes 3 and 4)                      | t <sub>BRHBGH</sub> | 0    | _          | 0   | _          | 0   | _          | ns         |

| 90   | Clock on which BGACK Low to Clock on which AS Low                     | †CLBKLAL            | 2    | 2          | 2   | 2          | 2   | 2          | clks       |

| 91   | Clock High to BGACK High                                              | tснвкн              |      | 30         |     | 25         |     | 20         | ns         |

| 92   | Clock Low to BGACK High Impedance                                     | t <sub>CLBKZ</sub>  |      | 15         | _   | 15         | _   | 10         | ns         |

| 93   | Clock High to DACK Low                                                | <sup>†</sup> CHACKL | _    | 30         |     | 25         | _   | 20         | ns         |

| 94   | Clock Low to DACK High                                                | <sup>t</sup> CLACKH |      | 30         | _   | 25         | _   | 20         | ns         |

| 95   | Clock High to DONE Low (Output)                                       | tCHDNL              |      | 30         |     | 25         |     | 20         | ns         |

| 96   | Clock Low to DONE High Impedance                                      | t <sub>CLDNZ</sub>  | _    | 30         |     | 25         | _   | 20         | ns         |

| 97   | DONE Input Low to Clock Low (Asynchronous Setup)                      | † <sub>DNLTCH</sub> | 15   | _          | 15  | _          | 10  | _          | ns         |

- 1. DREQ is sampled on the falling edge of CLK in cycle steal and burst modes.

- 2. If #80 is satisfied for DREQ, #81 may be ignored.

- 3. BR will not be asserted while BG, HALT, or BERR is asserted.

- 4. Specifications are for DISABLE CPU mode only.

- 5. DREQ, DACK, and DONE do not apply to the SDMA channels.

- 6. DMA and SDMA read and write cycle timing is the same as that for the M68000 core.

Figure 6-6. DMA Timing Diagram (IDMA)

Figure 6-7. DMA Timing Diagram (SDMA)

6

# 6.10 AC ELECTRICAL SPECIFICATIONS—EXTERNAL MASTER INTERNAL ASYNCHRONOUS READ/WRITE CYCLES

(see Figure 6-8 and Figure 6-9)

|      |                                          |                     | 16.67 | MHz | 20 1 | MHz | 25 I | MHz |      |

|------|------------------------------------------|---------------------|-------|-----|------|-----|------|-----|------|

| Num. | Characteristic                           | Symbol              | Min   | Max | Min  | Max | Min  | Max | Unit |

| 100  | R/W Valid to DS Low                      | trwvosi             | 0     | _   | 0    | _   | 0    | _   | ns   |

| 101  | DS Low to Data-In Valid                  | t <sub>DSLDIV</sub> | _     | 30  |      | 25  |      | 20  | ns   |

| 102  | DTACK Low to Data-In Hold Time           | t <sub>DKLDH</sub>  | 0     | _   | 0    |     | 0    |     | ns   |

| 103  | AS Valid to DS Low                       | tasvosl             | 0     | _   | 0    |     | 0    |     | ns   |

| 104  | DTACK Low to AS, DS High                 | toklosh             | 0     | _   | 0    |     | 0    | _   | ns   |

| 105  | DS High to DTACK High                    | t <sub>DSHDKH</sub> | _     | 45  | _    | 40  | _    | 30  | ns   |

| 106  | DS Inactive to AS Inactive               | t <sub>DSIASI</sub> | 0     |     | 0    |     | 0    | _   | ns   |

| 107  | DS High to R/W High                      | toshrwh             | 0     |     | 0    |     | 0    | _   | ns   |

| 108  | DS High to Data High Impedance           | toshoz              | _     | 45  |      | 40  | _    | 30  | ns   |

| 108A | DS High to Data-Out Hold Time (see Note) | t <sub>DSHDH</sub>  | 0     | _   | 0    | _   | 0    | _   | ns   |

| 109A | Data Out Valid to DTACK Low              | t <sub>DOVDKL</sub> | 15    | _   | 15   | _   | 10   | _   | ns   |

NOTE: If  $\overline{AS}$  is negated before  $\overline{DS}$ , the data bus could be three-stated (spec 126) before  $\overline{DS}$  is negated.

Figure 6-8. External Master Internal Asynchronous Read Cycle Timing Diagram

Figure 6-9. External Master Internal Asynchronous Write Cycle Timing Diagram

# 6.11 AC ELECTRICAL SPECIFICATIONS—EXTERNAL MASTER INTERNAL SYNCHRONOUS READ/WRITE CYCLES

(see Figure 6-10, Figure 6-11, and Figure 6-12)

|      |                                        |                     | 16.67 | MHz      | 20 ( | MHz | 25  | MHz |      |

|------|----------------------------------------|---------------------|-------|----------|------|-----|-----|-----|------|

| Num. | Characteristic                         | Symbol              | Min   | Max      | Min  | Max | Min | Max | Unit |

| 110  | Address Valid to AS Low                | tavasl              | 15    | _        | 12   | _   | 10  |     | ns   |

| 111  | AS Low to Clock High                   | † <sub>ASLCH</sub>  | 30    | _        | 25   | _   | 20  | _   | ns   |

| 112  | Clock Low to AS High                   | tCLASH              | _     | 45       | _    | 40  |     | 30  | ns   |

| 113  | AS High to Address Hold Time on Write  | tashah              | 0     | _        | 0    |     | 0   | _   | ns   |

| 114  | AS Inactive Time                       | tash                | 1     | _        | 1    | _   | 1   |     | clk  |

| 115  | UDS/LDS Low to Clock High (see Note 2) | t <sub>SLCH</sub>   | 40    |          | 33   | _   | 27  |     | ns   |

| 116  | Clock Low to UDS/LDS High              | t <sub>CLSH</sub>   |       | 45       | _    | 40  |     | 30  | ns   |

| 117  | R/W Valid to Clock High (see Note 2)   | tewsch              | 30    |          | 25   | _   | 20  |     | ns   |

| 118  | Clock High to R/₩ High                 | tchawh              |       | 45       | _    | 40  |     | 30  | ns   |

| 119  | AS Low to IAC High                     | tasliah             | _     | 40       |      | 35  | _   | 27  | ns   |

| 120  | AS High to IAC Low                     | tashial             | _     | 40       |      | 35  | _   | 27  | ns   |

| 121  | AS Low to DTACK Low (0 Wait State)     | t <sub>ASLDTL</sub> | _     | 45       | _    | 40  | -   | 30  | ns   |

| 122  | Clock Low to DTACK Low (1 Wait State)  | t <sub>CLDTL</sub>  |       | 30       |      | 25  | _   | 20  | ns   |

| 123  | AS High to DTACK High                  | tashdth             |       | 45       | _    | 40  | _   | 30  | ns   |

| 124  | DTACK High to DTACK High Impedance     | <sup>t</sup> DTHDTZ |       | 15       | _    | 15  | _   | 10  | ns   |

| 125  | Clock High to Data-Out Valid           | tcHDOV              |       | 30       |      | 25  |     | 20  | ns   |

| 126  | AS High to Data High Impedance         | † <sub>ASHDZ</sub>  | _     | 45       | _    | 40  | - T | 30  | ns   |

| 127  | AS High to Data-Out Hold Time          | t <sub>ASHDOI</sub> | 0     | _        | 0    | _   | 0   | _   | ns   |

| 128  | AS High to Address Hold Time on Read   | tashai              | 0     | <b> </b> | 0    | -   | 0   | _   | ns   |

| 129  | UDS/LDS Inactive Time                  | tsH                 | 1     |          | 1    | -   | 1   | _   | clk  |

| 130  | Data-In Valid to Clock Low             | t <sub>CLDIV</sub>  | 30    | _        | 25   | _   | 20  | _   | ns   |

| 131  | Clock Low to Data-In Hold Time         | t <sub>CLDIH</sub>  | 15    |          | 12   | -   | 10  | _   | ns   |

- 1. Synchronous specifications above are valid only when SAM = 1 in the SCR.

- It is required that this signal not be asserted prior to the previous rising CLKO edge (i.e., in the previous clock cycle). It must be recognized by the IMP no sooner than the rising CLKO edge shown in the diagram.

Figure 6-10. External Master Internal Synchronous Read Cycle Timing Diagram

Figure 6-11. External Master Internal Synchronous Read Cycle Timing Diagram (One Wait State)

Figure 6-12. External Master Internal Synchronous Write Cycle Timing Diagram

# 6.12 AC ELECTRICAL SPECIFICATIONS—INTERNAL MASTER INTERNAL READ/WRITE CYCLES (see Figure 6-13)

|      |                               |                    | 16.67 MHz |     | 20 MHz |     | 25 MHz |     |      |  |

|------|-------------------------------|--------------------|-----------|-----|--------|-----|--------|-----|------|--|

| Num. | Characteristic                | Symbol             | Min       | Max | Min    | Max | Min    | Max | Unit |  |

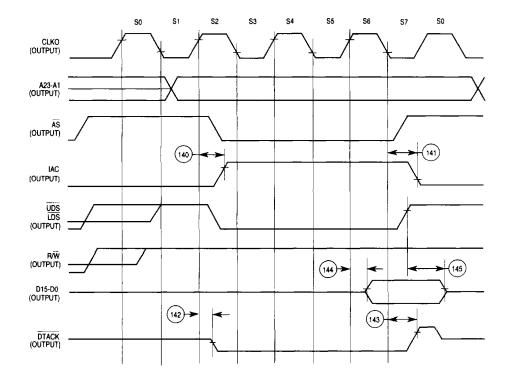

| 140  | Clock High to IAC High        | t <sub>CHIAH</sub> | _         | 40  |        | 35  | _      | 27  | ns   |  |

| 141  | Clock Low to IAC Low          | t <sub>CLIAL</sub> | _         | 40  | _      | 35  | _      | 27  | ns   |  |

| 142  | Clock High to DTACK Low       | t <sub>CHDTL</sub> | _         | 45  | _      | 40  | _      | 30  | ns   |  |

| 143  | Clock Low to DTACK High       | t <sub>CLDTH</sub> |           | 40  | _      | 35  | _      | 27  | ns   |  |

| 144  | Clock High to Data-Out Valid  | tcHDOV             | _         | 30  | _      | 25  | _      | 20  | ns   |  |

| 145  | AS High to Data-Out Hold Time | tashdoh            | 0         | _   | 0      | _   | 0      | _   | ns   |  |

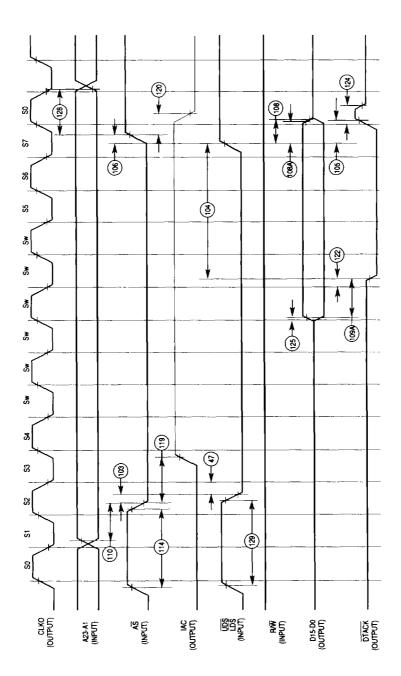

Figure 6-13. Internal Master Internal Read/Write Cycle Timing Diagram

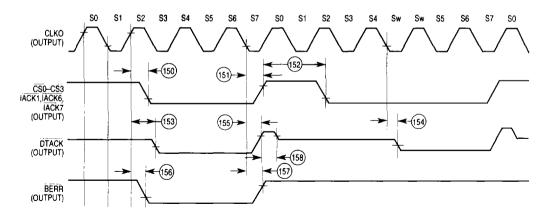

# 6.13 AC ELECTRICAL SPECIFICATIONS—CHIP-SELECT TIMING INTERNAL MASTER (see Figure 6-14)

|      |                                                   |                       | 16.67 | 16.67 MHz<br>Min Max |     | ИНz | 25 I | ИНz |      |

|------|---------------------------------------------------|-----------------------|-------|----------------------|-----|-----|------|-----|------|

| Num. | Characteristic                                    | Symbol                | Min   | Max                  | Min | Max | Min  | Max | Unit |

| 150  | Clock High to CS, IACK Low (see Note 2)           | <sup>†</sup> CHCSIAKL | 0     | 40                   | 0   | 35  | 0    | 27  | ns   |

| 151  | Clock Low to CS, IACK High (see Note 2)           | t <sub>CLCSIAKH</sub> | 0     | 40                   | 0   | 35  | 0    | 27  | ns   |

| 152  | CS Width Negated                                  | t <sub>CSH</sub>      | 60    | _                    | 50  | _   | 40   | _   | ns   |

| 153  | Clock High to DTACK Low (0 Wait State)            | <sup>t</sup> CHDTKL   | _     | 45                   | _   | 40  | _    | 30  | ns   |

| 154  | Clock Low to DTACK Low (1–6 Wait States)          | t <sub>CLDTKL</sub>   | _     | 30                   | _   | 25  |      | 20  | ns   |

| 155  | Clock Low to DTACK High                           | <sup>‡</sup> CLDTKH   | _     | 40                   | _   | 35  |      | 27  | ns   |

| 156  | Clock High to BERR Low (see Note 1)               | t <sub>CHBERL</sub>   | _     | 40                   | _   | 35  | _    | 27  | ns   |

| 157  | Clock Low to BERR High Impedance (see Note 1)     | tCLBERH               | _     | 40                   | -   | 35  | _    | 27  | ns   |

| 158  | DTACK High to DTACK High Impedance                | † <sub>DTKHDTKZ</sub> | _     | 15                   | _   | 15  |      | 10  | ns   |

| 171  | Input Data Hold Time from S6 Low                  | t <sub>IDHCL</sub>    | 5     | _                    | 5   | _   | 5    | _   | ns   |

| 172  | CS Negated to Data-Out Invalid (Write)            | t <sub>CSNDOI</sub>   | 10    | -                    | 10  | _   | 7    | _   | ns   |

| 173  | Address, FC Valid to CS Asserted                  | t <sub>AFVCSA</sub>   | 15    | _                    | 15  | -   | 15   | -   | ns   |

| 174  | CS Negated to Address, FC Invalid                 | t <sub>CSNAFI</sub>   | 15    | -                    | 15  | _   | 12   | -   | ns   |

| 175  | CS Low Time (0 Wait States)                       | t <sub>CSLT</sub>     | 120   | _                    | 100 | _   | 80   | _   | ns   |

| 176  | CS Negated to R/W Invalid                         | tcsnrwi               | 10    | _                    | 10  | ļ   | 7    | _   | ns   |

| 177  | CS Asserted to R/W Low (Write)                    | t <sub>CSARWL</sub>   | _     | 10                   | _   | 10  | _    | 8   | ns   |

| 178  | CS Negated to Data-In Invalid (Hold Time on Read) | tcsndii               | 0     | _                    | 0   | _   | 0    | _   | ns   |

- 1. This specification is valid only when the ADCE or WPVE bits in the SCR are set.

- 2. For loading capacitance less than or equal to 50 pF, subtract 4 ns from the maximum value given.

- 3. Since AS and CS are asserted/negated on the same CLKO edges, no AS to CS relative timings can be specified. However, CS timings are given relative to a number of other signals, in the same manner as AS. See Figure 6-2 and Figure 6-3 for diagrams.

Figure 6-14. Internal Master Chip-Select Timing Diagram

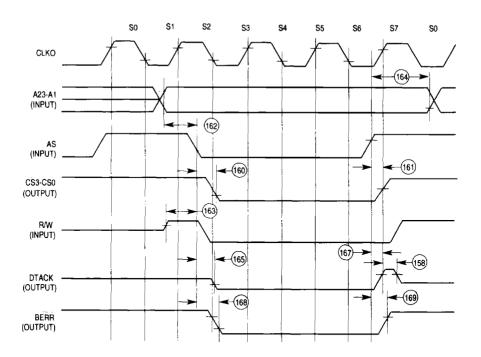

# 6.14 AC ELECTRICAL SPECIFICATIONS—CHIP-SELECT TIMING EXTERNAL MASTER (see Figure 6-15)

|      |                                                    |                      | 16.67 | 7 MHz | 20 1 | MHz | 25 I | MHz |      |

|------|----------------------------------------------------|----------------------|-------|-------|------|-----|------|-----|------|

| Num. | Characteristic                                     | Symbol               | Min   | Max   | Min  | Max | Min  | Max | Unit |

| 154  | Clock Low to DTACK Low (1-6 Wait States)           | † <sub>CLDTKL</sub>  |       | 30    | -    | 25  |      | 20  | ns   |

| 160  | AS Low to CS Low                                   | tASLCSL              | _     | 30    | _    | 25  | _    | 20  | ns   |

| 161  | AS High to CS High                                 | t <sub>ASHCSH</sub>  | -     | 30    |      | 25  | _    | 20  | ns   |

| 162  | Address Valid to AS Low                            | TAVASL               | 15    | _     | 12   |     | 10   | -   | ns   |

| 163  | R/W Valid to AS Low (see Note 1)                   | tRWVASL              | 15    | _     | 12   | _   | 10   | _   | ns   |

| 164  | AS Negated to Address Hold Time                    | tashai               | 0     | _     | 0    | -   | 0    | _   | ns   |

| 165  | AS Low to DTACK Low (0 Wait State)                 | 1 <sub>ASLDTKL</sub> |       | 45    | _    | 40  | _    | 30  | ns   |

| 167  | AS High to DTACK High                              | t <sub>ASHDTKH</sub> | _     | 30    | _    | 25  | _    | 20  | ns   |

| 168  | AS Low to BERR Low (see Note 2)                    | t <sub>ASLBERL</sub> | _     | 30    | _    | 25  | _    | 20  | ns   |

| 169  | AS High to BERH High Impedance (see Notes 2 and 3) | tashberh             | _     | 30    | _    | 25  | _    | 20  | ns   |

- 1. The minimum value must be met to guarantee write protection operation.

- 2. This specification is valid when the ADCE or WPVE bits in the SCR are set.

- 3. Also applies after a timeout of the hardware watchdog.

Figure 6-15. External Master Chip-Select Timing Diagram

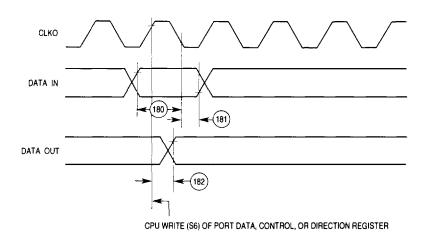

# 6.15 AC ELECTRICAL SPECIFICATIONS—PARALLEL I/O

(see Figure 6-16)

|      |                                                                          |                  | 16.67 MHz |     | 20 MHz |     | 25 MHz |     |      |  |

|------|--------------------------------------------------------------------------|------------------|-----------|-----|--------|-----|--------|-----|------|--|

| Num. | Characteristic                                                           | Symbol           | Min       | Max | Min    | Max | Min    | Max | Unit |  |

| 180  | Input Data Setup Time (to Clock Low)                                     | t <sub>DSU</sub> | 20        |     | 20     | T — | 14     |     | ns   |  |

| 181  | Input Data Hold Time (from Clock Low)                                    | t <sub>DH</sub>  | 10        | _   | 10     | _   | 19     |     | ns   |  |

| 182  | Clock High to Data-out Valid<br>(CPU Writes Data, Control, or Direction) | tchbov           |           | 35  | _      | 30  | -      | 24  | ns   |  |

Figure 6-16. Parallel I/O Data-In/Data-Out Timing Diagram

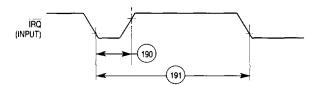

### 6.16 AC ELECTRICAL SPECIFICATIONS—INTERRUPTS

(see Figure 6-17)

|      |                                                               |                   | 16.67 MHz |     | 16.67 MHz 20 MHz |     |     | 25 I |      |

|------|---------------------------------------------------------------|-------------------|-----------|-----|------------------|-----|-----|------|------|

| Num. | Characteristic                                                | Symbol            | Min       | Max | Min              | Max | Min | Max  | Unit |

| 190  | Interrupt Pulse Width Low IRQ (Edge Triggered Mode) or PB8-11 | lew               | 50        | -   | 42               |     | 34  | _    | ns   |

| 191  | Minimum Time Between Active Edges                             | t <sub>AEMT</sub> | 3         | _   | 3                |     | 3   |      | clk  |

NOTE: Setup time for the asynchronous inputs IPL2-IPL0 and AVEC guarantees their recognition at the next falling edge of the clock.

Figure 6-17. Interrupts Timing Diagram

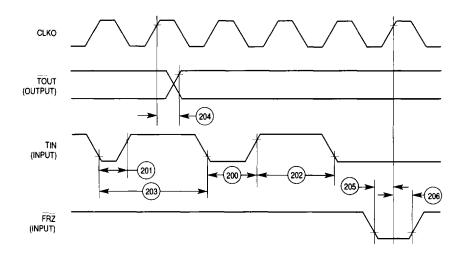

# 6.17 AC ELECTRICAL SPECIFICATIONS—TIMERS

(see Figure 6-18)

|      |                                                                  |                    | 16.67 | 16.67 MHz |     | MHz | 25 MHz |     |      |

|------|------------------------------------------------------------------|--------------------|-------|-----------|-----|-----|--------|-----|------|

| Num. | Characteristic                                                   | Symbol             | Min   | Max       | Min | Max | Min    | Max | Unit |

| 200  | Timer Input Capture Pulse Width                                  | t <sub>TPW</sub>   | 50    | _         | 42  | _   | 34     | _   | ns   |

| 201  | TIN Clock Low Pulse Width                                        | tTICLT             | 50    | _         | 42  |     | 34     | _   | ns   |

| 202  | TIN Clock High Pulse Width and Input<br>Capture High Pulse Width | t <sub>TICHT</sub> | 2     | _         | 2   | _   | 2      | _   | clk  |

| 203  | TIN Clock Cycle Time                                             | t <sub>cyc</sub>   | 3     |           | 3   |     | 3      |     | clk  |

| 204  | Clock High to TOUT Valid                                         | <sup>‡</sup> снтоv | _     | 35        | _   | 30  | -      | 24  | ns   |

| 205  | FRZ Input Setup Time (to Clock High) (see Note 1)                | t <sub>FRZSU</sub> | 20    |           | 20  | _   | 14     | _   | ns   |

| 206  | FRZ Input Hold Time (from Clock High)                            | t <sub>FRZHT</sub> | 10    | _         | 10  | _   | 7      | _   | ns   |

### NOTES:

- 1. FRZ should be negated during total system reset.

- 2. The TIN specs above do not apply to the use of TIN1 as a baud rate generator input clock. In such a case, specifications 1–3 may be used.

Figure 6-18. Timers Timing Diagram

6

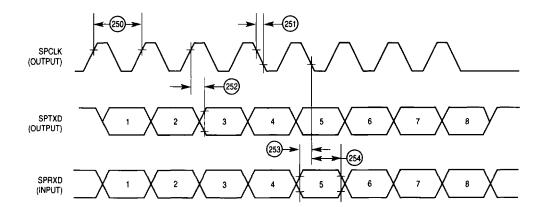

# 6.18 AC ELECTRICAL SPECIFICATIONS—SERIAL COMMUNICATIONS PORT (see Figure 6-19).

|      |                                           | 16.67 | 16.67 MHz |     | MHz | 25  | MHz |      |

|------|-------------------------------------------|-------|-----------|-----|-----|-----|-----|------|

| Num. | Characteristic                            | Min   | Max       | Min | Max | Min | Max | Unit |

| 250  | SPCLK Clock Output Period                 | 4     | 64        | 4   | 64  | 4   | 64  | clks |

| 251  | SPCLK Clock Output Rise/Fall Time         | 0     | 15        | 0   | 10  | 0   | 8   | ns   |

| 252  | Delay from SPCLK to Transmit (see Note 1) | 0     | 40        | 0   | 30  | 0   | 24  | ns   |

| 253  | SCP Receive Setup Time (see Note 1)       | 40    | -         | 30  | _   | 24  | I — | ns   |

| 254  | SCP Receive Hold Time (see Note 1)        | 10    |           | 8   | _   | 7   | _   | ns   |

- 1. This also applies when SPCLK is inverted by CI in the SPMODE register.

- 2. The enable signals for the slaves may be implemented by the parallel I/O pins.

Figure 6-19. Serial Communication Port Timing Diagram

# Q

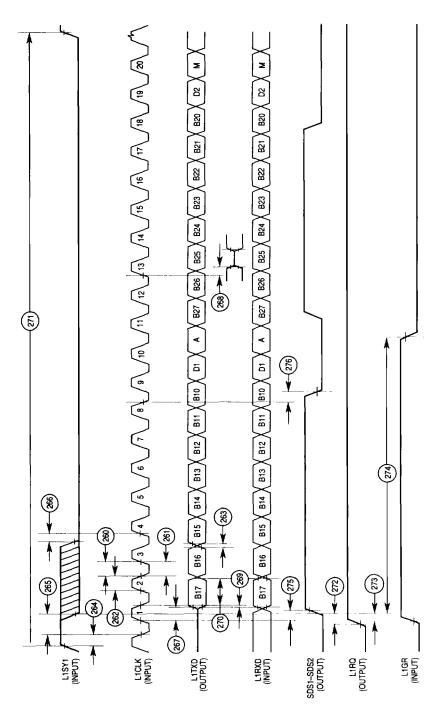

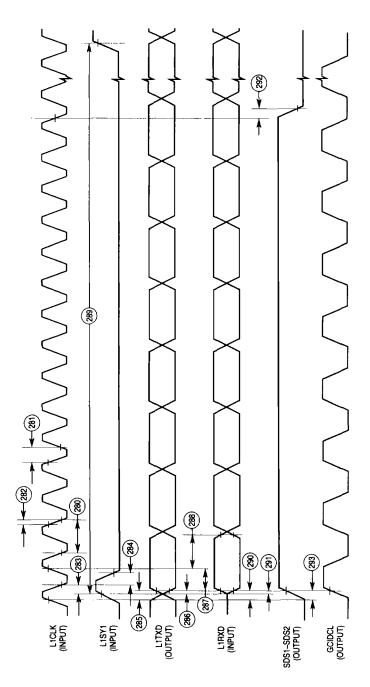

### 6.19 AC ELECTRICAL SPECIFICATIONS—IDL TIMING (All timing measurements,

unless otherwise specified, are referenced to the L1CLK at 50% point of VDD) (see Figure 6-20).

|      |                                                               | 16.67 | 16.67 MHz |      | ИHz | 25 N |     |       |

|------|---------------------------------------------------------------|-------|-----------|------|-----|------|-----|-------|

| Num. | Characteristic                                                | Min   | Max       | Min  | Max | Min  | Max | Unit  |

| 260  | L1CLK (IDL Clock) Frequency (see Note 1)                      | _     | 6.66      | _    | 8   | -    | 10  | MHz   |

| 261  | L1CLK Width Low                                               | 55    | 1         | 45   | -   | 37   | _   | ns    |

| 262  | L1CLK Width High (see Note 3)                                 | P+10  |           | P+10 | _   | P+10 | _   | ns    |

| 263  | L1TXD, L1RQ, SDS1-SDS2 Rising/Falling Time                    | ı     | 20        | -    | 17  | -    | 14  | ns    |

| 264  | L1SY1 (sync) Setup Time (to L1CLK Falling Edge)               | 30    | ı         | 25   | 1   | 20   | -   | ns    |

| 265  | L1SY1 (sync) Hold Time (from L1CLK Falling Edge)              | 50    | 1         | 40   | l   | 34   | ı   | ns    |

| 266  | L1SY1 (sync) Inactive Before 4th L1CLK                        | 0     |           | 0    |     | 0    | _   | ns    |

| 267  | L1TxD Active Delay (from L1CLK Rising Edge)                   | 0     | 75        | 0    | 65  | 0    | 50  | ns    |

| 268  | L1TxD to High Impedance (from L1CLK Rising Edge) (see Note 2) | 0     | 50        | 0    | 42  | 0    | 34  | ns    |

| 269  | L1RxD Setup Time (to L1CLK Falling Edge)                      | 50    | 1         | 42   | 1   | 34   | -   | ns    |

| 270  | L1RxD Hold Time (from L1CLK Falling Edge)                     | 50    |           | 42   | _   | 34   | _   | ns    |

| 271  | Time Between Successive IDL syncs                             | 20    | _         | 20   | _   | 20   | _   | L1CLK |

| 272  | L1RQ Valid before Falling Edge of L1SY1                       | _ 1   | _         | 1    | 1   | _ 1  | _   | L1CLK |

| 273  | L1GR Setup Time (to L1SY1 Falling Edge)                       | 50    | 1         | 42   | 1   | 34   | -   | ns    |

| 274  | L1GR Hold Time (from L1SY1 Falling Edge)                      | 50    | -         | 42   | _   | 34   | _   | ns    |

| 275  | SDS1-SDS2 Active Delay from L1CLK Rising Edge                 | 10    | 75        | 10   | 65  | 7    | 50  | ns    |

| 276  | SDS1-SDS2 Inactive Delay from L1CLK Falling Edge              | 10    | 75        | 10   | 65  | 7    | 50  | ns    |

- 1. The ratio CLKO/L1CLK must be greater than 2.5/1.

- 2. High impedance is measured at the 30% and 70% of  $V_{DD}$  points, with the line at  $V_{DD}/2$  through 10K in parallel with 130 pF.

- 3. Where P = 1/CLKO. Thus, for a 16.67-MHz CLKO rate, P = 60 ns.

Figure 6-20. IDL Timing Diagram

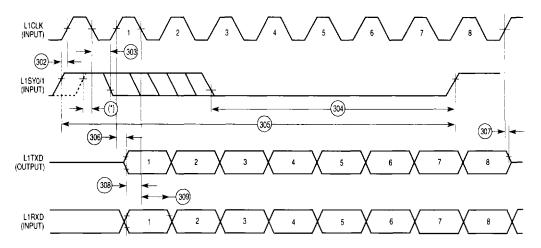

### 6.20 AC ELECTRICAL SPECIFICATIONS—GCI TIMING

GCI supports the NORMAL mode and the GCI channel 0 (GCN0) in MUX mode. Normal mode uses 512 kHz clock rate (256K bit rate). MUX mode uses 256 x n - 3088 kbs (clock rate is data rate x 2). The ratio CLKO/L1CLK must be greater than 2.5/1 (see Figure 6-21).

|      |                                                            | 16.67 | MHz   | 20 1      | MHz   | 25 (      | MHz   |                |

|------|------------------------------------------------------------|-------|-------|-----------|-------|-----------|-------|----------------|

| Num. | Characteristic                                             | Min   | Max   | Min       | Max   | Min       | Max   | Unit           |

|      | L1CLK GCI Clock Frequency (Normal Mode) (see Note 1)       | _     | 512   | -         | 512   | _         | 512   | kHz            |

| 280  | L1CLK Clock Period Normal Mode (see Note 1)                | 1800  | 2100  | 1800      | 2100  | 1800      | 2100  | ns             |

| 281  | L1CLK Width Low/High Normal Mode                           | 840   | 1450  | 840       | 1450  | 840       | 1450  | ns             |

| 282  | L1CLK Rise/Fall Time Normal Mode (see Note 4)              |       | _     | 1         |       | _         | _     | ns             |

| ·    | L1CLK (GCI Clock) Frequency (MUX Mode) (see Note 1)        |       | 6.668 | -         | 6.668 | _         | 6.668 | MHz            |

| 280  | L1CLK Clock Period MUX Mode (see Note 1)                   | 150   |       | 150       | _     | 150       | _     | ns             |

| 281  | L1CLK Width Low MUX Mode                                   | 55    | -     | 55        | _     | 55        | _     | ns             |

| 281A | L1CLK Width High MUX Mode (see Note 5)                     | P+10  | _     | P+10      | _     | P+10      | _     | ns             |

| 282  | L1CLK Rise/Fall Time MUX Mode (see Note 4)                 | _     |       | -         |       | _         | _     | ns             |

| 283  | L1SY1 Sync Setup Time to L1CLK Falling Edge                | 30    | _     | 25        | _     | 20        | _     | ns             |

| 284  | L1SY1 Sync Hold Time from L1CLK Falling Edge               | 50    | _     | 42        |       | 34        | _     | ns             |

| 285  | L1TxD Active Delay (from L1CLK Rising Edge) (see Note 2)   | 0     | 100   | 0         | 85    | 0         | 70    | ns             |

| 286  | L1TxD Active Delay (from L1SY1 Rising Edge) (see Note 2)   | 0     | 100   | 0         | 85    | 0         | 70    | ns             |

| 287  | L1RxD Setup Time to L1CLK Rising Edge                      | 20    | _     | 17        | _     | 14        | _     | ns             |

| 288  | L1RxD Hold Time from L1CLK Rising Edge                     | 50    | _     | 42        | _     | 34        | -     | ns             |

| 289  | Time Between Successive L1SY1in Normal SCIT Mode           |       | =     | 64<br>192 |       | 64<br>192 | _     | L1CLK<br>L1CLK |

| 290  | SDS1-SDS2 Active Delay from L1CLK Rising Edge (see Note 3) | 10    | 90    | 10        | 75    | 7         | 60    | ns             |

| 291  | SDS1-SDS2 Active Delay from L1SY1 Rising Edge (see Note 3) | 10    | 90    | 10        | 75    | 7         | 60    | ns             |

| 292  | SDS1-SDS2 Inactive Delay from L1CLK Falling Edge           | 10    | 90    | 10        | 75    | 7         | 60    | ns             |

| 293  | GCIDCL (GCI Data Clock) Active Delay                       | 0     | 50    | 0         | 42    | 0         | 34    | ns             |

- 1. The ratio CLKO/L1CLK must be greater than 2.5/1.

- 2. Condition C<sub>L</sub> = 150 pF. L1TD becomes valid after the L1CLK rising edge or L1SY1, whichever is later.

- 3.SDS1-SDS2 become valid after the L1CLK rising edge or L1SY1, whichever is later.

- 4. Schmitt trigger used on input buffer.

- 5. Where P = 1/CLKO. Thus, for a 16.67-MHz CLKO rate, P = 60 ns.

Figure 6-21. GCI Timing Diagram

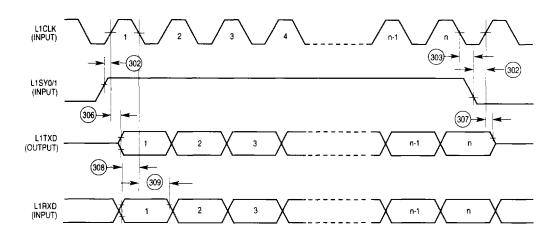

# 6.21 AC ELECTRICAL SPECIFICATIONS—PCM TIMING

There are two sync types:

Short Frame—Sync signals are one clock cycle prior to the data Long Frame—Sync signals are N-bits that envelope the data, N > 0; see Figure 6-22 and Figure 6-23).

| _    |                                                        | 16.67 | MHz  | 20 1 | ИНz | 25 I | MHz  |       |

|------|--------------------------------------------------------|-------|------|------|-----|------|------|-------|

| Num. | Characteristic                                         | Min   | Max  | Min  | Max | Min  | Max  | Unit  |

| 300  | L1CLK (PCM Clock) Frequency (see Note 1)               | _     | 6.66 |      | 8.0 | _    | 10.0 | MHz   |

| 301  | L1CLK Width Low                                        | 55    | _    | 45   | _   | 37   | _    | ns    |

| 301A | L1CLK Width High (see Note 4)                          | P+10  |      | P+10 |     | P+10 | _    | ns    |

| 302  | L1SY0-L1SY1 Setup Time to L1CLK<br>Rising Edge         | 0     | _    | 0    | -   | 0    | _    | ns    |

| 303  | L1SY0-L1SY1 Hold Time from L1CLK Falling Edge          | 40    | _    | 33   | _   | 27   | _    | ns    |

| 304  | L1SY0-L1SY1 Width Low                                  | 1     | -    | 1    | _   | 1    | _    | L1CLK |

| 305  | Time Between Successive Sync Signals (Short Frame)     | 8     | _    | 8    | _   | 8    | _    | L1CLK |

| 306  | L1TxD Data Valid after L1CLK Rising Edge (see Note 2)  | 0     | 70   | 0    | 60  | 0    | 47   | ns    |

| 307  | L1TxD to High Impedance (from L1CLK Rising Edge)       | 0     | 50   | 0    | 42  | 0    | 34   | ns    |

| 308  | L1RxD Setup Time (to L1CLK Falling Edge) (see Note 3)  | 20    | _    | 17   |     | 14   | _    | ns    |

| 309  | L1RxD Hold Time (from L1CLK Falling Edge) (see Note 3) | 50    | _    | 42   | _   | 34   |      | ns    |

- 1. The ratio CLK/L1CLK must be greater than 2.5/1.

- 2. L1TxD becomes valid after the L1CLK rising edge or the sync enable, whichever is later, if long frames are used. This note should only be used if the user can guarantee that only one sync pin (L1SY0 and L1SY1) is changed simultaneously in the selection and de-selection of the desired PCM channel time slot. A safe example of this is using only PCM CH-1. Another example is using CH-1 and CH-2 only, where CH-1 and CH-2 are not contiguous on the PCM highway.

- 3. Specification valid for both sync methods.

- 4. Where P = 1/CLKO. Thus, for a 16.67-MHz CLKO rate, P = 60 ns.

Figure 6-22. PCM Timing Diagram (SYNC Envelopes Data)

NOTE: (\*) If L1SYn is guaranteed to make a smooth low to high transition (no spikes) while the clock is high, setup time can be defined as shown (min 20 ns).

Figure 6-23. PCM Timing Diagram (SYNC Prior to 8-Bit Data)

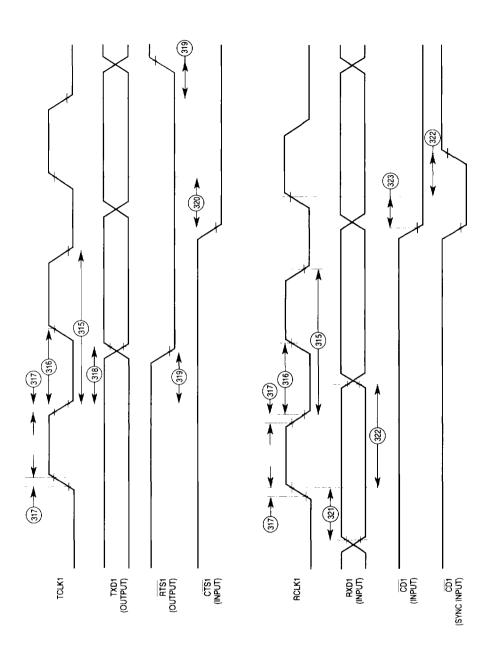

### 6.22 AC ELECTRICAL SPECIFICATIONS—NMSI TIMING

The NMSI mode uses two clocks, one for receive and one for transmit. Both clocks can be internal or external. When t he clock is internal, it is generated by the internal baud rate generator and it is output on TCLK or RCLK. All the timing is related to the external clock pin. The timing is specified for NMSI1. It is also valid for NMSI2 and NMSI3 (see Figure 6-24).

|      |                                                          | 16.67 | MHz         | 16.67 | MHz         | 20 F | VIHz        | 20 F | ИHz | 25 I | VHz  | 25 MHz |     |      |

|------|----------------------------------------------------------|-------|-------------|-------|-------------|------|-------------|------|-----|------|------|--------|-----|------|

| Num. | Characteristic                                           | Inte  | rnal<br>ock |       | rnal<br>ock |      | rnal<br>ock | Exte |     |      |      | Exte   |     | Unit |

|      |                                                          | Min   | Max         | Min   | Max         | Min  | Max         | Min  | Max | Min  | Max  | Min    | Max |      |

| 315  | RCLK1 and TCLK1 Frequency (see Note 1)                   | _     | 5.55        | _     | 6.668       |      | 6.66        | _    | 8   | 1    | 8.33 | -      | 10  | MHz  |

| 316  | RCLK1 and TCLK1 Low (see Note 4)                         | 65    |             | P+10  | _           | 55   | _           | P+10 | 1   | 45   |      | P+10   | _   | ns   |

| 316a | RCLK1 and TCLK1 High                                     | 65    | _           | 55    |             | 55   | _           | 45   |     | 45   | —    | 35     | -   | ns   |

| 317  | RCLK1 and TCLK1 Rise/Fall Time (see Note 3)              | _     | 20          | _     | _           | _    | 17          | _    | -   | _    | 14   | _      | _   | ns   |

| 318  | TXD1 Active Delay from TCLK1 Falling Edge                | 0     | 40          | 0     | 70          | 0    | 30          | 0    | 50  | 0    | 25   | 0      | 40  | ns   |

| 319  | RTS1 Active/Inactive Delay from TCLK1 Falling Edge       | 0     | 40          | 0     | 100         | 0    | 30          | 0    | 80  | 0    | 25   | 0      | 65  | ns   |

| 320  | CTS1 Setup Time to TCLK1<br>Rising Edge                  | 50    | _           | 10    | _           | 40   | _           | 7    |     | 35   | _    | 7      | _   | ns   |

| 321  | RXD1 Setup Time to RCLK1<br>Rising Edge                  | 50    | -           | 10    | _           | 40   | _           | 7    | _   | 35   | _    | 7      | _   | ns   |

| 322  | RXD1 Hold Time from<br>RCLK1 Rising Edge (see<br>Note 2) | 10    |             | 50    | _           | 7    |             | 40   | _   | 7    |      | 35     | _   | ns   |

| 323  | CD1 Setup Time to RCLK1<br>Rising Edge                   | 50    | _           | 10    | _           | 40   | -           | 7    | _   | 35   | _    | 7      | _   | ns   |

- 1. The ratio CLKO/TCLK1 and CLKO/RCLK1 must be greater than or equal to 2.5/1 for external clock. The input clock to the baud rate generator may be either an internal clock or TIN1, and may be as fast as EXTAL. However, the output of the baud rate generator must provide a CLKO/TCLK1 and CLKO/RCLK1 ratio greater than or equal to 3/1. In asynchronous mode (UART), the bit rate is 1/16 of the TCLK1/RCLK1 clock rate.

- 2. Also applies to  $\overline{CD}$  hold time when  $\overline{CD}$  is used as an external sync in BISYNC or totally transparent mode.

- 3. Schmitt triggers used on input buffers.

- 4. Where P = 1/CLKO. Thus, for a 16.67-MHz CLKO rate, P = 60 ns.

Figure 6-24. NMSI Timing Diagram