## 2 CHANNELS, 200MA BOOST LED BACKLIGHT DRIVER

Preliminary Information September 2017

#### **GENERAL DESCRIPTION**

The IS31BL3555 is a step-up controller with an integrated switching FET for driving white LED arrays in LCD panel backlight applications. The boost controller is a current mode, fixed frequency architecture with the switching frequency set by an external resistor. The integrated boost controller generates the minimum output voltage to keep all LEDs illuminated at the set current. The current in each of the 2 channels is programmed to a specific value with an external current set resistor and matched to within 1%.

LED dimming is achieved using an external digital PWM signal to either adjust the internal ISET current or pulse-width-modulate the LED intensity. The LED sinks have a fast response to a PWM input making it possible to achieve a high contrast ratio of 10,000:1.

A synchronization pin can be used to synchronize multiple IS31BL3555 devices or to synchronize with the external PWM source in the range of 580kHz to 1MHz.

The IS31BL3555 integrates protection features including output overvoltage, open or shorted diode, open or shorted LED, shorted FSET or ISET resistor, and IC over temperature. A dual level cycle-by-cycle current limit function provides soft start and protects the internal current switch against high current overloads.

The IS31BL3555 is available in a thermally enhanced eTSSOP-16 package.

#### **FEATURES**

- Input voltage range is 4.75V to 40V

- Excellent input voltage transient response

- Sync function to synchronize boost converter switching frequency up to 1MHz

- Single resistor primary OVP minimizes VOUT leakage

- Fully integrated LED current sinks and boost converter up to 55V

- LED current of 200mA per channel

- 1% LED to LED matching accuracy

- Internal secondary OVP for redundant protection

- Drives up to 12 series LEDs in 2 parallel strings

- 10000:1 PWM dimming at 100Hz

- PWM and analog dimming inputs

- Built-in protection features:

- Shorted FSET or ISET resistor

- Open or shorted LED

- Open boost Schottky

- Overtemperature (OTP)

### **APPLICATIONS**

- LCD monitor

- LCD display module

- LCD TV

- Car infotainment

- Cluster

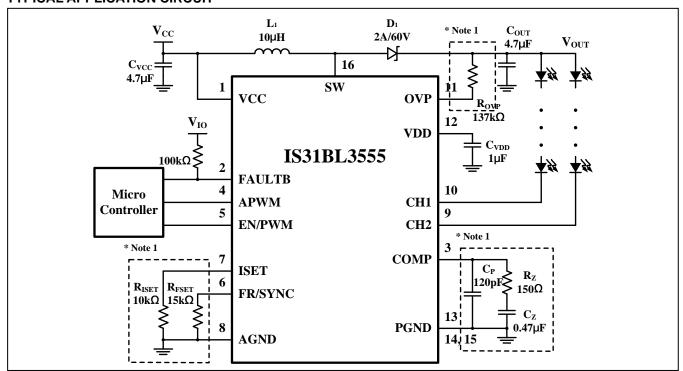

# **TYPICAL APPLICATION CIRCUIT**

Figure 1 Typical Application Circuit

Note 1: Value of those devices need to adjust according different applications.

# **PIN CONFIGURATION**

| Package   | Pin Configuration (Top View)          |                 |                                             |                                   |  |  |

|-----------|---------------------------------------|-----------------|---------------------------------------------|-----------------------------------|--|--|

| eTSSOP-16 | VCC FAULTB COMP APWM FR/SYNC SET AGND | 1 2 3 4 5 6 7 8 | 16<br>15<br>14<br>13<br>12<br>11<br>10<br>9 | SW PGND PGND PGND VDD OVP CH1 CH2 |  |  |

# **PIN DESCRIPTION**

| No.   | Pin         | Description                                                                                                                                                                                                                                 |

|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VCC         | Power supply input. Bypass VCC to GND with a capacitor to keep the DC input voltage constant.                                                                                                                                               |

| 2     | FAULTB      | Open drain fault flag to indicate a fault condition. Connect a $100 k\Omega$ resistor between this pin and the required logic level voltage.                                                                                                |

| 3     | COMP        | Soft-start and control loop compensation. Connect a series $R_Z$ - $C_Z$ network from this pin to ground for control loop compensation.                                                                                                     |

| 4     | APWM        | Analog trimming option for dimming. Applying a digital PWM signal to this pin adjusts the internal ISET current.                                                                                                                            |

| 5     | EN/PWM      | PWM signal input for LED dimming, used to control the LED intensity by using pulse width modulation. Also used to enable the IS31BL3555.                                                                                                    |

| 6     | FR/SYNC     | Frequency and synchronization pin. A resistor $R_{FR}$ from this pin to ground sets the switching frequency. This pin can also be used to synchronize two or more IS31BL3555s in the system. The maximum synchronization frequency is 1MHz. |

| 7     | ISET        | LED current adjust input. Connect a resistor R <sub>ISET</sub> between ISET pin and GND to set the reference current through each LED string.                                                                                               |

| 8     | AGND        | LED signal ground.                                                                                                                                                                                                                          |

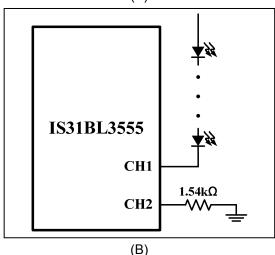

| 9,10  | CH2,CH1     | Connect the cathodes of the LED strings to these pins. All unused pins should be connected with a $1.54 k\Omega$ resistor to ground.                                                                                                        |

| 11    | OVP         | Over voltage protection pin; connect the R <sub>OVP</sub> resistor from VOUT to this pin to adjust the overvoltage protection.                                                                                                              |

| 12    | VDD         | Output of internal LDO; connect a 1µF decoupling capacitor between this pin and ground.                                                                                                                                                     |

| 13~15 | PGND        | Power ground for internal NMOS.                                                                                                                                                                                                             |

| 16    | SW          | The drain of the internal NMOS switch of the boost converter.                                                                                                                                                                               |

|       | Thermal Pad | Connect to GND.                                                                                                                                                                                                                             |

ORDERING INFORMATION Industrial Range: -40°C to +125°C

| Order Part No.                        | Package              | QTY                  |

|---------------------------------------|----------------------|----------------------|

| IS31BL3555-ZLS4-TR<br>IS31BL3555-ZLS4 | eTSSOP-16, Lead-free | 2500/Reel<br>96/Tube |

Copyright © 2017 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products. Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

## **ABSOLUTE MAXIMUM RATINGS**

| Voltage in CHx, OVP pins                                                       | -0.3V ~ +55V   |  |

|--------------------------------------------------------------------------------|----------------|--|

| Voltage in VCC, FAULTB pins                                                    | -0.3V ~ +40V   |  |

| Voltage in ISET, FR/SYNC, APWM, COMP pins                                      | -0.3V ~ +5.5V  |  |

| Voltage in SW pin, continuous                                                  | -0.6V ~ 65V    |  |

| Voltage in SW pin, t<50ns                                                      | -1.0V          |  |

| All other pins                                                                 | -0.3V ~ +6.0V  |  |

| Package thermal resistance, θ <sub>JA</sub> , thermal simulation @25°C ambient | 39.9°C/W       |  |

| temperature, still air convection, 2s2p boards according to JESD51             | 39.9 C/VV      |  |

| Operating junction temperature, T <sub>A</sub> =T <sub>J</sub>                 | +150°C         |  |

| Storage temperature range, T <sub>STG</sub>                                    | -65°C ~ +150°C |  |

| ESD (HBM)                                                                      | ±2kV           |  |

| ESD (CDM)                                                                      | ±750V          |  |

#### Note:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS (NOTE 1, 2)**

$T_J$ = -40°C ~ +125°C,  $V_{CC}$ = 12V. Typical value is  $T_J$ = 25°C, unless otherwise specified.

| Symbol                | Parameter                                | Condition                                                                        | Min. | Тур. | Max. | Unit |

|-----------------------|------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Input Sup             | ply                                      |                                                                                  |      | •    |      |      |

| $V_{CC}$              | Input voltage                            | (Note 3, 4)                                                                      | 4.75 |      | 40   | V    |

| $V_{\text{UVLO}_{R}}$ | UVLO start threshold                     | V <sub>CC</sub> rising (Note 3)                                                  |      |      | 4.35 | V    |

| V <sub>UVLO_F</sub>   | UVLO stop threshold                      | V <sub>CC</sub> falling (Note 3)                                                 |      |      | 3.90 | V    |

| $V_{\text{UVLO\_HY}}$ | UVLO hysteresis                          | (Note 2)                                                                         | 300  | 450  | 600  | mV   |

| I <sub>CC</sub>       | Quiescent current                        | V <sub>EN/PWM</sub> = V <sub>IH</sub> , f <sub>SW</sub> = 1MHz, no load (Note 3) |      | 5.5  | 10   | mA   |

| I <sub>SD</sub>       | Shutdown current                         | $V_{CC}$ = 12V, $V_{EN/PWM}$ = $V_{FR/SYNC}$ = 0V (Note 3)                       |      | 5.0  | 10   | μA   |

| Input Log             | ic Levels (EN/PWM and APWM)              |                                                                                  |      |      |      |      |

| V <sub>IL</sub>       | Input logic level-low                    | VCC throughout operating input voltage range (Note 3)                            |      |      | 0.4  | ٧    |

| V <sub>IH</sub>       | Input logic level-high                   | VCC throughout operating input voltage range (Note 3)                            | 1.5  |      |      | ٧    |

| R <sub>EN/PWM</sub>   | EN/PWM pin open drain pull-down resistor |                                                                                  | 60   | 100  | 140  | kΩ   |

| R <sub>APWM</sub>     | APWM pull-down resistor                  |                                                                                  | 60   | 100  | 140  | kΩ   |

ELECTRICAL CHARACTERISTICS (CONTINUED)  $T_J$ = -40°C ~ +125°C,  $V_{CC}$ = 12V. Typical value is  $T_J$ = 25°C, unless otherwise specified.

| Symbol               | Parameter                              | Condition                                                                                          | Min.  | Тур.     | Max.  | Unit    |

|----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------|-------|----------|-------|---------|

| APWM                 |                                        |                                                                                                    | •     | <u> </u> | •     | •       |

| $f_{APWM}$           | APWM frequency                         | V <sub>IH</sub> = 1.5V, V <sub>IL</sub> = 0.4V (Note 2,3)                                          | 20    |          | 1000  | kHz     |

| Overvolta            | age Protection                         |                                                                                                    |       |          |       | •       |

| $V_{\text{OVP1}}$    | OVP threshold                          | OVP connected to V <sub>OUT</sub> (Note 3)                                                         | 7.7   | 8.1      | 8.5   | V       |

| $I_{\text{OVPS}}$    | OVP sense current                      | (Note 3)                                                                                           | 188   | 199      | 210   | μA      |

| $I_{OVPL}$           | OVP leakage current                    | (Note 3)                                                                                           |       | 0.1      | 1     | μA      |

| V <sub>OVP2</sub>    | Secondary over voltage protection      | (Note 3)                                                                                           |       | 60       |       | V       |

| Boost Sw             | vitch                                  |                                                                                                    |       |          |       |         |

| R <sub>SW</sub>      | Switch on-resistance                   | I <sub>SW</sub> = 0.750A, V <sub>CC</sub> = 12V(Note 3)                                            | 75    | 300      | 600   | mΩ      |

| I <sub>SW_LKG</sub>  | Switch leakage current                 | V <sub>SW</sub> = 16V, V <sub>EN/PWM</sub> = V <sub>IL</sub> (Note 3)                              |       | 0.1      | 1     | μA      |

| I <sub>SW_LIM1</sub> | Switch current limit                   | (Note 3)                                                                                           | 3.0   | 3.5      | 4.2   | Α       |

| I <sub>SW_LIM2</sub> | Secondary switch current limit         | Higher than maximum I <sub>SW_LIM1</sub> for all conditions, device latches when detected (Note 2) |       | 7.0      |       | А       |

| t <sub>SW_ON</sub>   | Minimum switch on-time                 | (Note 3)                                                                                           |       | 200      |       | ns      |

| t <sub>SW_OFF</sub>  | Minimum switch off-time                | (Note 3)                                                                                           |       | 50       |       | ns      |

| Oscillato            | r Frequency                            |                                                                                                    |       |          |       |         |

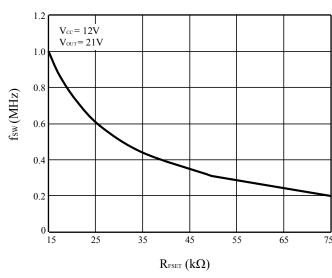

| r                    | Os sillata a fra avvan avv             | R <sub>FR</sub> = 14.4kΩ (Note 3)                                                                  | 0.84  | 1        | 1.13  | N 41 1- |

| $f_{SW}$             | Oscillator frequency                   | R <sub>FR</sub> = 20kΩ (Note 3)                                                                    | 0.675 | 0.75     | 0.875 | MHz     |

| V <sub>FR/SYNC</sub> | FR/SYNC pin voltage                    | R <sub>FR</sub> = 15kΩ                                                                             |       | 1.0      |       | V       |

| f <sub>FR</sub>      | FR frequency range                     | (Note 2)                                                                                           | 200   |          | 1000  | kHz     |

| Synchron             | nization                               |                                                                                                    |       |          |       |         |

| $f_{SY}$             | Synchronized PWM frequency             | (Note 2)                                                                                           | 580   |          | 1000  | kHz     |

| t <sub>SY_OFF</sub>  | Synchronization input minimum off-time | (Note 2)                                                                                           | 150   |          |       | ns      |

| t <sub>SY_ON</sub>   | Synchronization input minimum on-time  | (Note 2)                                                                                           | 150   |          |       | ns      |

| V <sub>SY_H</sub>    | CVNC input logic veltage               | FR/SYNC pin, high level (Note 3)                                                                   | 2.0   |          |       | V       |

| V <sub>SY_L</sub>    | SYNC input logic voltage               | FR/SYNC pin, low level (Note 3)                                                                    |       |          | 0.4   | V       |

|                      | Protection (TSD)                       |                                                                                                    |       |          |       |         |

| T <sub>SD_TH</sub>   | Thermal shutdown threshold             | Temperature rising (Note 2)                                                                        |       | 165      |       | °C      |

| T <sub>SD_HY</sub>   | Thermal shutdown hysteresis            | (Note 2)                                                                                           |       | 20       |       | °C      |

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

$T_J$ = -40°C ~ +125°C,  $V_{CC}$ = 12V. Typical value is  $T_J$ = 25°C, unless otherwise specified.

| Symbol                | Parameter                                         | Condition                                                                                                                                                             | Min. | Тур.   | Max. | Unit                   |  |  |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------------------------|--|--|

| FAULTB Pin            |                                                   |                                                                                                                                                                       |      |        |      |                        |  |  |

| $V_{FAULT\_PD}$       | FAULTB pull-down voltage                          | I <sub>FAULTB</sub> = 1mA (Note 3)                                                                                                                                    |      |        | 0.5  | V                      |  |  |

| I <sub>FAULT_L</sub>  | FAULTB pin leakage current                        | V <sub>FAULTB</sub> = 5V                                                                                                                                              |      |        | 1    | μA                     |  |  |

| LED Curre             | ent Sinks                                         |                                                                                                                                                                       |      |        |      |                        |  |  |

| Err <sub>CH</sub>     | CHx accuracy                                      | I <sub>SET</sub> = 100μA (Note 3)                                                                                                                                     |      |        | 3    | %                      |  |  |

| ΔI <sub>CH</sub>      | CHx matching                                      | I <sub>SET</sub> = 100μA (Note 3)                                                                                                                                     |      |        | 1    | %                      |  |  |

| $V_{CH}$              | CHx regulation voltage                            | V <sub>CH1</sub> = V <sub>CH2</sub> = V <sub>CH3</sub> = V <sub>CH4</sub> ,<br>I <sub>SET</sub> = 100μA (Note 3)                                                      | 620  | 720    | 820  | mV                     |  |  |

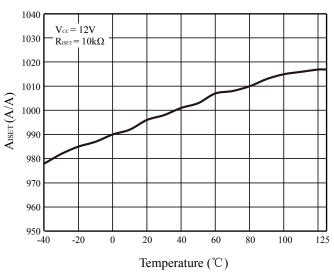

| $A_{ISET}$            | I <sub>SET</sub> to I <sub>CHx</sub> current gain | I <sub>SET</sub> = 100μA (Note 3)                                                                                                                                     | 1940 | 2000   | 2060 | A/A                    |  |  |

| $V_{SET}$             | ISET pin voltage                                  |                                                                                                                                                                       | 0.99 | 1.00   | 1.01 | V                      |  |  |

| I <sub>SET</sub>      | Allowable I <sub>SET</sub> current                | (Note 3)                                                                                                                                                              | 20   |        | 100  | μA                     |  |  |

| $V_{\text{CH\_S}}$    | V <sub>CH</sub> short detect                      | While LED sinks are in regulation, sensed from CHx pin to ground (Note 3)                                                                                             | 4.6  | 5.1    | 5.6  | V                      |  |  |

| I <sub>CH_SS</sub>    | Soft start CHx current                            | Current through each enabled CHx pin during soft start                                                                                                                |      | 24     |      | mA                     |  |  |

| t <sub>PWM_OFF</sub>  | Maximum PWM dimming until off-time (Note 2)       | Measured while $V_{\text{EN/PWM}} = \text{Iow}$ , during dimming control and internal references are powered-on (exceeding $t_{\text{PWM\_OFF}}$ results in shutdown) |      | 32,750 |      | f <sub>SW</sub> cycles |  |  |

| t <sub>PWM_ON</sub>   | Minimum PWM on-time                               | First cycle when powering-up device (Note 3)                                                                                                                          |      | 0.75   | 2    | μs                     |  |  |

| t <sub>PWMH_ON</sub>  | PWM high to LED-on delay                          | Time between PWM enable and LED current reaching 90% of maximum (Note 3)                                                                                              |      | 0.5    | 0.9  | μs                     |  |  |

| t <sub>PWML_OFF</sub> | PWM low to LED-off delay                          | Time between PWM enable going low and LED current reaching 10% of maximum (Note 3)                                                                                    |      | 0.9    | 1    | μs                     |  |  |

Note 1: For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing); positive current is defined as going into the node or pin (sinking).

Note 2: Ensured by design and characterization, not production tested.

Note 3: Indicates specifications guaranteed by design and characterization over the full operating temperature range with T<sub>A</sub> = T<sub>J</sub> = -40°C ~

Note 4: Minimum  $V_{CC}$ = 4.75V is only required at startup. After startup is completed, the IC is able to function down to  $V_{CC}$ = 4V.

#### TYPICAL PERFORMANCE CHARACTERISTICS

1.2  $V_{cc} = 12V$ 1.15  $R_{\text{FSET}}{=15k\Omega}$ 1.1 fsw (MHz) 1.05 0.95 0.9 0.85 0.8 -25 -10 20 35 50 110 125 -40 5 65 Temperature ( $^{\circ}$ C)

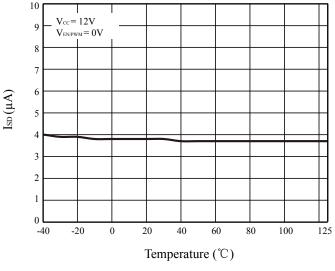

Figure 2 I<sub>SD</sub> vs. Temperature

Figure 3 f<sub>SW</sub> vs. Temperature

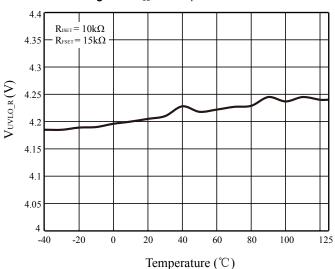

Figure 4  $V_{UVLO\_R}$  vs. Temperature

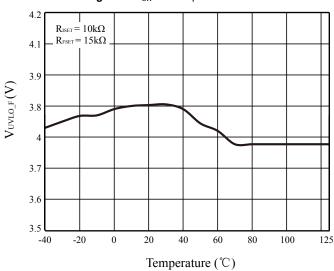

Figure 5 V<sub>UVLO\_F</sub> vs. Temperature

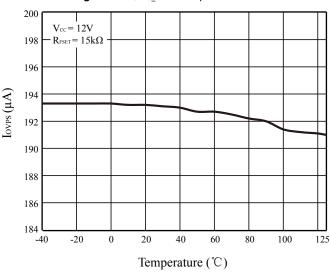

Figure 6  $I_{\text{OVPS}}$  vs. Temperature

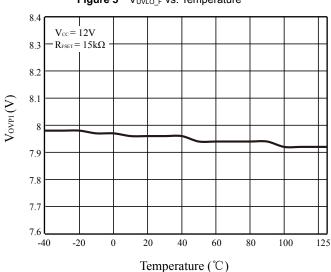

Figure 7  $V_{\text{OVP1}}$  vs. Temperature

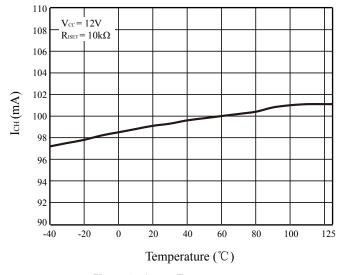

Figure 8 I<sub>CH</sub> vs. Temperature

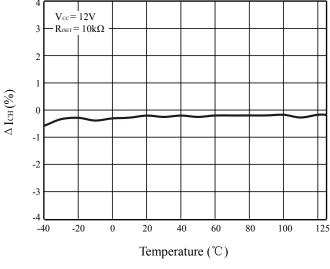

Figure 9 ΔI<sub>CH</sub> vs. Temperature

Figure 10 A<sub>ISET</sub> vs. Temperature

Figure 11 f<sub>SW</sub> vs. R<sub>FSET</sub>

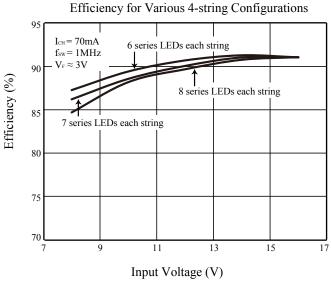

Figure 12 Efficiency vs. Voltage of String Configurations

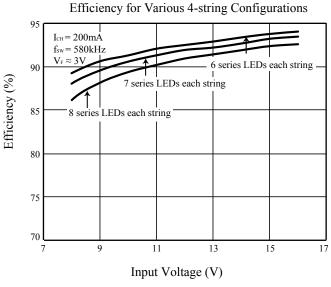

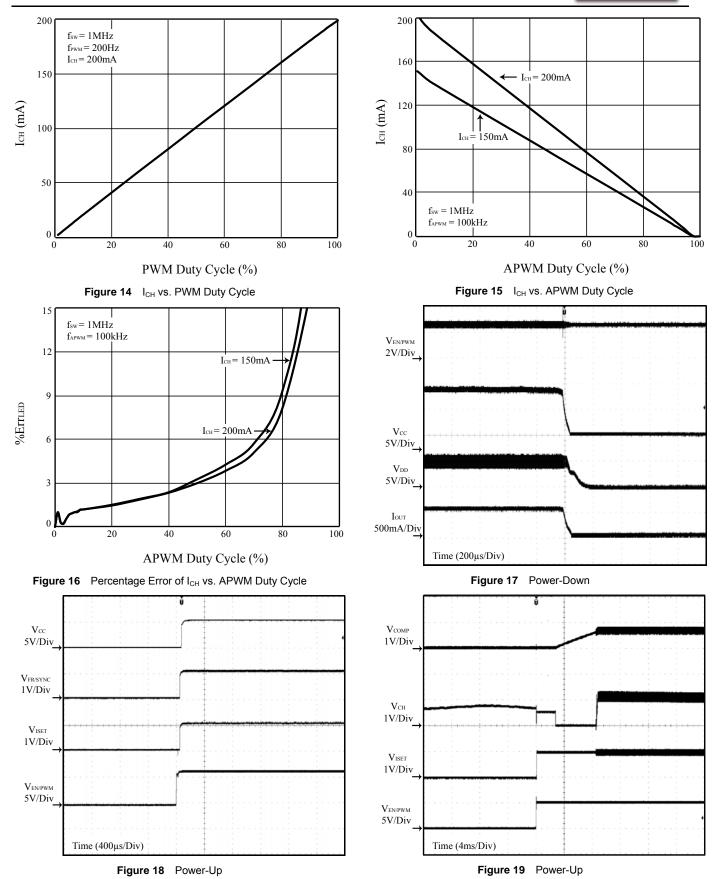

Figure 13 Efficiency vs. Voltage of String Configurations

Integrated Silicon Solution, Inc. – www.issi.com Rev. 0A, 09/08/2017

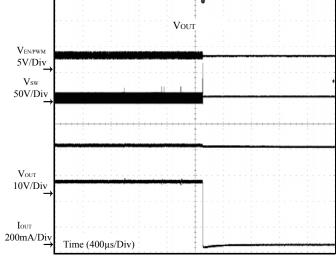

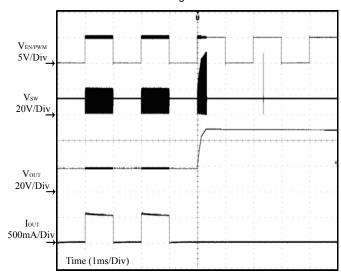

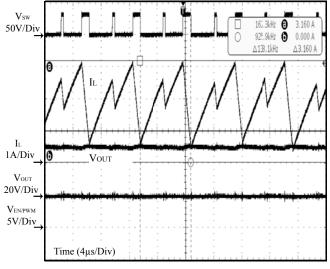

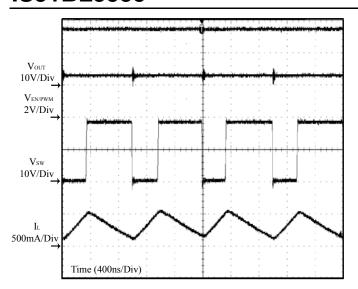

Figure 32 Signal Applied To The APWM Pin During PWM Dimming

Figure 33 OVP Protection When The IC Is Enabled During An Open Diode Condition

Figure 34 OVP Protection With Output Disconnect

Figure 35 OVP Protection With Open LED String

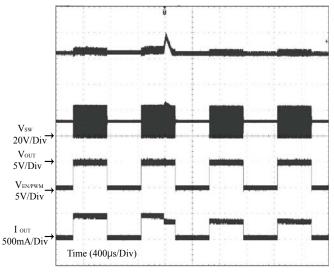

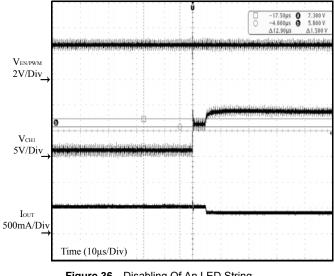

Figure 36 Disabling Of An LED String

Figure 37 Cycle-By-Cycle Current Limiting

Figure 38 Normal Operation

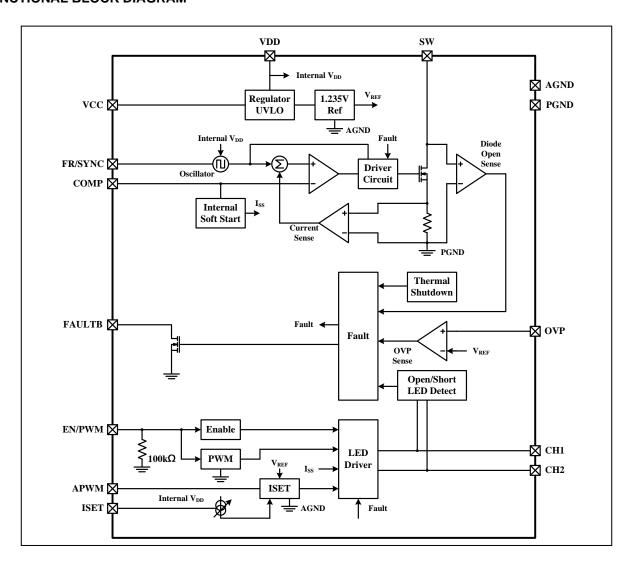

# **FUNCTIONAL BLOCK DIAGRAM**

#### **APPLICATION INFORMATION**

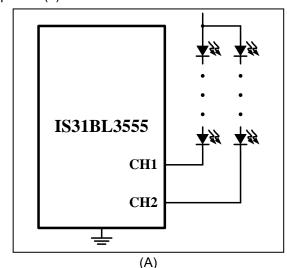

The IS31BL3555 is a highly integrated current-mode boost HBLED driver with integrated switching FET and two LED current sinks. It is designed to drive two LED strings of up to 12 white LEDs in series, with current up to 200mA per string. An adaptive headroom control feature automatically adjusts the output boost stage to the minimum voltage ( $V_{\text{OUT}}$ ) required to power the LED strings ( $V_{\text{STRx}}$ ). This is expressed by the following Equation (1):

$$V_{OUT} = Max(V_{STR1}, V_{STR2}) + V_{CH}$$

(1)

Where  $V_{\text{STRx}}$  is the voltage drop across LED strings 1 through 2, and  $V_{\text{CH}}$  is the headroom (regulation) voltage of the LED current sinks (typically 0.72V at the maximum LED current). The dynamic headroom control will adjust the VOUT to equal the sum of the highest LED string voltage plus the IS31BL3555 operating headroom voltage.

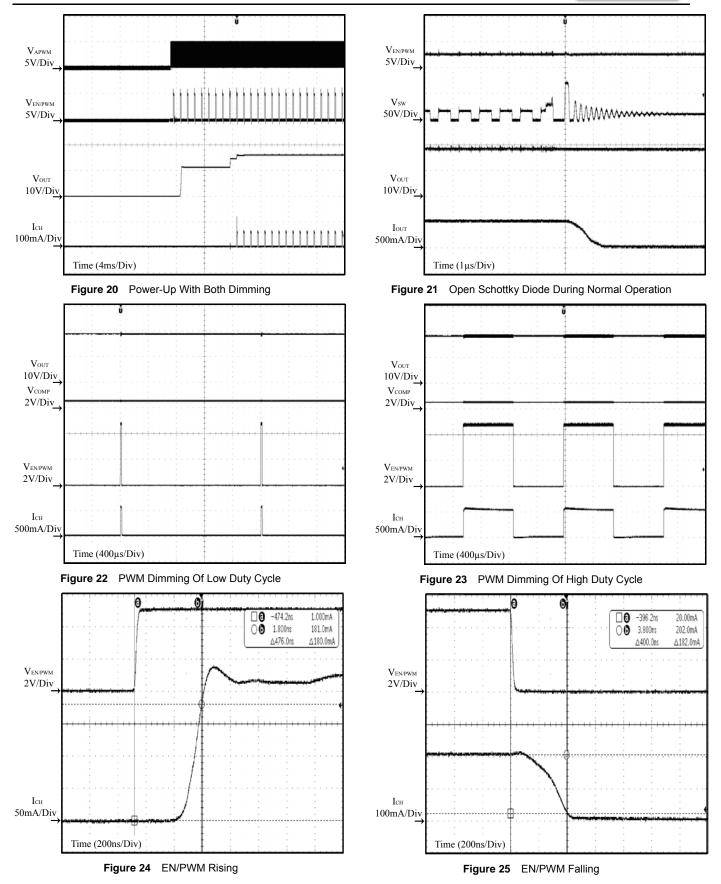

### **INITIAL POWER UP SEQUENCE**

The power-up sequence is shown in Figure 18. The IS31BL3555 integrates a UVLO/Regulator function which monitors the supply voltage level at the VCC input pin. The IS31BL3555 will power up only when the supply voltage is above the internal UVLO threshold level of 4.35V (max) and the EN/PWM pin is pulled high. During the power up sequence, the IS31BL3555 will check if any CHx pins are shorted to ground and/or are not used as shown in Figure 39.

Once any of the CHx pin voltage rises above 120mV, a delay of between 3000 and 4000 clock cycles must pass before pin status detection is enabled. Therefore the LED detection period will vary depending on the switching frequency, as shown in the following table:

| Switching Frequency (MHz) | Detection Time (ms) |

|---------------------------|---------------------|

| 1                         | 3 ~ 4               |

| 0.800                     | 3.75 ~ 5.0          |

| 0.600                     | 5.0 ~ 6.7           |

The CHx pin voltage thresholds used in detecting short/open LED conditions are as follows:

| CHx    | LED Pin Status  | Action                     |

|--------|-----------------|----------------------------|

| <35mV  | Short to ground | Power-up is halted         |

| <220mV | Not used        | LED removed from operation |

| >220mV | LED pin in use  | None                       |

As shown in Figure 39, any unused CHx pins should be connected with a  $1.54k\Omega$  resistor to ground. The CHx pin with a pull-down resistor will be ignored and

will not be used for adaptive headroom control in Equation (1).

Figure 39 Channel Select Setup: (A) Using All Two Channels And (B) Using Only CH1.

If any CHx short to ground ( $V_{\text{CHx}}$ <35mV) is detected, the IS31BL3555 will not soft start until the short condition is removed. This protects the LED strings from an uncontrolled amount of current at power up due to shorted CHx pins.

## **SOFT START**

When in soft start mode, the CHx pins will initially sink the soft start current ( $I_{CH\_SS}$ ). As the CHx pin voltage rises above 220mV, the IS31BL3555 will set the boost switch current limit to the  $I_{SW\_LIM1}$  level and proceed to increase the LED current to the level set by the  $I_{SET}$  resistor value. This is shown in Figure 27

### **ENABLING THE IC**

The IS31BL3555 will turn on when a logic high (>  $t_{PWM\_ON}$ ) on EN/PWM pin and the VCC voltage rises above 4.35V to clear the UVLO ( $V_{UVLO\_R}$ ) threshold.

A logic low on the EN/PWM pin will completely shut down the IS31BL3555. It will not power-up if the FR/SYNC pin is pulled low.

#### SWITCHING FREQUENCY SELECTION

A resistor connected to the FR/SYNC pin is used to set the boost regulator's switching frequency from 200kHz to 1MHz. Figure 11 shows the typical switching frequencies, in MHz, for resistor values, in k $\Omega$ .

$$R_{ESET} = 15 / f_{SW}$$

The FR/SYNC pin is clamped to a maximum switching frequency of 3.5MHz if a fault occurs during operation. It will shut down when the FR/SYNC pin is shorted to GND.

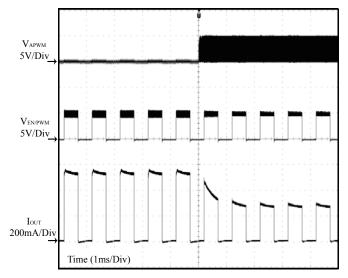

#### **SYNCHRONIZE**

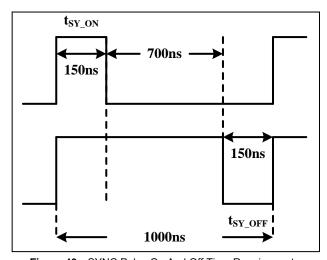

The FR/SYNC pin can be used as a synchronization input, allowing the IS31BL3555 to operate with an external clock in the range of 580kHz to 1MHz as long as it satisfies the 150ns requirements of  $t_{\rm SY\_ON}$  and  $t_{\rm SY\_OFF}$ . When an external synchronization clock is applied to the FR/SYNC pin, the internal oscillator is over-driven so that each switching cycle begins at the rising edge of external clock. The IS31BL3555 will not be enabled if the FR/SYNC pin is held low during power-up. Only when the FR/SYNC pin is tri-stated to allow the pin to rise, to about 1V, or when a synchronization clock is detected, will the IS31BL3555 try to power-up.

Figure 40 shows the timing for a synchronization clock into the IS31BL3555 at 1MHz. Thus any pulse with a duty cycle of 15% to 85% at 1MHz can be used to synchronize the IC.

Figure 40 SYNC Pulse On And Off Time Requirements

The SYNC pulse duty cycle ranges for selected switching frequencies are:

| SYNC Pulse Frequency(MHz) | Duty Cycle Range(%) |

|---------------------------|---------------------|

| 1                         | 15 ~ 85             |

| 0.800                     | 12 ~ 88             |

| 0.600                     | 9 ~ 91              |

If the clock is lost, the IC will revert to the preset switching frequency set by the  $R_{\text{FSET}}$  resistor. The IC will stop switching during this period for a maximum period of about  $7\mu s$  to allow the sync detection circuitry to switch over to the resistor preset switching frequency. Figure 28 shows the synchronized normal operation of the external sync signal and switching frequency. Figure 29 shows the switching frequency locking to the external sync signal. LED current does vary during the frequency changeover.

Keeping the FR/SYNC pin lower than 0.4V for greater than 7µs will effectively shut down the IS31BL3555. If the FR/SYNC pin is held low during power-up, the IC will not power-up. Normal operation is resumed when the FR/SYNC pin is released and rises above 1V which starts the soft-start sequence. The IC can be placed into a low-power mode by keeping the EN pin low for 32,750 clock cycles.

#### **SETTING LED CURRENT**

The  $I_{SET}$  pin is used to set the  $I_{LED}$  channel current from 40mA up to a maximum of 200mA. To adjust the  $I_{LED}$  current, the resistor,  $R_{ISET}$ , is selected according to the following Formula (2):

$$R_{ISET} = (1.000 \times 2000) / I_{LED}$$

(2)

Where  $I_{\text{LED}}$  is in Amps and  $R_{\text{ISET}}$  is in  $\Omega$ . This sets the maximum channel current, referred to as the peak current.

Sample standard  $R_{\text{ISET}}$  values with the corresponding  $I_{\text{LED}}$  current are as follows:

| Standard Closest Resistor, $R_{\text{ISET}}\left(k\Omega\right)$ | LED Current, I <sub>LED</sub> (mA) |

|------------------------------------------------------------------|------------------------------------|

| 10.0                                                             | 200                                |

| 25                                                               | 80                                 |

| 33.4                                                             | 60                                 |

#### **PWM DIMMING**

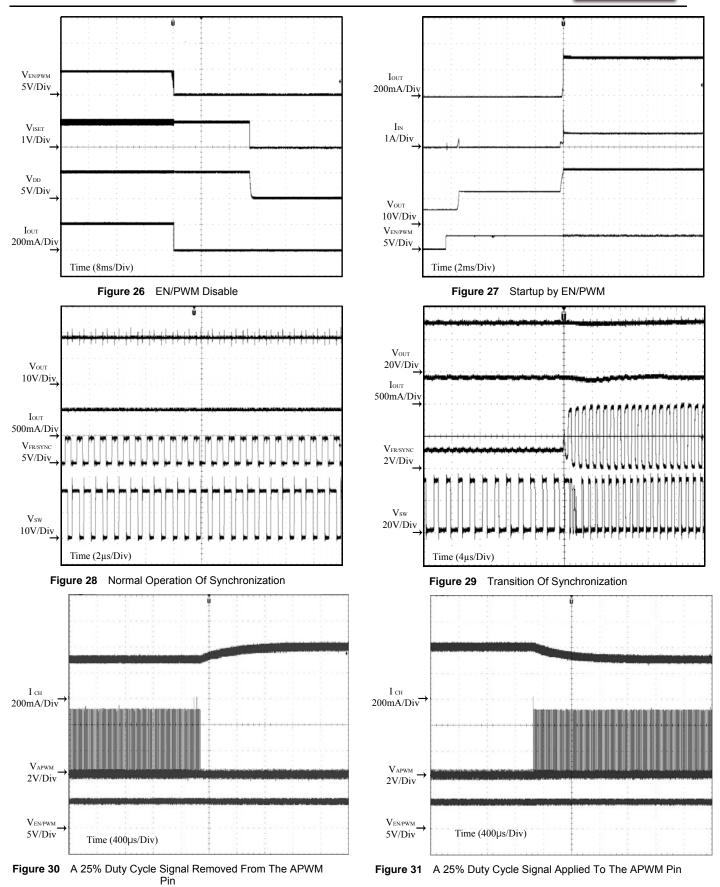

A PWM signal in the range of 200Hz ~ 1kHz applied to the EN/PWM pin will adjust the average LED current for all enabled channels. The PWM duty cycle sets the average LED current by turning on and off the current sinks. During the "high level" period of the PWM signal, the current sinks are turned ON at peak current level. During the "low level" period the current sinks are turned OFF and only critical internal circuits are kept active resulting in minimal power consumption. Figures 22 to 25 provide examples of PWM switching behavior.

PWM signal to LED current delay is less than 1µs typically, which allows greater accuracy at low PWM dimming duty cycles, as shown in Figure 14.

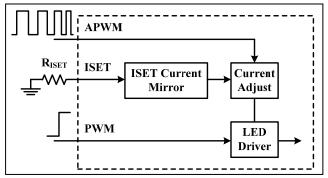

#### **APWM PIN**

As shown in Figure 41, the APWM pin is used to trim the LED peak current set by the  $R_{\rm ISET}$  resistor. The duty cycle of this 20kHz to 1MHz digital signal will adjust the internally  $I_{\rm SET}$  current. The duty cycle of this signal is inversely proportional to the percentage of current that is delivered to the LEDs (Shown in Figure 15). There is a several millisecond propagation delay between applying an APWM signal and the change in LED current peak current. This effect is shown in Figures 30~32.

The APWM pin should be connected to ground if it is not used.

Figure 41 Simplified Block Diagram Of The APWM And ISET Circuit

When using the APWM input to trim the LED current, the  $R_{\rm ISET}$  should selected for an LED current at least 5% higher than the desired peak current. The LED current is then trimmed down to the desired value. The trim down percentage corresponds to the APWM duty cycle. Therefore duty cycles between 30% and 60% will result in LED current trim from 30% and 60%. (Shown in Figure 16, Ich=200mA).

For example, a peak LED current of 80mA (set by  $R_{\rm ISET}$ ) would deliver 60mA of current per LED sink if an APWM signal is applied with a duty cycle of 25% (Figures 30 and 31).

Although the order in which APWM and the PWM signal are enabled does not matter, the APWM signal should be enable before the PWM signal when actively adjusting the IS31BL3555 to output a lower current. This is to prevent the light intensity from changing during power up of the IC. Figure 20 shows the sequence of applying APWM before the PWM signal during power-up to prevent inadvertent light intensity changes.

For the best APWM dimming accuracy it is recommended to use frequency ranges between 50 and 500kHz.

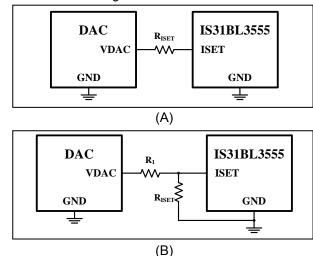

#### ANALOG DIMMING

The LED current can also be dimmed by using an external DAC or another voltage source applied either directly to the ground side of the R<sub>ISET</sub> resistor or through an external resistor to the ISET pin (Figure 42). For this type of dimming the I<sub>SET</sub> range  $20\mu A \sim 100\mu A$  will set the dimming limits.

**Figure 42** Simplified diagrams of voltage control of I<sub>LED</sub>: typical applications using a DAC to control I<sub>LED</sub> using a single resistor (upper), and dual resistors (lower).

$\bullet$  For Figure 42A, the I<sub>SET</sub> current is calculated by the following Formula (3). The LED can only be decreased from the peak current set by R<sub>ISET</sub>.

$$I_{SET} = \frac{V_{SET} - V_{DAC}}{R_{ISET}} \tag{3}$$

Where  $V_{SET}$  is the  $I_{SET}$  pin voltage (1V typ) and  $V_{DAC}$  is the DAC output voltage. The LED current is maximum value when the DAC voltage is 0V. Select  $R_{ISET}$  resistor so the  $I_{SET}$  current is in the range of  $20\mu A \sim 100\mu A$  to maintain stability of the internal gain amplifier.

• For the dual-resistor configuration (Figure 42B), the I<sub>SET</sub> current is calculated by the following Formula (4). The LED current can be increased or decreased.

$$I_{SET} = \frac{V_{SET}}{R_{ISET}} - \frac{V_{DAC} - V_{SET}}{R_{1}}$$

(4)

For this resistor circuit the LED current can be increased or decreased.by adjusting the DAC voltage higher or lower. The LED current can be made higher or lower than the current set by the R<sub>ISET</sub> resistor:

- □ V<sub>DAC</sub>= 1.000V; R<sub>ISET</sub> controls current output

- VDAC> 1.000V; the LED current is reduced

- □ V<sub>DAC</sub> < 1.000V; the LED current is increased

</p>

#### LED SHORT DETECT

The IS31BL3555 integrates an LED short-circuit protection circuit. If the voltage at any of the two channel pins exceeds a threshold of approximately  $V_{\text{CH\_S}}$  during normal operation, the corresponding string is turned off and is latched off (Figure 36). This is to prevent the IC from dissipating too much power by having a large voltage present on a CHx pin.

To prevent false tripping of an LED short event, the IS31BL3555 rechecks the disabled LED string every time the PWM signal goes high. This enables self-correction for an intermittent LED pin short.

#### **OVERVOLTAGE PROTECTION**

The IS31BL3555 integrates an OVP circuit and open Schottky diode protection to prevent system damage should the output voltage become excessive. The OVP protection default level is 8.1V and can be increased to 53V by connecting a resistor  $R_{\text{OVP}}$  from the OVP pin to VOUT. When the current into the OVP pin exceeds 199 $\mu$ A (typical), the OVP comparator goes low and stops the switching.

The following Equation (5) can be used to determine the resistance for setting the OVP level:

$$R_{OVP} = \frac{V_{OVP\_OUT} - V_{OVP1}}{I_{OVPS}} \tag{5}$$

Where:  $V_{\text{OVP\_OUT}}$  is the target overvoltage level,  $R_{\text{OVP}}$  is the value of the external resistor, in  $\Omega$ ,  $V_{\text{OVP1}}$  is the pin OVP threshold found in the Electrical Characteristics Table, and  $I_{\text{OVPS}}$  is the sense current into the OVP pin.

The two most common reasons for an OVP condition are: a disconnected output, and an open LED string. Examples of these are provided in Figures 34 and 35.

Figure 34 shows when the output of the IS31BL3555 is disconnected from the load during normal operation. The output voltage  $V_{\text{OUT}}$  immediately increases to the OVP voltage level which then stops the switching to prevent damage to the IC. Switching will resume once  $V_{\text{OUT}}$  discharges to below the OVP threshold and will stop if  $V_{\text{OUT}}$  increases above the OVP threshold.

Figure 35 displays a typical OVP event caused by an open LED string. After the OVP condition is detected, the IS31BL3555 stops switching, the open LED string is disabled and  $V_{\text{OUT}}$  begins to drop. The switching will resume and the IS31BL3555 continues with normal operation.

IS31BL3555 also has secondary overvoltage protection for the internal switch (SW pin). In the event of an open schottky diode the voltage on the SW

pin  $(V_{SW})$  may exceed 60V, which is above the device safe operating voltage rating. Under this condition the secondary overvoltage protection will disable the IS31BL3555 and remain in a latched off condition. To clear the latch and resume operation, the IS31BL3555 must be shut down by either lowering the supply voltage below the UVLO threshold or by driving the EN/PWM pin as shown in Figure 21.

If the IS31BL3555 is enabled with an open diode condition, it will go through all its initial LED detection procedure and then try to enable the switcher, at which time the open diode is detected the device shuts down as shown in Figure 33.

#### **INPUT UVLO**

The IS31BL3555 will be enabled when  $V_{\rm CC}$  and  $V_{\rm SENSE}$  rise above the  $V_{\rm UVLO\_R}$  threshold. It will be disabled when  $V_{\rm CC}$  falls below the  $V_{\rm UVLO\_F}$  threshold for more than 50 $\mu$ s. This small delay is used to avoid shutting down because of momentary glitches in the input power supply. It will shut down if  $V_{\rm CC}$  falls below 4.35V, (see Figure 17).

### **VDD**

The IS31BL3555 has an internal LDO to support internal circuits and provide a pull-up voltage (3.5V typ) for the FAULTB pin. The current is limited to <2mA and a capacitor  $C_{VDD}$  ( $\geq 1\mu F$ ) should be connected to the VDD pin.

### **SHUTDOWN**

The IS31BL3555 enters a shutdown mode and clears all internal fault registers when the EN/PWM pin is pulled low for more than  $t_{PWM\_OFF}$  (32,750 clock cycles). With a 1MHz clock frequency, it will take approximately 33ms to shut down (Figure 26). When the IS31BL3555 is shut down, all current sources are disabled. A high level on the EN/PWM will remove the shutdown condition. For a faster shutdown, the FR/SYNC pin can be pulled low.

### **FAULT PROTECTION DURING OPERATION**

The IS31BL3555 constantly monitors the state of the system in order to determine whether there is any fault condition. The response to a triggered fault condition is summarized in the Fault Mode Table 1.

The device can detect these fault conditions:

- Open/short LED string

- FSET or ISET pins shorted to ground

- Open boost schottky diode

- Over temperature (OTP)

# **TABLE 1 FAULT MODE**

| Fault Name                                                                    | Туре         | Active              | Flag | Description                                                                                                                                                                                                                                                                                          | Boost                    | Sink<br>Driver                           |

|-------------------------------------------------------------------------------|--------------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------|

| Primary switch<br>overcurrent protection<br>(Cycle-by-cycle current<br>limit) | Auto-restart | Always              | No   | This fault condition is triggered by the cycle-by-cycle current limit, I <sub>SW_LIM1</sub>                                                                                                                                                                                                          | Off for a single cycle   | On                                       |

| Secondary OVP                                                                 | Latched      | Always              | Yes  | Secondary overvoltage protection is used for open diode detection. When diode D1 opens, the SW pin voltage will increase until $V_{\text{OVP2}}$ is reached. This fault latches the IC and the fault flag is set. To re-enable the part the EN/PWM pin must be pulled low for 32,750 clock cycles.   | Off                      | Off                                      |

| LED pin short protection                                                      | Auto-restart | Startup             | No   | This fault prevents the device from starting-up if either of the CHx pins are shorted. The device stops soft-start from starting while either of the CHx pins are determined to be shorted. After the short is removed, soft-start is allowed to start.                                              | Off                      | Off                                      |

| LED pin open                                                                  | Auto-restart | Normal<br>Operation | No   | When a CHx pin is open the device will determine which LED pin is open by increasing the output voltage until OVP is reached. Any LED string not in regulation will be turned off. The device will then go back to normal operation by reducing the output voltage to the appropriate voltage level. | On                       | Off for open pins. On for all others.    |

| ISET short protection                                                         | Auto-restart | Always              | No   | This fault occurs when the ISET current goes above 150% of the maximum current. The boost will stop switching and the IC will disable the LED sinks until the fault is removed. When the fault is removed the IC will try to regulate to the preset LED current.                                     | Off                      | Off                                      |

| FR/SYNC short protection                                                      | Auto-restart | Always              | Yes  | Fault occurs when the FR/SYNC current goes above the protection threshold, about 256µA. The boost will stop switching and the IC will disable the LED sinks until the fault is removed. When the fault is removed the IC will try to restart with soft-start.                                        | Off                      | Off                                      |

| Overvoltage protection                                                        | Auto-restart | Always              | No   | Fault occurs when OVP pin exceeds V <sub>OVPS</sub> threshold. The IC will immediately stop switching to try to reduce the output voltage. If the output voltage decreases then the IC will restart switching to regulate the output voltage.                                                        | Stop during<br>OVP event | On                                       |

| LED short protection                                                          | Auto-restart | Always              | No   | Fault occurs when the LED pin voltage exceeds V <sub>CH_S</sub> . When the LED short protection is detected the LED string that is above the threshold will be removed from operation.                                                                                                               | On                       | Off for shorted pins. On for all others. |

| Over temperature protection                                                   | Auto-restart | Always              | No   | Fault occurs when the die temperature exceeds the over temperature threshold, 165°C.                                                                                                                                                                                                                 | Off                      | Off                                      |

| VCC UVLO                                                                      | Auto-restart | Always              | No   | Fault occurs when $V_{\text{CC}}$ drops below $V_{\text{UVLO}}$ , 3.9V maximum. This fault resets all latched faults.                                                                                                                                                                                | Off                      | Off                                      |

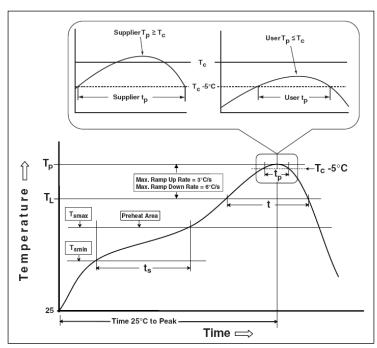

# **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                           | Pb-Free Assembly                 |

|-------------------------------------------------------------------------------------------|----------------------------------|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |

Figure 43 Classification Profile

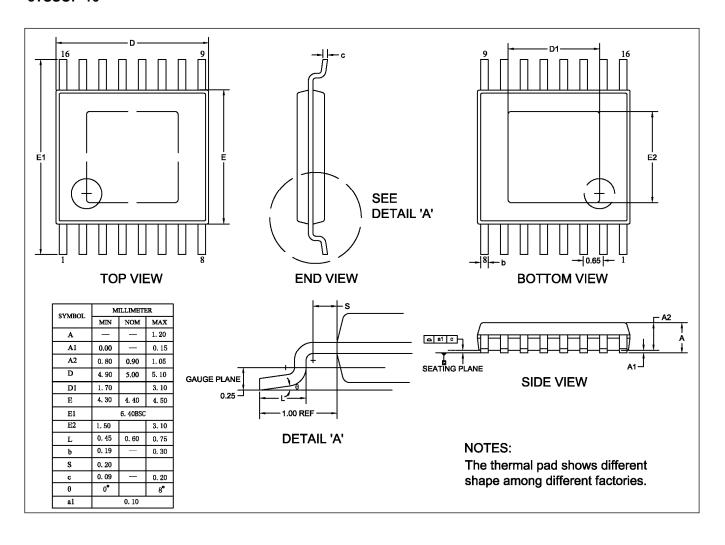

## **PACKAGE INFORMATION**

## eTSSOP-16

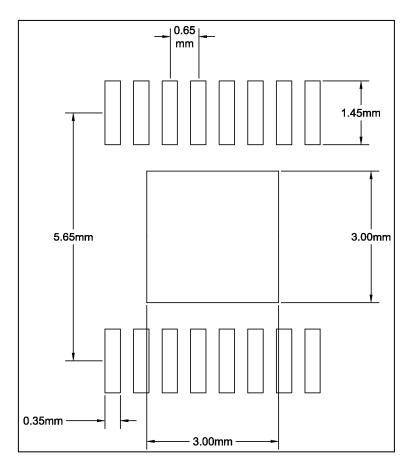

## **RECOMMENDED LAND PATTERN**

### Note:

- 1. Land pattern complies to IPC-7351.

- 2. All dimensions in MM.

- 3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. User's board manufacturing specs), user must determine suitability for use.

# **REVISION HISTORY**

| Revision | Detail Information | Date       |

|----------|--------------------|------------|

| 0A       | Initial release    | 2017.09.08 |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ISSI:

IS31BL3555-ZLS4 IS31BL3555-ZLS4-TR