# 2.5V to 5.5V, 5A Reversible Buck/Boost Regulator for Backup Applications

**MAX38890**

## **Product Highlights**

- 2.5V to 5.5V System Output Voltage Range

- 0.5V to 5.5V Supercapacitor Voltage Range

- ±1% Threshold Accuracy

- 2.5% Hysteresis between Backup and Charging

- 1A to 5A Peak Inductor Current Limit

- Peak Inductor Current Is Pin-Programmable over 1A to 5A through External Resistor

- 94% Peak Efficiency, Charging or Discharging Mode

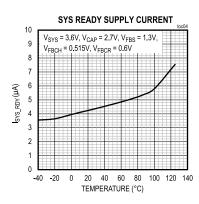

- 4µA Quiescent Current in Ready State

- After Supercapacitor Is Charged, Draws only 4µA of Quiescent Current

- Ready and Backup State Outputs

- RDY and BKB Flags Provide Real-Time Status to System

- 3mm x 3mm, 16-Pin TQFN Package

## **Key Applications**

- Handheld Industrial Equipment

- Portable Devices/Computers with Removable Battery

- Industrial Sensor and Actuators

- Aftermarket Automotive Tracking

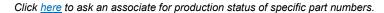

# **Pin Configuration**

Ordering Information appears at end of data sheet.

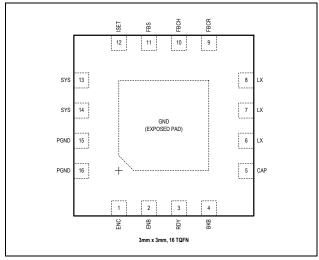

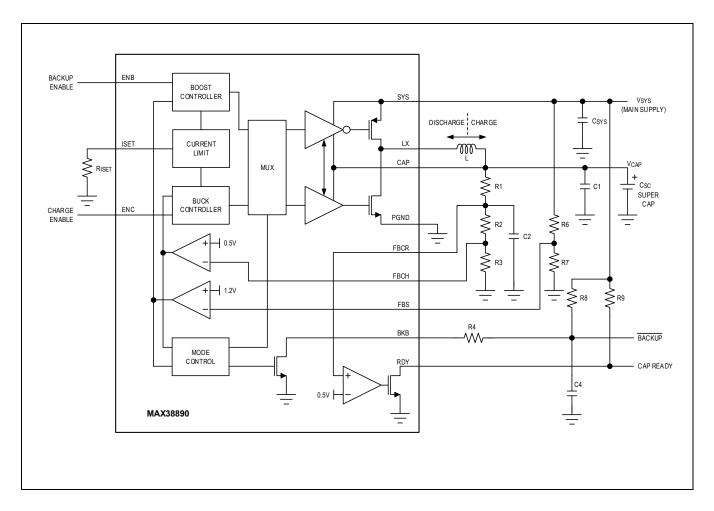

# **Simplified Application Diagram**

19-101564; Rev 0; 11/22

# 2.5V to 5.5V, 5A Reversible Buck/Boost Regulator for Backup Applications

# **Absolute Maximum Ratings**

| CAP, ENB, ENC, LX to GND $\!.$ | 0.3V to +6V                      |

|--------------------------------|----------------------------------|

| SYS, BKB, RDY to GND           | 0.3V to +6V                      |

| FBCH, FBCR to GND              | 0.3V to CAP + 0.3V               |

| FBS, ISET to GND               | 0.3V to SYS + 0.3V               |

| PGND to GND                    | 0.3V to +0.3V                    |

| Continuous Power Dissipatio    | n ( $T_A = +70^{\circ}C$ , TQFN, |

| derate 23.1mW/°C above +70     | 0°C)1847.6mW                     |

| Operating Temperature Range       | 40°C to +125°C       |

|-----------------------------------|----------------------|

| Storage Temperature Range         | 65°C to +150°C       |

| Maximum Junction Temperature      | +150°C               |

| Lead Temperature (soldering, 10s) | +300°C               |

| Soldering Temperature (reflow)    | +260°C               |

| LX RMS Current                    | ±5.0A <sub>RMS</sub> |

| Output Short-Circuit Duration     | Continuous           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### **TQFN**

| Package Code                           | T1633+5C       |  |

|----------------------------------------|----------------|--|

| Outline Number                         | <u>21-0136</u> |  |

| Land Pattern Number                    | <u>90-0032</u> |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 43.3°C/W       |  |

| Junction to Case (θ <sub>JC</sub> )    | 4°C/W          |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

$(V_{SYS} = 3.7V, V_{CAP} = 2.8V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C \text{ (typical values at } T_J = +25^{\circ}C), \text{ circuit of } \frac{Figure 1}{C}, \text{ unless otherwise specified.)}$

| PARAMETER                        | SYMBOL               | CONDITIONS                                                                         |                                                        | MIN   | TYP   | MAX   | UNITS |

|----------------------------------|----------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| SYS Voltage Range                | V <sub>SYS</sub>     | Guaranteed by LX peak backup current and SYS shutdown current                      |                                                        | 2.5   |       | 5.5   | V     |

| CAP Voltage Range                | V <sub>CAP</sub>     | -                                                                                  | Guaranteed by maximum on-time and CAP shutdown current |       |       | 5.5   | V     |

| SYS Shutdown                     | I <sub>SYS_SD</sub>  | $V_{SYS} = 5.5V$ ,                                                                 | T <sub>A</sub> = +25°C                                 |       | 0.010 | 1     | μА    |

| Current                          | .313_30              | $V_{ENC} = V_{ENB} = 0V$                                                           | T <sub>A</sub> = +125°C                                |       | 0.46  |       |       |

| SYS Ready Supply                 | _                    | V <sub>FBS</sub> = 1.3V,                                                           | T <sub>A</sub> = +25°C                                 |       | 4.5   | 8     |       |

| Current                          | Isys_RDY             | $V_{FBCH} = 0.515V,$<br>$V_{FBCR} = 0.6V$                                          | T <sub>A</sub> = +125°C                                |       | 8     |       | μA    |

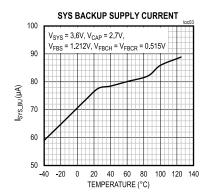

| SYS Backup Supply<br>Current     | I <sub>SYS_BU</sub>  | $V_{FBS}$ = 1.212V, $V_{FB}$<br>$V_{FBCR}$ = 0.6V                                  | CH = 0.5V,                                             |       | 75    | 150   | μA    |

| CAP Shutdown                     | I <sub>CAP_SD</sub>  | V <sub>CAP</sub> = 5.5V,                                                           | T <sub>A</sub> = +25°C                                 |       | 0.01  | 1     | μA    |

| Current                          | ·CAF_3D              | V <sub>ENC</sub> = V <sub>ENB</sub> = 0V                                           | T <sub>A</sub> = +125°C                                |       | 0.2   |       | μΛ    |

| System Undervoltage<br>Threshold | V <sub>UVLOF</sub>   | V <sub>SYS</sub> falling, 100mV<br>V <sub>CAP</sub> = 0V                           | typical hysteresis,                                    | 2.1   | 2.2   | 2.3   | V     |

| FBS Backup Voltage               | V <sub>FBS_BU</sub>  | V <sub>FBS</sub> rising, when di                                                   | scharging stops                                        | 1.188 | 1.2   | 1.212 | V     |

| FBS Charging<br>Threshold        | V <sub>FBS_CHG</sub> | From V <sub>FBS</sub> backup voltage, when charging begins                         |                                                        | 2     | 2.5   | 3     | %     |

| FBCH Threshold                   | V <sub>TH_FBCH</sub> | V <sub>FBCH</sub> rising, when charging stops;<br>10mV typical hysteresis          |                                                        | 0.495 | 0.5   | 0.505 | V     |

| FBCR Threshold                   | V <sub>TH_FBCR</sub> | V <sub>FBCR</sub> rising, when RDY releases;<br>10mV typical hysteresis            |                                                        | 0.495 | 0.5   | 0.505 | V     |

| V <sub>IL</sub>                  |                      | V <sub>FBS</sub> = 1.3V,<br>V <sub>FBCH</sub> = 0.4V,<br>when LX switching         | V <sub>ENC</sub> rising                                | 600   | 850   |       | \/    |

| ENC Input Threshold              | V <sub>IH</sub>      | $V_{FBS}$ = 1.3V,<br>$V_{FBCH}$ = 0.4V,<br>when LX switching                       | V <sub>ENC</sub> falling                               |       | 950   | 1200  | mV    |

| ENB Input Threshold              | V <sub>IL</sub>      | V <sub>FBS</sub> = 1.1V,<br>V <sub>FBCH</sub> = 0.4V,<br>when LX switching         | V <sub>ENB</sub> rising                                | 600   | 850   |       | mV    |

| END IIIput Tilleshold            | V <sub>IH</sub>      | V <sub>FBS</sub> = 1.1V,<br>V <sub>FBCH</sub> = 0.4V,<br>when LX switching         | V <sub>ENB</sub> falling                               |       | 950   | 1200  | IIIV  |

| ISET Resistor Range              | R <sub>ISET</sub>    | Guaranteed by LX                                                                   | Guaranteed by LX peak current limits                   |       |       | 100   | kΩ    |

| LX Switching<br>Frequency        | F <sub>SW</sub>      | V <sub>CAP</sub> = 1.5V, I <sub>SYS</sub> = 1A                                     |                                                        |       | 1.2   |       | MHz   |

| LX Peak Back-Up                  | I <sub>LX_BU</sub>   | Circuit of Figure 1,<br>V <sub>CAP</sub> = 2V, V <sub>SYS</sub><br>= 2.5V (Note 1) | R <sub>ISET</sub> = 20kΩ                               | 4     | 5     | 6     | A     |

| Current Limit                    | I <sub>LX_BU</sub>   | Circuit of Figure 1,<br>V <sub>CAP</sub> = 2V, V <sub>SYS</sub><br>= 2.5V (Note 1) | R <sub>ISET</sub> = 100kΩ                              |       | 1     |       |       |

$(V_{SYS} = 3.7V, V_{CAP} = 2.8V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C \text{ (typical values at } T_J = +25^{\circ}C), \text{ circuit of } \frac{Figure 1}{C}, \text{ unless otherwise specified.)}$

| PARAMETER                            | SYMBOL                                   | COND                                                                            | ITIONS                    | MIN  | TYP   | MAX  | UNITS |

|--------------------------------------|------------------------------------------|---------------------------------------------------------------------------------|---------------------------|------|-------|------|-------|

| LX Peak Charge                       |                                          | Circuit of Figure 1,                                                            | $R_{ISET} = 20k\Omega$    | 4    | 5     | 6    |       |

| Current Limit (Note 1)               | I <sub>LX_CHG</sub>                      | $V_{SYS} = 3.7V,$<br>$V_{CAP} = 2V$                                             | R <sub>ISET</sub> = 100kΩ |      | 1     |      | A     |

| Feedback Input Bias                  | I <sub>FBS</sub> , I <sub>FBCH</sub> ,   | V <sub>FBS</sub> = 1.2V                                                         | T <sub>A</sub> = +25°C    | -0.1 | 0.01  | +0.1 | μА    |

| Current                              | I <sub>FBCR</sub>                        | $V_{FBCH} = V_{FBCR} = 0.5V$                                                    | T <sub>A</sub> = +125°C   |      | 0.01  |      |       |

| Enable Input Leakage                 | I <sub>ENC</sub> , I <sub>ENB</sub>      | 0V < V <sub>ENC</sub> , V <sub>ENB</sub>                                        | T <sub>A</sub> = +25°C    | -1   | 0.004 | 1    | μА    |

| Current                              | 'ENC, 'ENB                               | < 5.5V                                                                          | T <sub>A</sub> = +125°C   |      | 0.01  |      |       |

| LX Low-Side FET<br>Resistance        | R <sub>LOW</sub>                         | V <sub>LX</sub> switched to 0V                                                  |                           |      | 42    | 84   | mΩ    |

| LX High-Side FET<br>Resistance       | R <sub>HIGH</sub>                        | V <sub>LX</sub> switched to V <sub>SY</sub>                                     | 'S                        |      | 57    | 114  | mΩ    |

|                                      |                                          | V <sub>ENC</sub> = V <sub>ENB</sub> =                                           | T <sub>A</sub> = +25°C    | -1   | 0.01  | 1    |       |

| LX Leakage Current                   |                                          | $0V, V_{SYS} = 5.5V,$<br>$V_{LX} = 0V \text{ to } 5.5V$                         | T <sub>A</sub> = +125°C   |      | 0.26  |      | μA    |

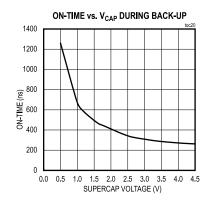

|                                      | ,                                        | Typical                                                                         | V <sub>CAP</sub> = 2V     | 320  | 400   | 480  | ns    |

| Maximum On-Time                      | t <sub>ON</sub>                          | Application Circuit, V <sub>SYS</sub> = 2.9V                                    | V <sub>CAP</sub> = 1.2V   |      | 570   |      |       |

| Minimum Off-Time                     | t <sub>OFF</sub>                         | Backup mode, V <sub>FBS</sub>                                                   | = 1.164V                  | 80   | 100   | 120  | ns    |

| Maximum Duty Cycle                   | Duty <sub>MAX</sub>                      | V <sub>CAP</sub> = 0.5V                                                         |                           | 90   | 95    |      | %     |

| Overtemperature<br>Lockout Threshold | T <sub>OTLO</sub>                        | T <sub>J</sub> rising, 15°C typical hysteresis                                  |                           |      | 165   |      | °C    |

| Logic Output Leakage                 | I <sub>BKB_H</sub>                       | $V_{BKB} = 5.5V,$<br>$V_{RDY} = 5.5V$                                           | T <sub>A</sub> = +25°C    | -1   | 0.001 | +1   |       |

| High                                 | I <sub>RDY_H</sub>                       | V <sub>BKB</sub> = 5.5V,<br>V <sub>RDY</sub> = 5.5V                             | T <sub>A</sub> = +125°C   |      | 0.01  |      | μΑ    |

| Logic Output Voltage<br>Low          | V <sub>BKB_L</sub><br>V <sub>RDY_L</sub> | I <sub>BKB</sub> = 10mA, I <sub>RDY</sub> = 10mA                                |                           |      | 0.1   | 0.4  | V     |

| High-Side FET Zero-<br>Crossing      | I <sub>ZXP</sub>                         | Circuit of Figure 1, V <sub>SYS</sub> = 2.9V,<br>V <sub>CAP</sub> = 2V (Note 1) |                           |      | 60    |      | mA    |

| Low-Side FET Zero-<br>Crossing       | I <sub>ZXN</sub>                         | Circuit of Figure 1, V <sub>SYS</sub> = 3.7V,<br>V <sub>CAP</sub> = 2V (Note 1) |                           |      | 180   |      | mA    |

**Note 1:** DC measurement, actual inductor current accuracy in the circuit is affected by the propagation delay time.

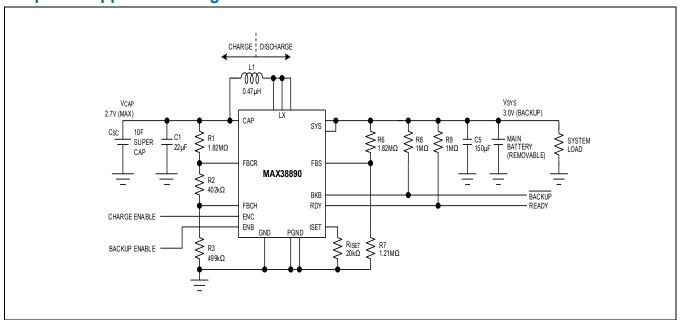

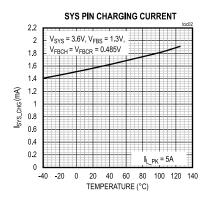

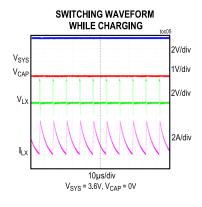

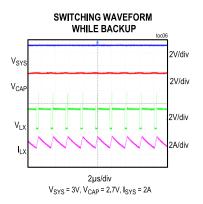

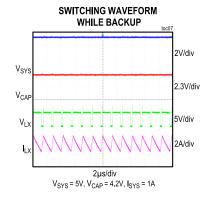

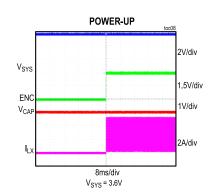

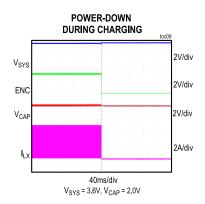

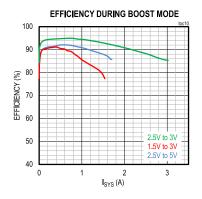

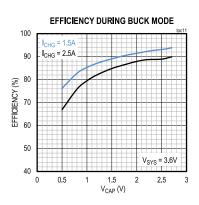

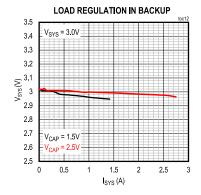

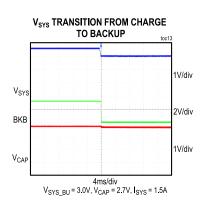

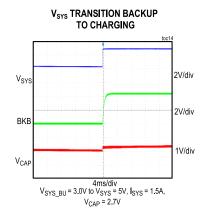

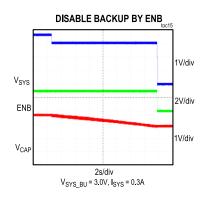

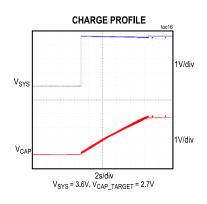

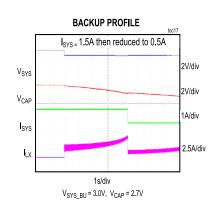

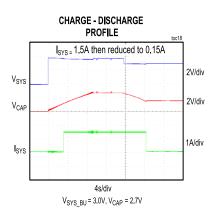

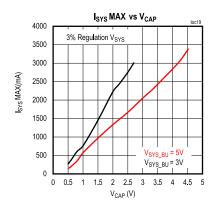

# **Typical Operating Characteristics**

$(V_{SYS} = 3.6V, V_{CAP} = 2.7V, C_{SYS} = 150 \mu F, C_{CAP} = 22 \mu F + 10 F, L = 0.47 \mu H, unless otherwise noted.)$

$(V_{SYS} = 3.6V, V_{CAP} = 2.7V, C_{SYS} = 150 \mu F, C_{CAP} = 22 \mu F + 10 F, L = 0.47 \mu H, unless otherwise noted.)$

$(V_{SYS} = 3.6V, V_{CAP} = 2.7V, C_{SYS} = 150 \mu F, C_{CAP} = 22 \mu F + 10 F, L = 0.47 \mu H, unless otherwise noted.)$

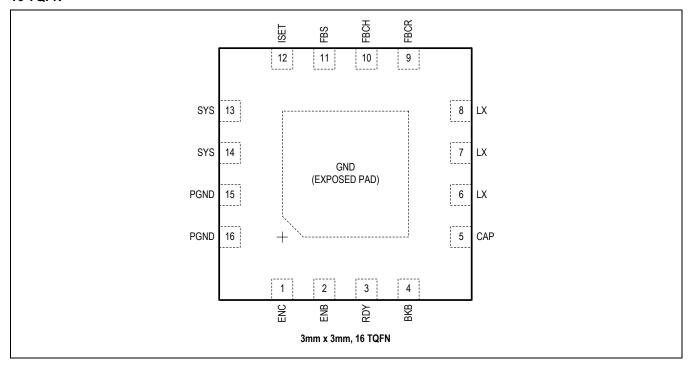

# **Pin Configuration**

#### **16 TQFN**

# **Pin Descriptions**

| PIN     | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ENC  | Charger Enable Input. Drive this pin high to enable charging of the supercapacitor while V <sub>SYS</sub> is above the charging threshold. Drive this pin low to disable charging. If not driven, tie this pin to the SYS rail.                                                                                                                                               |

| 2       | ENB  | Backup Enable Input. Drive this pin high to enable system backup when $V_{SYS}$ drops below the backup threshold. Drive this pin low to disable backup. If not driven, tie this pin to the SYS rail.                                                                                                                                                                          |

| 3       | RDY  | Ready Status Pin. Connect a pullup resistor from RDY to a logic supply. $V_{RDY}$ will be pulled low when $V_{FBCR}$ is below 0.5V and released when it is above 0.5V. $V_{RDY}$ is pulled low when $V_{ENC}$ and $V_{ENB}$ are both low.                                                                                                                                     |

| 4       | ВКВ  | Backup Status Pin. Connect a pullup resistor from BKB to a logic supply. $V_{BKB}$ will be pulled low when $V_{FBS}$ is regulating at 1.2V and released when it is above 1.23V. $V_{BKB}$ is released high when $V_{ENC}$ and $V_{ENB}$ are both low. It is recommeded to have an RC filter from BKB to ground as shown in <u>Figure 1</u> for smooth transition of BKB flag. |

| 5       | CAP  | Supercapacitor. Connect to a supercapacitor rated between 0.8V to 5V. Put a high-frequency capacitor of 22µF close to the CAP pin.                                                                                                                                                                                                                                            |

| 6, 7, 8 | LX   | Inductor Switching Node. Connect a 0.47µH inductor from LX to CAP. Keep this switching node separated from feedback signal nodes FBS, FBCH, and FBCR as much as possible.                                                                                                                                                                                                     |

| 9       | FBCR | Supercapacitor Ready Input. RDY will go high when $V_{FBCR}$ reaches 0.5V. It is recommended to place 0.47 $\mu$ F capacitor from FBCR to ground for smooth transition of the RDY flag.                                                                                                                                                                                       |

| 10      | FBCH | Supercapacitor Feedback Input. Connect a resistor-divider from CAP to FBCH to GND to set the supercapacitor maximum charging voltage.                                                                                                                                                                                                                                         |

| 11      | FBS  | System Feedback Input. Connect a resistor-divider from SYS to FBS to GND to set the system backup operating voltage. When V <sub>FBS</sub> is >102.5% of V <sub>FBS_BU</sub> , the supercapacitor will be charged from SYS.                                                                                                                                                   |

| 12      | ISET | Charge/Discharge Current Select. During charging, the average supercapacitor current ( $I_{CAP\_CHG}$ ) is set to $I_{CAP\_CHG}$ = 2.5A x ( $20k\Omega/R_{ISET}$ ). During backup, $V_{SYS}$ is regulated through the boost regulator with a peak inductor current of $I_{LX\_BU}$ = 5A x ( $20k\Omega/R_{ISET}$ )                                                            |

| 13, 14  | SYS  | System Supply. Connect to the system supply and bypass with 2x47µF and 2x22µF ceramic capacitors to PGND. In addition, place a high-frequency filter capacitor of 1µF close to the part across the SYS and PGND pins.                                                                                                                                                         |

| 15, 16  | PGND | Power Ground.                                                                                                                                                                                                                                                                                                                                                                 |

| EP      | GND  | Analog Ground. Connect the exposed pad to the ground plane with excellent thermal conduction to ambient temperature to avoid overtemperature.                                                                                                                                                                                                                                 |

## **Functional Diagram**

## **Detailed Description**

The MAX38890 is a flexible storage capacitor or capacitor bank backup regulator transferring power efficiently between a storage element and a system supply rail.

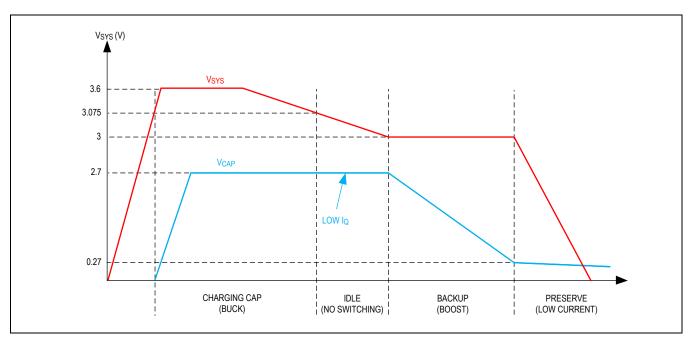

When the main supply is present and its voltage is above the minimum threshold system supply voltage, the regulator operates in charging mode and charges the storage element with a maximum 5A peak, 2.5A average inductor current. Once the storage element is charged, the circuit draws only  $4\mu$ A of current while maintaining the storage element in its ready state. The supercapacitor needs to be fully charged to enable backup operation.

When the main supply is removed, the regulator prevents the system from dropping below the set system backup operating voltage, boosting the supercapacitor voltage to a regulated  $V_{SYS}$  by discharging the storage element with a maximum 5A peak inductor current. During this backup mode of operation, the MAX38890 utilizes an adaptive on-time, current-limited, pulse-frequency-modulation (PFM) control scheme. Once the MAX38890 is in backup mode, the BKB flag is low.

The external pins allow various settings such as maximum supercapacitor voltage, system backup voltage (V<sub>SYS</sub>), and peak inductor charge and discharge current.

The MAX38890 implements a True Shutdown<sup>TM</sup> feature, disconnecting SYS from CAP as well as protecting against a SYS short if  $V_{CAP} > V_{SYS}$ .

Charging and backup can be disabled by keeping the ENC and ENB pins low, respectively. The backup system status can be monitored through two status outputs: the RDY flag that indicates when the supercapacitor is charged and the BKB flag that indicates when backup operation is occurring.

## **Application Circuits**

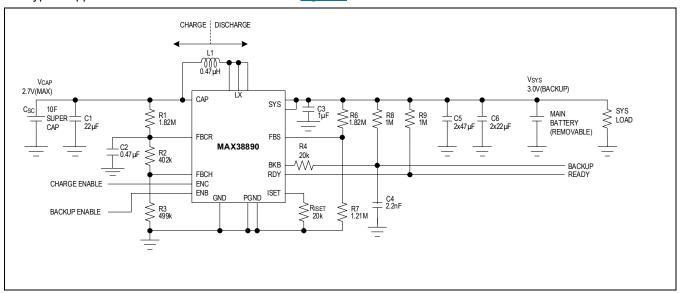

The typical application of the MAX38890 is shown in *Figure 1*.

Figure 1. Application Circuit

#### **Supercapacitor Voltage Configuration**

The maximum supercapacitor voltage ( $V_{CAP\_MAX}$ ) during charging is determined by the resistor-divider driving the FBCH pin. When  $V_{FBCH}$  reaches 0.5V, further charging of the supercapacitor is halted. The threshold has a 2.5% (12.5mV) hysteresis. To keep the ready power drawn low, keep the quiescent current in the resistor-divider low by setting the resistor from FBCH to GND to  $500k\Omega$ . The resistance from CAP to FBCH (R1 + R2) can then be determined by the standard equation:

$$R1 + R2 = R3 \times \left(\frac{V_{CAP\_MAX}}{0.5V} - 1\right)$$

Selecting  $V_{CAP\ MAX} = 2.7V$  and  $R3 = 499k\Omega$ :

$$R1 + R2 \approx 2.2M\Omega$$

The RDY pin is a flag that goes high when the supercapacitor has crossed a user-defined voltage. Like the FBCH input, the FBCR pin is driven from CAP through a resistor-divider. To save quiescent current, the FBCR and FBCH resistor-dividers can be combined using a three-resistor-divider string, as shown in <u>Figure 1</u>.

Total resistance from CAP to GND (R<sub>T</sub>) is:

$$R_T = R1 + R2 + R3 = 2.2M\Omega + 499k\Omega \approx 2.7M\Omega$$

RDY goes high when V<sub>FBCR</sub> is greater than 0.5V.

Assuming RDY to go high when V<sub>CAP</sub> reaches 1.5V:

$$V_{CAP\ RDY} = 1.5V$$

$$R3 = 499k\Omega$$

$$R2 = R_T \times \left(\frac{0.5V}{V_{CAP\ RDY}}\right) - R3 = 2.7M\Omega \times \left(\frac{0.5V}{1.5V}\right) - 499k\Omega = 401k\Omega$$

Selecting R2 =  $402k\Omega$ :

$R1 = R_T - R2 - R3 = 2.7M\Omega - 402k\Omega - 499k\Omega = 1.8M\Omega$

Select R2 =  $1.82M\Omega$  for fine-tuning on the bench.

During backup, the supercapacitor voltage discharges and the boost converter automatically adjusts its duty cycle to regulate V<sub>SYS</sub>. When V<sub>SYS</sub> drops below UVLO threshold (V<sub>UVLOF</sub>) or V<sub>FBCH</sub> drops to 10% of the FBCH threshold voltage (V<sub>TH\_FBCH</sub>), the boost regulator stops delivering load current and the supercapacitor voltage is preserved with only the current from the resistor-divider discharging the supercapacitor further.

#### **System Voltage Configuration**

The backup system voltage is determined by a resistor-divider driving the FBS pin. Set the system backup voltage using a resistor-divider from SYS to FBS to GND. When  $V_{FBS}$  is above 1.23V, the DC-DC regulator draws power from the main battery through the SYS pin to charge the supercapacitor to the maximum voltage set by FBCH and be ready for backup. The peak charging current can be programmed to up to 5A, max. When the main battery is removed and  $V_{FBS}$  drops to 1.2V, the DC-DC regulator draws power from the supercapacitor and regulates the SYS pin to the programmed backup voltage with the programmed peak inductor current, which is a maximum of 5A.

In order to reduce the current flowing through the resistor-divider, select high-value resistors.

To set system the backup voltage to 3.0V, select the bottom resistor (R7) to  $1.21M\Omega$ . The top resistor value can be calculated by the following equation:

$$R6 = \left(3.0 \times \frac{R7}{1.2}\right) - R7$$

$$R6 = \left(3.0 \times \frac{1.21M\Omega}{1.2}\right) - 1.21M\Omega = 1.815M\Omega$$

Select R6 =  $1.82M\Omega$  for fine-tuning on the bench.

#### **Charge/Discharge Current Configuration**

The MAX38890 current configuration pin, ISET, gives the user the ability to optimize the efficiency around the maximum load requirements of the system during backup. A larger current setting allows the supercapacitor to be discharged to a lower voltage for a given load during backup.

A single resistor sets both the charging and backup current.

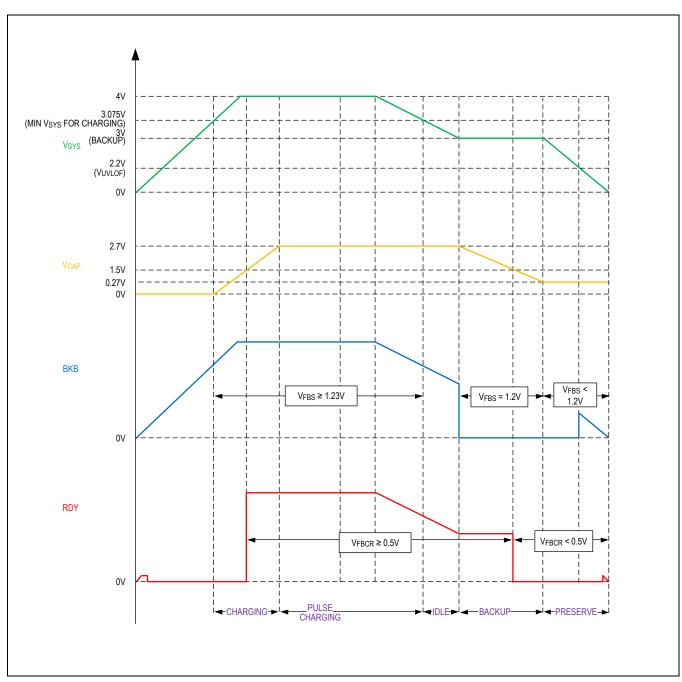

Figure 2. System Waveforms

#### Charging

Supercapacitor charging current and discharging current is determined by the same resistor, R<sub>ISET</sub>. The buck regulator operates in forced discontinuous conduction mode (DCM) until the supercapacitor gets fully charged.

Average charging current (I<sub>CAP CHG</sub>) is determined by:

$$I_{CAP\_CHG} = 2.5A \times \left(\frac{20k\Omega}{R_{ISET}}\right)$$

where  $R_{ISET}$  can be selected from  $100k\Omega$  to  $20k\Omega$ , and  $I_{CAP\_CHG}$  varies from 0.5A to 2.5A, respectively. Since charging current is efficiently drawn through a buck regulator, the average charging current from SYS ( $I_{SYS\_CHG}$ ) is:

$$I_{SYS\_CHG} = 2.5A \times \left(\frac{20k\Omega}{R_{ISET}}\right) \times \left(\frac{V_{CAP}}{V_{SYS}}\right) \times \left(\frac{1}{(charging\ efficiency)}\right)$$

Peak charging current (I<sub>LX</sub> CHG)

$$I_{LX\_CHG} = 5A \times \left(\frac{20k\Omega}{R_{ISFT}}\right)$$

When the supercapacitor voltage reaches its maximum voltage as determined by the FBCH threshold, the forced DCM of the charging stops. After this, only pulse charging takes place.

#### **Backup**

The peak inductor current limit during backup operation can be set by the same RISET resistor using the below equation:

$$I_{LX\_BU} = 5A \times \left(\frac{20k\Omega}{R_{ISET}}\right)$$

where  $R_{ISET}$  can be selected from  $100k\Omega$  to  $20k\Omega$ , and  $I_{LX}$  BU varies from 1A to 5A, respectively.

During backup operation, the MAX38890 regulator regulates the system voltage to the target backup voltage and as a result, the voltage on the supercapacitor reduces from the maximum charged voltage. For a given system load in backup ( $I_{SYS\_BU}$ ), the minimum supercapacitor voltage ( $V_{CAP\_MIN}$ ) needed to support the load can be calculated as:

$$V_{CAP\_MIN} = V_{SYS\_MIN} \times \left[ \frac{I_{SYS\_BU}}{I_{LX~BU} - (0.5 \times dl_{LX})} \right] \times \left( \frac{1}{backup~efficiency} \right)$$

For a system backup voltage of 3.0V and 1.5A system load, assuming the system backup is required until the minimum supercapacitor voltage of 1.5V and system efficiency of 75%.

Let us calculate the inductor current ripple based on on-time for a given minimum super capacitor voltage. From the on-time vs. supercapacitor voltage TOC, the voltage across inductor during on-time is given as below:

$$V_{L} = L \times \left[\frac{dILX}{Ton}\right] = Vcap$$

$$dILX = Vcap \times \left[\frac{Ton}{L}\right] = \frac{1.5 \times 480ns}{470nH} = 1.53A$$

The actual minimum supercapacitor voltage to backup 3V with 1.5A system load is calculated as below:

$$V_{CAP\_MIN} = 3V \times \left[ \frac{1.5A}{5A - (0.5 \times 1.53)} \right] \times \left( \frac{1}{75\%} \right) = 1.42V$$

For a system backup voltage of 5.0V and 0.5A system load, assuming the system backup is required until the minimum supercapacitor voltage of 1.0V and system efficiency of 75%.

The inductor ripple current is calculated as below:

$$dILX = Vcap \times \left[\frac{Ton}{L}\right] = \frac{1.0 \times 636ns}{470nH} = 1.35A$$

The actual minimum supercapacitor voltage to backup 5V with 0.5A system load is calculated as below:

$$V_{CAP\_MIN} = 5V \times \left[ \frac{0.5A}{5A - (0.5 \times 1.35)} \right] \times \left( \frac{1}{75\%} \right) = 0.77V$$

It is not recommended to operate the MAX38890 below the calculated  $V_{CAP\_MIN}$  for a given load. This causes the inductor peak current to hit the current limit which resets the regulator. Once the part is reset, the system supply needs to be reapplied to the SYS rail for the MAX38890 to restart and charge the storage element to its programmed threshold, after which backup operation can be resumed. Refer to the TOC for backup profile of 3V system backup voltage and 1.5A system load.

To avoid the regulator resetting, it is recommended either to reduce the load current before the supercapacitor voltage reaches the V<sub>CAP MIN</sub> level or the inductor peak current hits the set current limit.

# **Applications Information**

#### **Capacitor Selection**

Capacitors at the SYS and CAP pins reduce current peaks and increase efficiency. Ceramic capacitors are recommended because they have the lowest equivalent series resistance (ESR), smallest size, and lowest cost. Choose an acceptable dielectric such as X5R where the ambient temperature is less than +85°C or X7R where the ambient temperature is less than +125°C. Due to the ceramic capacitor's capacitance derating at higher DC bias voltages,  $2x47\mu F$  and  $2x22\mu F$  ceramic capacitors are recommended at the SYS side and a  $22\mu F$  ceramic capacitor at the CAP side for most applications. In addition, it is recommended to place a high-frequency filter capacitor of  $1\mu F$  across the SYS and PGND pins as mentioned in the *PCB Layout Guidelines*.

## **Supercapacitor Selection**

When the power source supplying the  $V_{SYS}$  voltage is removed, power to the output is provided by the MAX38890 operating in the backup or boost mode of operation using the supercapacitor as its source. In order to ensure that the supply voltage stays in regulation, the amount of power the supercapacitor can deliver at its minimal voltage should be greater than that required by the system. The MAX38890 presents a constant power load to the supercapacitor where smaller current is pulled out of the supercapacitor near its maximum  $V_{CAP}$  voltage. However, current drawn from the supercapacitor increases as it discharges to maintain constant power at the load. The amount of energy required in backup mode is the product of the constant backup power and time defined as backup time,  $T_{BACKLIP}$ .

The amount of energy available in the supercapacitor (C<sub>SC</sub>) is calculated using the following formula:

$$E = \frac{1}{2} \times C_{SC} \times (V^2_{CAPMAX} - V^2_{CAPMIN}) (J)$$

The amount of energy required to complete the backup equals to:

$$E = V_{\rm SYS} \times I_{\rm SYS} \times T_{\rm BACKUP}(J)$$

where ISYS is the system load during backup.

Since the energy required at the system side during the backup event comes from the available energy in the supercapacitor, assuming conversion efficiency  $\eta$  and the given  $T_{BACKUP}$ , the required  $C_{SCAP}$  is determined by the following equation:

$$C_{\text{SC}} = \frac{2 \times V_{\text{SYS}} \times I_{\text{SYS}} \times T_{\text{BACKUP}}}{[(V^{2}_{\text{CAPMAX}} - V^{2}_{\text{CAPMIN}}) \times \eta]} (F)$$

For example, in the <u>Figure 1</u> application circuit, assuming a 1.5A system load and an average efficiency of 75%, the minimum value of the supercapacitor required for a 5s backup time is:

$$C_{SC} = \frac{2 \times 3.0V \times 1.5A \times 5s}{[((2.7V)^2 - (1.5V)^2) \times 0.75]} = 12F$$

Figure 3. Charging/Discharging Waveforms

#### **Inductor Selection**

The recommended inductor value for the MAX38890 is 0.47µH.

#### **Status Flags**

The MAX38890 has two dedicated pins to report the device status to the host processor. Both of these output pins are open-drain type and require external pullup resistors. The recommended value for the pullup resistors is  $1M\Omega$ . The pins should be pulled up to the SYS rail.

#### **BKB Flag**

The BKB flag indicates that the converter is in backup mode, and it is low when the part is in backup mode, and  $V_{FBS}$  is regulating at 1.2V. This pin is high when  $V_{FBS}$  is above 1.23V. The BKB is high when  $V_{ENC}$  and  $V_{ENB}$  are both low.

#### **RDY Flag**

The RDY flag helps the external processor to detect that the supercapacitor is ready to back up the SYS voltage. The RDY flag is high when  $V_{FBCR} > 0.5V$  and low when  $V_{FBCR} < 0.5V$ . The RDY threshold can be set using the external resistor divider from the supercapacitor to GND.

#### **Enabling the Device**

The MAX38890 has dedicated enable pins for both charging and backup modes. Both of the pins can either be driven individually by a digital signal, pulled up, or strapped to the SYS rail.

#### **Charger Enable Input (ENC)**

Drive this pin high to enable charging of the supercapacitor while  $V_{SYS}$  is above the charging threshold. Drive it low to disable charging and reduce quiescent current. The ENC voltage applied should be more than 950mV.

#### Backup Enable Input (ENB)

Drive this pin high to enable system backup when  $V_{SYS}$  drops below the backup threshold. Drive it low to disable backup and reduce quiescent current. The ENB voltage applied should be more than 950mV.

#### **PCB Layout Guidelines**

Minimize trace lengths to reduce parasitic capacitance, inductance and resistance, and radiated noise. Keep the main power path from SYS, LX, CAP, and PGND as tight and short as possible. Minimize the surface area used for LX since this is the noisiest node. It is recommended to place a filter capacitor close to the part across the SYS and GND pins to minimize voltage spikes on account of trace inductance, as shown in *Figure 4*.

Figure 4. High-Frequency Filter Capacitor

The trace between the feedback resistor dividers should be as short as possible and should be isolated from the noisy power path. Refer to the EV kit layout for best practices.

The PCB layout is important for robust thermal design. The junction-to-ambient thermal resistance of the package greatly depends on the PCB type, layout, and pad connections. Using thick PCB copper and having a SYS, LX, CAP, and PGND copper pour enhances the thermal performance. The TQFN package has a large, exposed pad under the package, which creates an excellent thermal path to the PCB. This pad is electrically connected to the analog GND of the controller (AGND). Its PCB pad should have multiple thermal vias connecting the pad to the internal ground plane. The thermal vias should either be capped or have a small diameter in order to minimize solder wicking and voids.

### **Ordering Information**

| PART NUMBER   | TEMPERATURE RANGE | PIN-PACKAGE            | FEATURES                                       |

|---------------|-------------------|------------------------|------------------------------------------------|

| MAX38890AATE+ | -40°C to +125°C   | 3mm x 3mm, 16-pin TQFN | Enable input, selectable voltages and currents |

<sup>+</sup>Denotes a lead (Pb)-free/RoHS-compliant package.

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION              | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------|------------------|

| 0                  | 11/22            | Release for Market Intro | _                |